ESD介绍及TVS的原理和应用

见转自:https://blog.csdn.net/weixin_41796052/article/details/105125775

0 ESD简介

静电放电即ESD(Electro-Static discharge),是指具有不同静电电位的物体互相靠近或直接接触引起的电荷转移。

.1 静电积累

静电是两种介电系数不同的物质磨擦时,正负极性的电荷分别积累在两个特体上而形成。当两个物体接触时,其中一个趋从于另一个吸引电子,因而二者会形成不同的充电电位。有许多因素会影响电荷的积累,包括接触压力、摩擦系数和分离速度等。静电电荷会不断积累,直到造成电荷产生的作用停止、电荷被泄放或者达到足够的强度可以击穿周围物质为止。就人体而言,衣服与皮肤之间的磨擦发生的静电是人体带电的主要因之一。

.2 静电放电特性

静电放电产生的电磁场幅度很大(达几百伏/米)频谱极宽(从几十兆到几千兆),对电子产品造成干扰甚至损坏(电磁干扰)ESD引起的器件击穿,是电子工业最普遍,最严重的静电危害。

静电对电子产品损害的特点隐蔽性:人体不能直接感知静电,除非发生静电放电。人体也不一定能有电击的感觉,这是因为人体感知的静电放电电压为2~3KV,所以静电具有隐蔽性。

潜在性:有些电子元器件受到静电损伤后的性能没有明显的下降,但多次积累放电会给器件造成内伤而形成隐患。因此静电对器件的损伤具有潜在性。

随机性:电子元件什么情况下会遭受静电破坏呢?可以这么说,从一个元件产生以后,一直到它损坏以前,所有的过程都受到静电的威胁,而这些静电的产生也具有随机性,其损坏也具有随机性。

复杂性:静电放电损伤的实效分析工作,因电子产品的精,细,微小的结构特点而费时,费事,要求较高的技术并往往需要使用扫描电镜等高精密仪器。

.3 静电危害

引起电子设备的故障或误动作,造成电磁干扰.如:驱动电路程序被ESD打乱,出现花屏,白屏,声音不正常。

击穿集成电路和精密的电子元件,半导体元件或者促使元件老化,降低生产成品率。

高压静电放电造成电击,危及人身安全。

在易燃易爆品或粉尘、油雾的生产场所极易引起爆炸和火灾。

芯片损坏或击穿(高速端口、高阻输入端口、模拟端口等ESD电压较低)

1 ESD静电标准

一般ESD有三种类型:

第一个是人体模型,简称HBM,它模拟了在工厂环境中携带静电的人体触摸接地设备的过程,HBM的波形如绿线所示。值得一提的是HBM标准是为了衡量芯片,能否在生产、组装和运输的过程中免受ESD的损害,并非适用于日常使用的场景;

第二个是带电装置模型,简称CDM,它模拟了一个带静电的器件接触电路的情景,CDM的模拟波形如蓝线所示,CDM会在小于20ns的时间内有一个非常高的电流脉冲,和HBM相似CDM也是为了衡量芯片生产、制造过程中可能会遇到的ESD而设计的,并非适用于日常使用场景。

第三个是IEC 61000-4-2模型,这是一个为日常使用设计的标准,它可以帮助我们衡量芯片确保是否能在日常可能接触到的ESD中,免受损坏,如红色波形所示,它用了更高的电流脉冲 并且持续的时间也更长。

对于ESD有不同的等级,四级为最高级,一般在ESD芯片的手册里也会表明这些参数,下面截取了TI公司的TVS保护二极管:ESDS302, ESDS304手册的内容

2. ESD防护设计

电源加TVS管

特别是对于裸露在外的一些接口,比如USB、LVDS、网口、SD卡等,对这些接口进行接触放电时,静电很容易就会“串”到电源线上,静电由本来的共模变成了差模,此时电源上就会产生一个很高的尖峰,很多芯片都承受不了,发生死机,复位等问题。对于电源VCC的ESD保护,可以并接TVS管来解决。TVS管与稳压二极管很相似,都有一个额定的电压,不同的是它的响应速度特别快,对静电有很好的泄放作用。要注意的是布局布线的时候,TVS管要尽量靠近接口的位置,TVS的阴极以最近的路径接到接口的外壳地。

敏感器件电源添加LC滤波

有些IC特别容易受静电影响,进行ESD试验时,总是发生复位或者死掉。究其原因,一般都是电源引脚受到干扰。对此可以对其电源添加LC滤波。一般芯片的VDD管脚旁边都会有一个去耦电容,但是这个去耦电容是没有办法有效拦截静电的,甚至是几十uF的钽电容并接小电容,效果仍旧不佳。这时候,如果再串一个小电感,情况就得到很好的改观。静电放电会产生一个尖峰,同属于高频干扰,LC可以很好地将高频滤除,使通过电感之后的尖峰大大减弱,IC就不容易死机或者复位。

PCB铺地要求

PCB要尽可能多的铺地。如果是双面板,两面都要大面积铺铜,而且还要有足够的地过孔;如果是四层板或以上,主要元件层的临近平面层要设置成地层。比如四层板,如果主要元件在顶层,那么分层为:顶层->地层->电源层->底层;如果主要元件在底层,分层为:顶层->电源层->地层->底层。

3 TVS介绍

TVS,瞬态抑制二极管(TVS)又叫钳位型二极管,是目前国际上普遍使用的一种高效能电路保护器件,它的外型与普通二极管相同,但却能吸收高达数千瓦的浪涌功率,它的主要特点是在反向应用条件下,当承受一个高能量的大脉冲时,其工作阻抗立即降至极低的导通值,从而允许大电流通过,同时把电压钳制在预定水平,其响应时间仅为10-12毫秒,因此可有效地保护电子线路中的精密元器件。TVS允许的正向浪涌电流在TA=250C,T=10ms条件下,可达50~200A。双向TVS可在正反两个方向吸收瞬时大脉冲功率,并把电压钳制到预定水平, 双向TVS适用于交流电路,单向TVS一般用于直流电路。可用于防雷击、防过电压、抗干扰、吸收浪涌功率等,是一种理想的保护器件。耐受能力用瓦特(W)表示。

TVS管的非线性特性比压敏电阻好,当通过TVS管的过电流增大时,TVS管的钳位电压上升速度比压敏电阻慢,因此可以获得比压敏电阻更理想的残压输出。在很多需要精细保护的电子电路中,应用TVS管是比较好的选择。TVS管的通流容量在限压型浪涌保护器中是最小的,一般用于最末级的精细保护,因其通流量小,一般不用于交流电源线路的保护,直流电源的防雷电路使用TVS管时,一般还需要与压敏电阻等通流容量大的器件配合使用。 TVS管便于集成,很适合在单板上使用。

3.1 TVS的参数

TVS的伏安特性曲线,下图给出的是双向TVS管。如果是单向的,是反接在电路中,特性曲线的横向正半轴不是这样。

VBR:TVS二极管最小击穿电压。也就是在流过规定电流(IR )时,加于TVS两极的最小击穿电压;在25℃时,低于这个电压TVS是不会产生雪崩的。当TVS流过规定的1mA电流(IR )时,加于TVS两极的电压为其最小击穿电压VBR 。按TVS的VBR与标准值的离散程度,可把VBR分为5%和10%两种。为了满足IEC61000-4-2国际标准,TVS二极管必须达到可以处理最小8kV(接触)和15kV(空气)的ESD冲击,部份半导体厂商在自己的产品上使用了更高的抗冲击标准。对于某些有特殊要求的可携设备应用,设计者可以依需要挑选元件。

VRMW:正常工作时候可承受的电压。这个电压在实际应用当中应大于或等于被保护电路的正常工作电压。该电压值下对应的电流非常小,为nA级别,因此理解为:此电压表示电路正常工作时,TVS的电流非常小,也就是在电路中隐形,没有发挥作用,如果是理想状态下,该电压状态下的TVS电流应该为0。选型时,比如电路中的信号电压为3V,那么选择TVS管的Vrmw需要大于3V;如果选择Vrmw小于3V的TVS,那么在电路正常工作电压为3V时,就会有比较大的电流流进TVS,干扰电路正常工作;

IPP:最大峰值脉冲电流。处于反向状态时, 允许通过的最大脉冲峰值电流;

VC:钳位电压:当持续时间为20ms的脉冲峰值电流IPP流过TVS时,在其两端出现的最大峰值电压为VC。VC、IPP反映了TVS的突波抑制能力。 VC与VBR之比称为钳位因子,一般在1.2~1.4之间。 VC是二极管在截止状态提供的电压,也就是在ESD冲击状态时通过TVS的电压,它不能大于被保护回路的可承受极限电压,否则元件面临被损伤的危险。

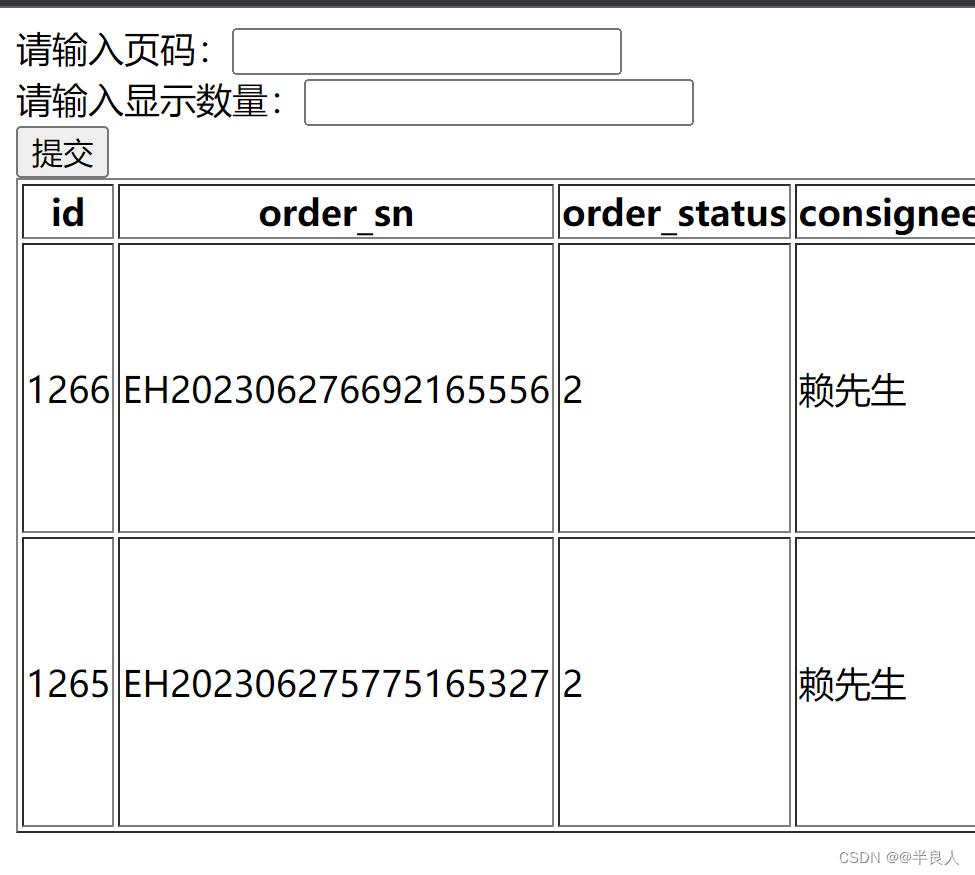

下面结合具体的datasheet来看:

该TVS的Vrwm为3.6V,主要看测试条件,是在电流为500nA的情况下;

VBR最小击穿电压为4.5-7.5V,测试条件是在1mA的情况下;

Vclamp(浪涌钳位电压)根据不同的电流测试条件下,有不同的电压值。

举例说明Vc:

(1)网上找到的测试图片

TVS 元件与压敏电阻在8kV IEC 61000-4-2 应力冲击测试下的输出波形对比。从图中可以看出,安森美半导体的TVS 元件可以迅速将ESD 应力降低,即从8 kV 静电电压钳位到5 至6 V 的水平;但压敏电阻的曲线则下降得很慢,而且无法降到很低的水平。该曲线表明,TVS 器件的恢复时间非常短,经过TVS 器件泄漏到后面电路的能量也非常少,特别适合于便携式设备的应用。而在多重应力条件下,两者的差别就表现得更为突出。由于TVS 采用二极管工作原理,受到电击后,会立即击穿,然后关闭,对器件没有损伤,因此可以说没有寿命限制。对于压敏电阻而言,它采用的是物理吸收原理,每经过一次ESD 事件,材料就会受到一定的物理损伤,形成无法恢复的漏电通道;而且,要达到更好的吸收效果,就要使用更多的材料,使其体积增加,进而限制了在今天小型化产品当中的应用。

(2)TI公司的芯片

这是官方手册给出的浪涌电流、钳位电压以及功率的波形图,测试标准没有具体理解,8/20us代表的浪涌时间(不明白的地方是给进来的浪涌电流和电压分别为?)。根据横纵坐标可以看到电流最大达到了12A左右,最大的电压为6V左右,之后就一直下降为0(是否可以理解浪涌结束?),这两个参数与钳位电压Vclamp给出的参数基本保持一致。

疑问:假如这个测试条件是给了一个电压很高的瞬间浪涌,那么TVS可以把电压直接降到一个比较低的水平,用来保护后续电路?

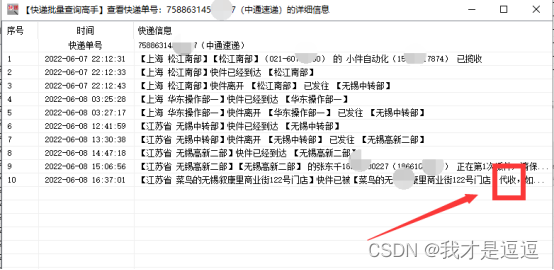

(3)钳位波形

红色表示没有加入ESD保护器件,电压会有一个很高的浪涌;

蓝色表示加入了ESD保护二极管,会被钳位到 比较低的水平。

3.2 TLP曲线(传输线性脉冲曲线)

所谓的TLP 测试,就是一种利用矩形短脉(50~200 ns)来测量ESD 保护元件的电流-电压特性曲线的方法。这个短脉冲用来模拟作用于保护元件的短ESD 脉冲,而恒定阻抗的传输线路可以生成恒定幅度的方波。下图为TLP 测试的结构示意图:

TLP 测试通过方波测试脉冲加到待测器件(DUT)的两个引脚之间进行测试。TLP 测试前要先对电路中的传输线路充电,测试时将被测器件接入,传输线路通过被测器件放电。改变电路和输入电压和传输线路的长度可以模拟不同能量的ESD 脉冲,从而得到器件的ESD 大电流抑制能力。TLP 测试先从小电压脉冲开始,随后连续增加直到获得足够多的数据点,以作出完整的I-V 曲线。通常测试脉冲的幅度会加大到使DUT 彻底损伤为止,作而获得其精确的允许最大脉冲电流。

可以通过TLP曲线观察钳位电压:

举个例子当1A的电流被释放到ESD二极管,它的钳位电压大约为8.4V;当放电电流为2.7A,钳位电压为9V ;当放电电流为5.8A时 ,钳位电压为10V 。(这里可以对应上面的用不同的测试条件,来获得完整的TLP曲线)

系统会承受的钳位电压对于8000V的IEC ESD冲击而言,我们只需要看TLP曲线中16A的那一点 。对于这一个二极管而言,钳位电压大约是13.4V。TLP曲线的斜率对于理解二极管保护的好坏很重要。

绿色的曲线代表另一颗ESD保护二极管。更高的斜率代表它在对应电流时有更低的钳位电压。根据欧姆定律这条曲线的斜率为动态电阻1/Rdyn。所以 当你关注钳位电压时,选择动态电阻更小的ESD保护二极管,就代表它拥有更小的钳位电压 。

下面是TI的一款TVS芯片的TLP曲线,有一个婉转的曲线,不太明白。

3.3 寄生电容CL

在芯片的手册中命名为:Line capacitance(I/O对地或者I/O对I/O)

电容器量CL是由TVS雪崩结截面决定的,是在特定的1MHz频率下测得的。CL的大小与TVS的电流承受能力成正比,C太大将使讯号衰减,如下图。因此,CL是数据介面电路选用TVS的重要参数。电容器对于数据/讯号频率越高的回路,二极管的电容器对电路的干扰越大,形成噪音或衰减讯号强度,因此需要根据回路的特性来决定所选元件的电容器范围。高频回路一般选择电容器应尽量小(如LCTVS、低电容器TVS,电容器不大于3pF),而对电容器要求不高的回路电容器选择可高于40pF。

那么,选择ESD二极管时应该选择哪种电容?不幸的是,由于每种设计都有自己的电容预算,因此不存在适合每种接口的最大ESD电容要求。但是这张表给出的几种常用接口的一般电容和ESD选型的建议。

4 TVS选型

计算接口信号幅值的范围来确定ESD保护产品的工作电压;

根据信号类型决定使用单向或是双向的ESD保护产品;

根据信号速率决定该接口最大可接受ESD保护产品的电容;

根据电路系统最大可承受电压冲击,在TLP中寻找对应的钳位电压;

确保ESD保护产品可达到或超过IEC 61000-4-2 Level 4,8KV接触放电和15KV空气放电;

以USB 2.0为例

第一步是确认接口的电压范围,对USB2.0而言,Vbus 可能达到5伏,所以我们可以确定的是,需要选取的ESD保护二极管的,工作电压需要达到5伏或略微高于5伏 。正常工作中 D+和D-负责传输差分信号,幅值范围在0到3.6伏之间 ,所以我会选择工作电压在3.6伏,或者更高的ESD保护二极管。

接下来 我们需要确定ESD二极管的极性配置,在我们希望的应用中 ,因为Vbus和D+ D-都是大于等于零的正向信号 ,所以单向和双向的二极管都是有的,选择单向二极管有助于提供更好的提供负压保护。而选择双向二极管,可以提供更灵活的设计空间,因为pin脚可以自定义接地 。

接下来,我们需要确定ESD二极管,应该具有的电容,因为Vbus线路是直流电信号,电容对信号无影响 。但对于D+和D-而言,在高速USB中,信号速率可以达到480兆,所以我们需要考虑对电容的影响 。虽然最大的ESD电容还取决于,整个系统的电容总预算 ,但一般而言 我们推荐该接口的电容小于2.5pF ,如果系统中其器件具有更高的电容值 ,那么此处可能需要选择更小电容的二极管。

接下来 我们看看保护系统所需的钳位电压 ,在这种情况下,我们需要考虑USB switch和Battery Charger能承受的最大电压冲击 ,我们假设battery charger在TLP脉冲20伏时,会发生故障 USB。switch在TLP16脉冲16伏时会发生故障,这意味着为了保护battery charger ,顺利通过8000伏的IEC ESD冲击,ESD二极管必须在16安,TLP又小于20伏的钳位电压。同理 为了保护USB switch,ESD二极管必须在16安TLP时 ,有小于16伏的钳位电压。

4 手机ESD防护

手机电路中需要进行ESD防护的部位有:SIM 卡插座与CPU 读卡电路、键盘电路、耳机、麦克风电路、电源接口、数据接口、USB 接口、彩屏LCD 驱动接口。

4.1 壳体的设计

尽量增加壳体的厚离,即增加外壳到电路板之间的距离,或者通过一些等效方法增加壳体气隙的距离,这样可以避免或者大大减少ESD 的能量强度。通过结构的改进,可以增大外壳到内部电路之间气隙的距离从而使 ESD 的能量大大减弱。根据试验,8kV 的ESD 在通过过4mm 的距离后能量一般衰减为零。

可以用 EMI 油漆喷涂在壳体的内侧。EMI 油漆是导电的,可以看成是一个金属的屏蔽层,这样可以将静电导在壳体上;再将壳体与PCB(Printed Circuit Board)的地连接,将静电从地导走。这样处理的方法除了可以防止静电,还能有效抑制EMI 的干扰。如果有足够的空间,还可以用一个金属屏蔽罩将其中的电路保护起来,金属屏蔽罩再连接PCB 的GND。用金属屏蔽罩将 LCD 模块保护起来的例子。

4.2 手机PCB设计

因为手机通常是多层板,有高频信号,在设计时布局、布线有很多需要注意的地方。

4.3 电路设计

在壳体和 PCB 的设计中,对ESD 问题加以注意之后,ESD 还会不可避免地进入到手机电路中,尤其是以下几个部件:SIM 卡的CPU 读卡电路、键盘电路、耳机、麦克风电路、数据接口、电源接口、USB 接口、彩屏LCD 驱动接口,这些部位很可能将人体的静电引入手机中。所以,需要在这些部分中使用ESD 防护器件。

5 总结

总之,静电的防护是一个系统工程,从静电的产生、静电的积累、静电的释放、静电释放的路径的选择和释放静电的量的控制全方位考虑,但是因为静电破坏的复杂性,至今还没有一个很好的方法去完全解决静电问题。但是这也不代表我们对静电问题束手无策,在静电保护的过程中,我们只要遵循一个原则:静电的积累必然有静电的释放,所以我们只要给静电选好放电的路径和放电的去处即放电地,就能很好的进行静电的释放。

————————————————

版权声明:本文为CSDN博主「leon.geng」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/weixin_41796052/article/details/105125775