目录

前言

4.3.1 编码器和译码器

一、编码器

1、普通编码器

2、优先编码器

二、译码器

1、二进制译码器

2、二-十进制译码器

3、显示译码器

4.3.2 数据选择器和数据分配器

一、数据选择器

1、工作原理

2、用数据选择器设计组合逻辑电路

二、数据分配器

1、工作原理

4.3.4 加法器

一、一位加法器

1.半加器

2.全加器

二、多位加法器

1.串行进位加法器

2.超前进位加法器

三、用加法器设计组合逻辑电路

1.74LS283设计一个将8421BCD码转换成余3码

2.用74LS283设计一个4位二进制并行加/减法器

4.3.5 数值比较器

4.3.6 奇偶发生/校验器

前言

《数字电子技术基础》第4.3节学习笔记

《数字逻辑电路设计》第6.1节学习笔记

将常用的组合逻辑电路制成了中小规模集成的标准化集成电路产品,在设计大规模集成电路时常常调用已有的模块电路,作为所设计电路的组成部分。

该博客会继续更新

4.3.1 编码器和译码器

一、编码器

将每个数据表现方式用一个二进制码来表示,有主要分为普通和优先编码器。

编码信号的不同,可分为二进制编码器和二-十进制编码器(十进制-BCD码编码器)。

1、普通编码器

在编码器中,任何时刻只允许输出一个编码信号,否则输出将发生混乱。8-3线二进制编码器:

由于只要有一条线导通即导通,属于或门,化简上式得到

从上式也可以得到3位编码器的电路图

2、优先编码器

允许同时输入两个以上的编码信号。不过在设计优先编码器时已经将所有输入信号按照优先级排了对,当输入信号同时输入时,只对优先级最高的位进行编码。

具有代表性的时74HC148(74LS148)优先编码器。

由以上逻辑式可以看出,其中添加了控制端s' ,只有在s' = 0时才正常功能使用;为1时输出端封锁为高电平。

在优先编码器电路中,除了二进制编码器以外,还有一类位二-十进制优先编码器,将10个输入信号分别编成10个BCD码,第9位为最高位;第0位为最低位。

- 【例4.3.1】使用两片74HC148设计一个16-4线编码器,实现中断优先级控制,设置输入端15为优先级最高,0为优先级最低。输出为16中4位二进制代码。

解:由于每一个编码器有8路输入,所以需要并列使用,设置高8位与低8位。按照高位输入时地位无线控制,可以通过高8位的YS'端控制低8位的S'使能端。这样就实现了在高位没有输入时低位才有效。

二、译码器

译码器最为编码器的反向操作,就是将二进制代码转换成其他相应代码。常用的译码器电路有二进制译码器、二-十进制译码器和显示译码器三类。

1、二进制译码器

3-8线译码器与编码器功能相反

二极管与门阵列构成:

74HC138(74LS138)使用CMOS门电路实现

由于门电路中会强调“低电平有效”因此在门电路上加圈表示反相器,即实现了非的功能。

74HC138也称为最小项译码器,由于其附加了控制端S1、S2'、S3'。当S1、S2'+S3'=0时,Gs输出为高电平,译码器处于工作状态,否则禁止输出。控制端可以称为“片选”输入端,可以进行多片的扩展。

如两片74HC138组成4线-16输出译码器,可以看出D3控制左边片的输入使能。

2、二-十进制译码器

由于其是4-10线的,输入为4位,应有16个数对应,故出现了伪码。

3、显示译码器

灭灯输入/灭零输出BI'/RBO':

4.3.2 数据选择器和数据分配器

又成多路选择器和多路分配器,是数字系统中的基本功能是从输入端提供的多路数据中选择一路在公共传输线(如计算机总线)上传输,到接受段后再将该数据分配给多路输出中的某一路,从而实现多路数据在公共总线上的分时传送。实现数据的并-串转换、序列信号产生及任意组合逻辑函数等逻辑功能。

一、数据选择器

1、工作原理

数据选择器在多路数据传送过程中能够根据需要将其任意一路选出来的电路叫做数据选择器,也称多路选择器(Data Selector)或多路开关(Multiplexer,MUX)。多路数据的选择是受控制信号控制的,一般称为地址选择信号。通常对于一个具有路输入和1路输出的MUX有n个地址选择端。

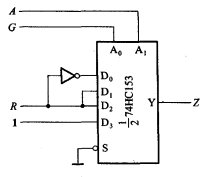

以双4选1数据选择器74HC153为例,进行工作原理的说明:

由图可见, 为公共输入段;

为相互独立的输出段;

为输出的控制输入段。

上图已经时数据选择器的数据流图,由于A0=0所以TG1和TG3传输门导通,二TG2和TG4截止,当A1=0时TG5导通,TG6截止,当

时Y1 = D10。同理可以推到其他的三种情况。

同时, 时,数据选择器工作,反之为1时数据选择器禁止工作,输出被封锁为低电平。

下表为74HC153其中Y1路输出的真值表,可以类似得到Y2作为输出的真值表。

| 选择输入 | 数据输入 | 使能输入 | 输出 | ||||

| A0 | A1 | D10 | D11 | D12 | D13 | Y1 | |

| x | x | x | x | x | x | 1 | 0 |

| 0 | 0 | D10 | X | X | X | 0 | D10 |

| 1 | 0 | X | D11 | X | X | 0 | D11 |

| 0 | 1 | X | X | D12 | X | 0 | D12 |

| 1 | 1 | X | X | X | D13 | 0 | D13 |

其输出逻辑式可以写成:

类似的可以写出路选择器的输出表达式:

式中,为控制变量A...组成的最小项,

为输入的第i路输入。

常见的MSI多路选择器有双4选1数据选择器74LS153(集成块中含有两个4选1数据选择器,这与74HC153类似)和8选1数据选择器74LS151等。

2、用数据选择器设计组合逻辑电路

- 两个带附加控制段的4选1数据选择器组成一个8选1数据选择器

8选1必须要3位地址输入端,所以只能借助控制端,只需要控制端对前4个或者后4个进行区分即可,即当4个输入端输入时后4个输入端截止,同时将2个输出端或输出即可。

上图逻辑表达式可以写成:

- 实现交通信号灯监视电路

(1)分析输出输出

将R/A/G作为三个输入变量,灯亮时为1,不亮时为0。将Z作为提醒信号进行输出。当Z为1时发生故障提醒,为0时未发生故障。

(2)逻辑真值表如下

| 输入 | 输出 | ||

| R | A | G | Z |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

(3)根据真值表写出逻辑表达式

(4)变化形式

(5)分配管脚

(6)根据管脚设计电路

- 将4位8421BCD码分时传送至七段显示译码器,然后动态显示相应的LED显示器。

| 真值表 | ||||||||||

| 输入 | 2-4译码器 | 七段译码器 | 数码管 | |||||||

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 个位(1) |

| 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 十位(5) |

| 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 百位(0) |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 千位(8) |

地址 按00——>01——>10——>11周期变化式,只要地址变化的频率大于25次/s,人眼就可以清楚的看到显示8051,且无明显闪烁感。

二、数据分配器

1、工作原理

数据分配器简称DEMUC,其结构和功能正好与数据选择器相反。

真值表

| 输入 | 选择输入 | 数据输出 | ||||

| D | A0 | A1 | D10 | D11 | D12 | D13 |

| D | ||||||

| 0 | 0 | D | X | X | X | |

| 1 | 0 | X | D | X | X | |

| 0 | 1 | X | X | D | X | |

| 1 | 1 | X | X | X | D | |

由真值表可以看出,当出入D=1时,就变成了2-4译码器。

4.3.4 加法器

一、一位加法器

1.半加器

不考虑低位的进位将两个1位二进制数相加,称为半加。实现电路为半加器。

S表示AB相加的和(不包括进位),CO为AB相加的进位。

2.全加器

在两个数相加时,需要考虑来自地位的进位,故相当于三个数相加,CI为低位进位。

二、多位加法器

1.串行进位加法器

在使用时及全加器的串联,低位全加器的进位为高位全加器的进位,称为串行进位加法器(或者称为行波进位加法器)。

每一位的相加结果必须等到下一位的进位才能确定,因此运算速度慢

2.超前进位加法器

每一位的相加的进位都可以使用逻辑表达式表达式进行计算,不需要再等待低位的进位,这样就可以有效的提高运算速度,称为超前进位(Carry Look-ahead)加法器,也成为快速进位(Fast Carry)加法器。

第i位的进位可以表示成:![]()

由上式可以得出4位超前加法器74LS283。

由上述逻辑式和电路图可以得出第一级输出的逻辑表达式

由此看出其节省时间是通过增加电路的复杂度来换取的,当加法器位数增加时,电路的负责度也随之上升。

三、用加法器设计组合逻辑电路

1.74LS283设计一个将8421BCD码转换成余3码

余三码与8421BCD码相差3,即8431BCD码加上0011即可得到余三码。

2.用74LS283设计一个4位二进制并行加/减法器

对于加法与减法通过外加一个功能选择端M,当M=0实现加法器;当M=1实现减法器。

补充二进制的补码:最高位符号位不变

正数的补码为它本身,负数的补码=数值逐位求反+1。

因此在M=1时,求其减数的补码+1就可以,这里取反可以通过与1的异或来求取,+1可以通过74LS283的进位置1来得到,因此其实现电路为: