原文链接:http://blog.csdn.net/njuitjf/article/details/17096517

非常好的资料关于两片DDR级联组成32bit系统,平时工作中也经常遇到,跟大家分享一下:

DDR3中bank, 16bit和32bit等概念

最近在看内存相关的东东。

以前认为内存就是块资源,需要的时候,malloc出来一部分使用即可。对内部的东东没有深入了解过。

刚开始看起来,感觉有点丈二和尚。

通过各种查询,并请教牛人,对基本概念有了个初步了解,先总结一把。

先说说bank。

看到bank首先想到了银行,然后是利率,然后是房贷...

扯远了,这儿的bank是存储库的意思。

也就是说,一块内存内部划分出了多个存储库,访问的时候指定存储库编号,就可以访问指定的存储库。

具体内存中划分了多少个bank,要看地址线中有几位BA地址,如果有两位,说明有4个bank,如果有3位,说明有8个bank.

DDR3的地址中有三个BA,即三个Bank Address,BA0, BA1, BA2。所以DDR3单块内存中都是8个bank.

存储库里面的内存是怎么组织的呢?

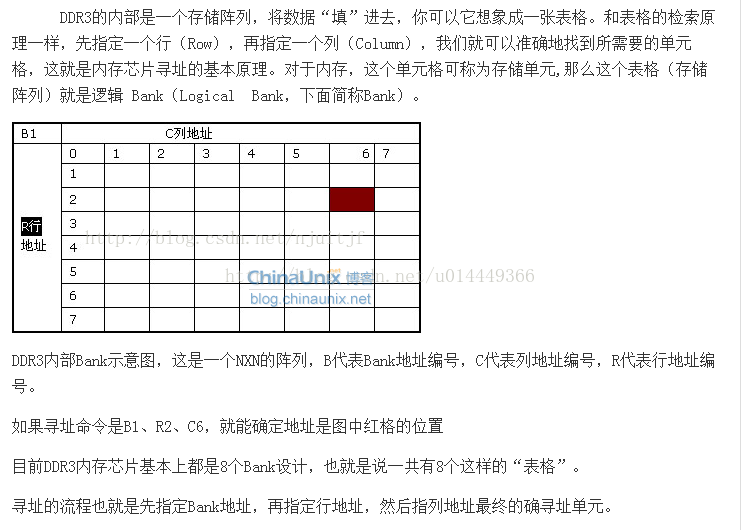

存储库里面类似于一个矩阵。

有很多点,没一个点就是一个cell,也就是一个存储点,有一个电容和一个晶体管组成,通过上电与否,来表示1或0.

每一个cell由一个行号和一个列号来唯一标识。

也可以这么理解,bank中分成了很多行(row),每一行又有很多列。

这样的话,给定bank编号,可以找到bank,给定row编号,可以找到所在行,给定 column 编号,可以找到所在列,也就找到了要访问的cell。

一个bank中有多少行,多少列呢?

这要看行和列分别有多少位来表示。

假如表示行的有A0~A14,那么单个bank中行的总量为2^15。

列类似,如果表示列的有A0~A9,单个bank中列总量为2^10.

下面来看看16bit/32bit内存的概念。

这儿所说的16bit/32bit,指的是内存中以多长为单位进行存储。

16bit,即是说内存中是以16bit为单位访问内存的,也就是说,你给内存一个地址,内存会给你一个16bit的数据到数据线。

32bit的与此类似。

下面来看一个具体例子。

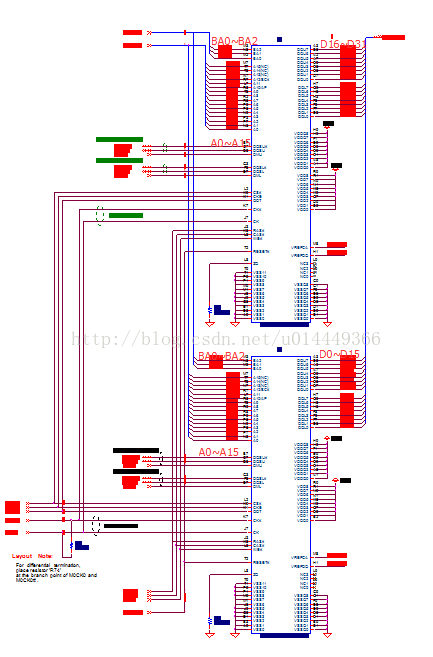

该例子中,用两个16bit的DDR3内存拼成了一个32bit的DDR3.

每块16bit DDR3的大小为512M Bytes.

看看硬件上连接,我们这儿只关心地址线和数据线,CS, CK, CKE, CAS, RAS等暂时不考虑。

第一片16bit DDR3的BA0, BA1, BA2连接到了CPU的BA0, BA1, BA2。

第二片16bit DDR3的BA0, BA1, BA2也连接到了CPU的BA0, BA1, BA2。

第一片16bit DDR3的A0~A14连接到了CPU的A0~A14。

第二片16bit DDR3的A0~A14连接到了CPU的A0~A14。

第一片16bit DDR3的D0~D15连接到了CPU的D0~D15。

第二片16bit DDR3的D0~D15连接到了CPU的D16~D31。

分析下该实例。

bank address有三个bit,所以单个16bit DDR3内部有8个bank.

表示行的有A0~A14,共15个bit,说明一个bank中有2^15个行。

表示列的有A0~A9,共10个bit,说明一个bank中有2^10个行。

来看看单块16bit DDR3容量:

2^3*2^15*2^10=2^28=256M

我们的内存是512M,到这儿怎么变成256M了?被骗了?

呵呵,当然没有。

忘了我们前面一直提到的16bit。

16bit是2个byte对吧。

访问一个地址,内存认为是访问16bit的数据,也就是两个字节的数据。

256M个地址,也就是对应512M的数据了。

真相大白。卖内存的没骗俺。

再来看看两个16bit是如何组成一个32bit的。

有一个概念一定要清楚,这儿所说的两个16bit组成一个32bit,指的是数据,与地址没有关系。

我开始这一块没搞清楚,一直认为是两个16bit的地址组成了一个32bit的地址。然后高位地址,地位地址,七七八八。。。

之后没一点头绪。

将16bit/32bit指的是数据宽度之后,就非常明了了。

每一块16bit DDR3中有8个bank,2^15个row,2^10个column。也就是有256M个地址。

看前面的连线可知,两块16bit DDR3的BA0~BA2和D0~D14其实是并行连接到CPU。

也就是说,CPU其实认为只有一块内存,访问的时候按照BA0~BA2和D0~D14给出地址。

两块16bit DDR3都收到了该地址。

它们是怎么响应的呢?

两块内存都是16bit,它们收到地址之后,给出的反应是要么将给定地址上2个字节送到数据线上,要么是将数据线上的两个字节写入到指定的地址。

再看数据线的连接,第一片的D0~D15连接到了CPU的D0~D15,第二片的D0~D15连接到了CPU的D16~D31。

CPU认为自己访问的是一块32bit的内存,所以CPU每给出一个地址,将访问4个字节的数据,读取/写入。

这4字节数据对应到CPU的D0~D31,又分别被连接到两片内存的D0~D15,这样一个32bit就被拆成了两个16bit.

反过来,也就是两个16bit组成了一个32bit.

CPU访问的内存地址有256M个,每访问一个地址,将访问4个字节,这样CPU能访问的内存即为1G.

DDR内部存储模型如下:

图来之:http://www.360doc.com/content/14/0116/16/15528092_345730642.shtml

自己也配上一张实际电路图,方便理解:

图中上面的是两片DDR级联电路:

1、两片DDR的地址线:A0~A15都接一起,然后接到CPU

2、两片DDR的bank选择线:BA0~BA2也都接一起,然后接到CPU

3、上面一片的DDR数据线接到CPU数据线的D15~D31,下面一片DDR的数据线接CPU数据线的D0~D15

4、这样CPU就认为自己访问的是32bit的内存,数据在储存时高16位在上面内片中,低16位在下面的DDR中,但是又不影响使用,管他怎么存呢,存可就行。

5、这里要纠正一点:你要是土豪的话,地址线也用32根,那根本就不用这么折腾,程序不用这么麻烦,但是成本就高了,现在明白了吧,只要够便宜,麻烦一点根不就不是事!!!