学习了一段时间后,决定开始一点点更新PCIe这一系列,虽然学习了一段时间,有些地方可能总结的不好或者有纰漏,还请大家不吝指教,先行谢过!

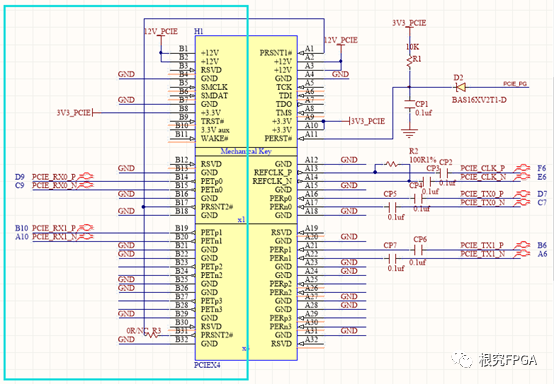

还需声明的是,接下来所有的设计硬件的照片,是一款xc7z030ffg676-2的ZYNQ开发板,功能很强大。

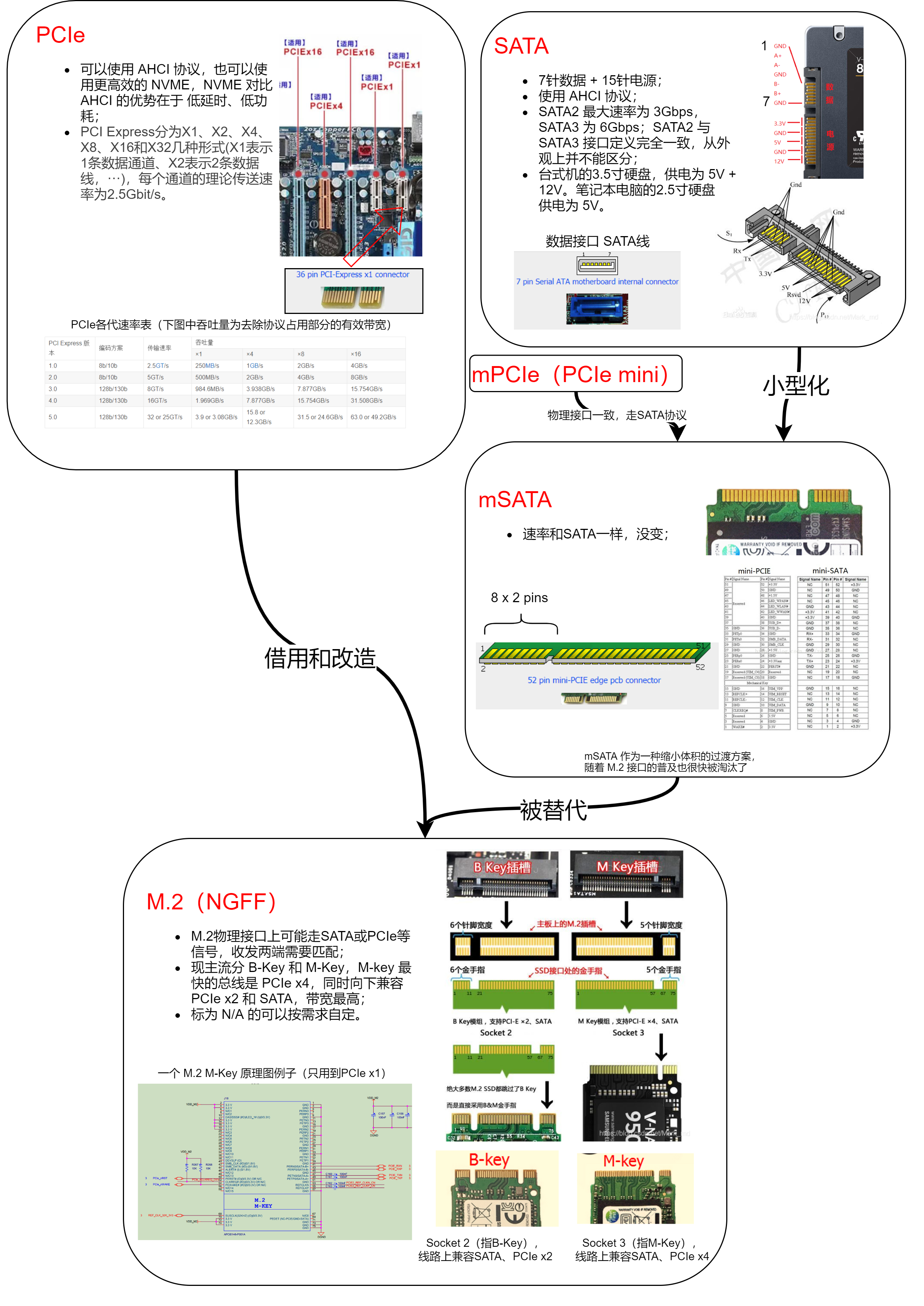

PCIe的传输速度与链路宽度

PCIe2.0规范于2007年1月5日推出,将PCIe1.0 2.5GT/s的传输速率提高了一倍,每个通道的吞吐率从250MB/s上升到500MB/s,因此2通道的PCIe可支持高达1GB的总吞吐量。

PCIe吞吐量计算方法

吞吐量=传输速率*编码方案

以PCIe2.0x2为例,该系列为2.0版本的PCIe,包含两个物理信道Lane,每个通道的吞吐量为:

5GT/s x 8/10 =4.0Gb/s =4000 Mb/s =500MB/s

所以PCIe2.0x2的吞吐量为:500MB/s x 2 = 1GB/s

分析:

PCIe2.0协议传输速率为5.0GT/s,这样的描述主要说明的是每条PCIe Gen2的lane(SERDES)每秒可以完成5.0Gbit数据传输的特性,即每一条链路上支持每秒5G次传输,每个Lane上传输5Gbit,但是由于PCIe2.0采用的是8b/10b编码方案,多出的2bit并不是对上层有意义的信息。

那么PCIe2.0协议的每一条lane支持5 * 8/10 /8=500MB/s的速率。

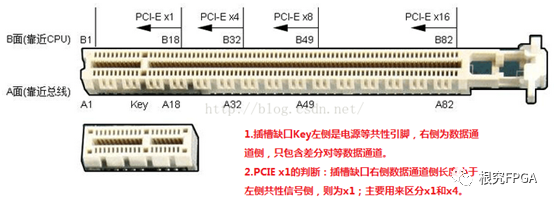

PCIe链路的电气接口

PCIe2.0x2接口相对于其他系列,包含两对发送与接收接口:

数据部分包含双向8个接口,而不是8个双向接口:

PETp0与PETn0:发送器差分线对,通道0

PETp1与PETn1:发送器差分线对,通道1

PERp0与PERn0:接收器差分线对,通道0

PERp1与PERn1:接收器差分线对,通道1

故链路宽度为2

A面:

手机视角:

PCB视角:

B面:

手机视角:

PCB视角:

PCIe的其他辅助电气接口

1、Vcc与Vaux(由处理器系统提供)

PCIe设备使用两种电源Vcc和Vaux,额定电压都为3.3V,其中Vcc为主电源,PCIe设备使用的主要逻辑模块由Vcc进行供电,而一些与电源管理相关的寄存器使用使用Vaux进行供电。

在PCIe设备中,一些特殊的寄存器通常使用Vaux进行供电,因为这样的话即使设备的Vcc被移除,这些与电源管理有关的逻辑状态和特殊寄存器的内容也不会丢失。这样可以大大的缩短系统恢复时间和降低系统功耗,因为Vaux在大多数情况下并不会被移除,这样当Vcc恢复后,设备不必恢复使用Vaux供电的逻辑,从而设备可以很快的恢复到正常工作状态。(具体应用在热插拔篇会讲)

2、PERST#(#:低电平有效)

该信号为全局复位信号,由处理器系统提供,处理器系统需要为PCIe插槽和PCIe设备提供该信号,PCIe设备使用该信号复位内部逻辑,当该信号有效时,PCIe设备将对内部逻辑进行复位操作,其中Cold Reset和Warm Reset这两种复位方式与该信号有关。

3、REFCLK+和REFCLK-信号

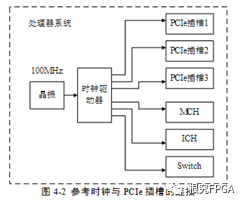

在一个处理器系统中,通常采用专用逻辑向PCIe插槽提供REFCLK+和REFCLK-信号,如下图所示,其中100Mhz的时钟源由晶振提供,并经过一个“一推多”的差分时钟驱动器生成多个同相位的时钟源,与PCIe插槽一一对应连接。

PCIe插槽参考时钟其频率范围为100Mhz±300ppm,处理器系统需要为每一个PCIe插槽 、MCH、ICH和Switch提供参考时钟。

当PCIe设备作为Add-in卡连接在PCIe插槽时,可以直接使用PCIe插槽提供的REFCLK+和REFCLK-信号,也可以使用独立的参考时钟,只要这个独立的参考时钟满足100Mhz±300ppm的要求即可。

4、WAKE#

当PCIe设备进入休眠状态,主电源已经停止供电时,PCIe设备使用该信号向处理器系统提供唤醒请求,使处理器系统为该PCIe设备提供主电源Vcc。

在PCIe总线中,该信号是可选的,因此使用WAKE#信号唤醒PCIe设备机制也是可选的,此外,使用该机制时,必须使用Vaux进行供电。

WAKE#是一个Open Drain信号,一个处理器的所有PCIe设备可以将WAKE#进行“线与”后,统一发送给处理器的电源控制器。当某个PCIe设备需要唤醒时,该设备先将WAKE#信号拉低,经过一段时间后,系统处理器开始为该设备提供主电源Vcc,并使用PERST#对该设备进行复位操作,再次过程中WAKE#信号需要保持为低电平,当主电源Vcc上电完成之后,PERST#也将置为无效并结束复位,WAKE#信号也随之被置为无效(拉高)。

5、SMCLK和SMDAT

SMCLK与SMDAT信号与SMBUS(System Management Bus,系统管理总线)有关,类似于IIC总线,因为SMBus源自于IIC总线。SMbus总线的最高频率为100Khz,SMBus上的从设备具有超时功能,当SMBus总线上的从设备发现主设备发出的时钟信号保持低电平超过35ms时,将引发从设备的超时复位,当设备需要复位从设备时,可以采用这种超时机制。

SMBus还支持Alert Response机制,当从设备产生一个中断时,并不会立即清除该中断,直到主设备向0b0001100地址发送指令。

6、JTAG信号

Joint Test Action Group,联合测试行为组 PRSNT1#和PRSNT2# PRSNT1#与PRSNT2#与PCIe设备的热插拔有关,在PCIe的Add-In卡中PRSNT1#与PRSNT2#直接相连。

在处理器主板中,PRSNT1#直接接地,PRSNT2#通过一个上拉电阻接为高电平。

当Add-In卡为插入时,PRSNT2#信号由上拉电阻接为高,Add-In卡插入后,主板的PRSNT2#与PRSNT1#接通,此时PRSNT2#信号为低,处理器主板的热插拔控制逻辑捕获这个低电平,得知Add-In卡已经插入,从而触发系统复位软件进行相应处理。当Add-In卡拔出时,PRSNT2#信号变为高,处理器主板捕获这个高电平,得知Add-In卡已经拔出,从而触发系统软件进行相应处理。

转自:

https://mp.weixin.qq.com/s?__biz=MzA5NjI1NDk0NQ==&mid=2247484417&idx=1&sn=b8aa67ce9048fbe0bc9186728eb58144&chksm=90b3aa8fa7c42399f426fba066fe8d9c44cacfa049d972345b166c9db8d851771d8b71770305&scene=178&cur_album_id=1462562427954216964#rd