在CPU领域里的竞争,AMD与Intel从来就没有停止过,AMD也并没有如几年前人们所料想的那样被Intel压着打,反而步步紧逼Intel做出了种种不得以的决策。从AMD第一块CPU芯片开始,就已经发动了对Intel的猛烈进攻。

Athlon已不仅是一款处理器名称,而成为AMD公司的灵魂。这是一个沿用了8年而不朽的称谓,它见证了AMD由受人摆布到走向成熟,见证了AMD与Intel 历时8年的性能斗争。Athlon并不是AMD的唯一产品,却成为整个公司风向标,在财务危机、裁员风波等一系列的关键时刻力挽狂澜,顽强地打破了Intel的垄断并巩固市场份额,使AMD逐渐强大。随着AMD决定在2007年第三季度发布Phonom处理器品牌,Athlon即将退役。笔者正是在8年前步入DIY殿堂,怀着对它一份特殊感情,我参考了很多资料,希望用这篇文章和大家一起回顾整个Athlon时代。

● Athlon到来之前

1993年3月22日,Intel全面超越486的586处理器问世,为摆脱486时代名称混乱的困扰并获得更好的知识产权保护(美国法律中不能用阿拉伯数字注册,Intel用拉丁文注册商标,以避免其他厂商用同样的名字,Pentium在拉丁文中是“5”的意思,后缀ium又像某些化学元素的拼写,充满了神秘和动力),Intel遂将新一代产品命名为Pentium(奔腾)并进行商标注册,以区别AMD和Cyrix等公司的产品。

Pentium采用的P5(第5代处理器)架构领先于竞争对手,并凭借市场运作等手段快速成长。同时Pentium产品的到来也宣布不同厂商的CPU架构设计分道扬镳,开始了激烈竞争。在同一时代,作为竞争对手的AMD和Cyrix显然因为架构上的落后而无法与Intel展开正面竞争,这使当时正在主推K5处理器的AMD开始反思并逐步觉醒。

Pentium(P5)微架构体系图

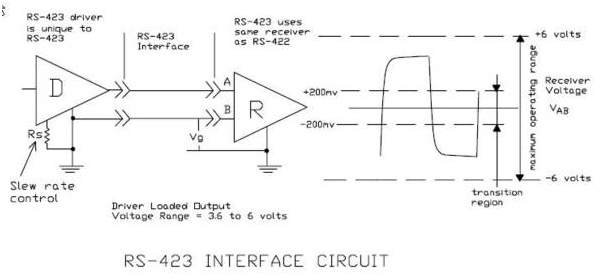

Pentium拥有8KB数据cache和8KB指令cache,初期的Pentium 60/66使用600纳米的Bi CMOS工艺,采用273 pin的PGA封装,晶体管数量是3.1百万,L2 cache集成于主板上(常见的预安装容量为256KB)。Pentium是一枚32位处理器,拥有64位的外部总线,物理内存定址空间为32位(据说工程样品出现过36位物理定址,但是正式产品降回32位),逻辑内存能力为64TB。

Intel在发布奔腾的下一代产品Pentium II时,采用了专利保护的P6(第6代处理器)架构,并且不再向AMD和Cyrix授权,AMD和Cyrix的市场份额急转直下。P6架构与Pentium的P5架构最大的不同在于,以前集成在主板上的二级缓存被移植到了CPU内,从而大大地加快了数据读取和命中率,提高了性能。

1997年4月,AMD推出K6以抵抗Intel,K6采用0.35微米工艺,工作频率在166-233MHz之间不等,基于对686处理器的研究开发,K6新增了MMX指令集(这是Intel发明的多媒体增强指令集技术,可以增强Pentium在图像、声音、通信应用等方面的性能),一级缓存为64KB,无内置二级缓存。

第一代K6还只能与具备MMX技术的Pentium打成平手,所以AMD于1998年4月迅速推出K6-2以抗击Pentium II,它支持新3D Now! 指令集(这是AMD发布的针对三维建模和效果渲染等三维应用场合性能增强的指令集,可以大幅度提高CPU的3D处理性能)及100MHz的前端总线频率(FSB),最初的时钟频率为266MHz,后增到475MHz,带有64KB的一级缓存,二级缓存位于主板上,容量为512KB—2MB之间,与总线频率同步。

后来的结果告诉我们K6-2是具有历史意义的CPU,因为它真正为AMD吹响了向Intel挑战的号角,并以极高的性价比打压了Pentium II。

1999年,Intel发布了Katmai核心的Pentium III,它在原有Pentium II核心添加SSE指令集,使用0.25微米工艺,内含900万个晶体管,512KB半速二级缓存,使用Slot 1接口。

Pentium III

K6-III

接下来诞生的则是K6-3,它于1999年2月发布,是AMD推出的第一款将二级缓存整合在处理器芯片中的产品,实际上是K6-2的改进版。它采用Socket插槽结构,主频在400MHz到450MHz,带一级缓存64KB,内置全速二级缓存256KB,创造性地外置512KB—2MB之间的三级缓存与系统总线同步。虽然K6家族的浮点性能与Pentium有不小差距,二级缓存也没有完全集成在CPU内部,但另人满意的性能和低廉的价格让Intel感到巨大的压力。它们是Athlon的前奏。

第一个4年(1999年6月23日——2003年9月22日)

● Athlon第一个4年 Athlon诞生——Pluto、Orion、Magnolia

第一款K7处理器于1999年6月23日首度亮相。AMD在K7时代给予了CPU一个响亮的名字——Athlon,其名称取自田径运动的“十项全能” (Decathlon)。从这一天起,Athlon时代正式到来。首批处理器的主频介于500到700 MHz之间,并带有512 KB的半速L2 cache,之后AMD又抢在Intel之前推出了1000 MHz的版本。这一架构内核发展共经历3个阶段:Pluto、Orion、Magnolia。这些处理器使用的插槽,与Pentium II的Slot 1相似,但两款插槽并不兼容。

采用了Slot A插槽的Athlon 650(Pluto核心)

上图就是采用了Slot A插槽的Athlon 650(Pluto核心)。这颗CPU使用0.25微米工艺制造,核心面积为184mm2,6层金属连接,晶体管集成数量达到了2200万。Athlon拥有128KB一级缓存(64KB指令+64KB数据),这一设计也在整个8年的变化中得以保留,这个阶段Athlon内核与L2 Cache采用分离式设计,核心位于长方形电路板中央,L2 Cache植荚谄淞讲啵幌馪entium II集成在一个管芯里。

如图:AMD的计划中,K6即将终结,Athlon时代到来

从Athlon时代开始,AMD的CPU能够实现乱序执行Out Of Order(它允许执行指令的顺序和取指令的顺序不同,实际上做到了指令只要有可能就执行。因为关键的路径计算可能随时开始和完成,因此这种方法加快了指令的执行速度)、可编程L2接口、在CPU与芯片组之间使用200MHz EV6总线(增加与内存之间带宽,获得更大的数据吞吐量)、增强型3DNow!TM指令集(在原有的3DNow!TM上继续完善追加至52个指令,包含一些SSE码,同时获得了更多软件的支持。但是3D Now!缺乏SSE所具备的IEEE-754兼容性、视频加速能力以及内存流式传输能力,因此虽然3D Now!一开始的时候威势不少并且有大量媒体借机炒作,但事实证明3D Now!的确有不少地方不如SSE)。

从内部而言,Athlon是完整的第七代x86处理器。也是它的同类型中的首位。这颗CPU是由AMD工程师和新雇用的DEC工程师联合开发的。所以融合了AMD以前的CPU和DEC Alpha 21264的技术。正如AMD的K5和K6,Athlon是一个RISC(精简指令集)的CPU,能够实时解码x86指令到它自己的内部指令。

AMD设计的这颗CPU提供了更加稳定的x86指令编码兼容性,使它可以同时处理更多的数据。Athlon的CISC(相对RISC而言,复杂指令集计算机)-RISC三元组解码器能够在每个时钟解码6个x86操作。关键分支预测单元(Critical Branch Predictor Unit)相比K6得到增强,这是因为Athlon更长的管线使得高准确的预测成为必要,否则将会导致使性能下降的管线延迟。

上图为Athlon的内核设计详细结构,其在设计时参考了Alpha 21264处理器。21264以超标量超流水的方式实现了Alpha体系结构,是一颗设计先进的高性能CPU,其在SPEC benchmark中取得了相当好的成绩。Alpha 21264的缓存系统也对高性能水平做出了贡献。Athlon继承了它的高效缓存设计——芯片内部L1包括一个64KB的指令缓存器(I-cache)和一个64KB的数据缓存器(D-cache)和外部总线——Alpha EV6 200MHz,片上和片外缓存提供了低延时的数据访问能力,从而带来了很高的数据访问带宽和整体性能,而且AMD K7处理器的动态分支预测技术也领先于P6架构,同时具有多重并行x86指令解码器。由于当时制造工艺的局限, L2 Cache部分只能以2/3、1/2、1/3于CPU主频速度运行,在后来很大程度上又制约了CPU整体性能发挥。以往AMD CPU较差的浮点性能在Athlon架构中同样得到改善,其浮点性能与Pentium III相比毫不逊色。

AMD的缓存设计与Intel相比也有很大不同,Athlon架构使用拥有一个很大的L1 Cache,直到今天的Athlon 64也一样没有发生变化。这表示了CPU需要的大量数据可以从L1获取,而Pentium III的L1 Cache则很小,为16KB,很大程度上要依赖于L2 Cache提供数据。所以Intel为CPU设计的L2 Cache位宽和关联度都比较高,以此来获得较高的L2带宽。特别是到了Pentium 4时,L1 Cache数据缓存只剩下8KB,Intel用新增的一种一级追踪缓存替代指令缓存,容量为12KμOps,表示能存储12K条微指令。所以Pentium 4必须有一个很大的L2 Cache,L1 Cache在Pentium 4中更多的作用是告诉CPU数据在L2 Cache的某个地方,而并没有存放很多数据。因此在低端市场,AMD可以大幅度削减CPU的L2 Cache,带来性能损失远没有Intel,这也为抢占低端市场打下了坚实的性能基础。

安装了散热器的Slot A插槽Athlon

Intel没有想到AMD在K7时代变得异常强大,这让Pentium III措不及防,Intel迅速将Pentium III过度到新核心——也就是后来最流行的Coppermine,它使用0.18微米工艺,256KB全速二级缓存,支持Socket 370与Slot 1两种接口。Intel终于把L2 cache集成到了和CPU同一枚管芯(die)内,也是在Pentium III,Intel引入了71条SSE扩展指令集,显著加强了x86处理器在流媒体处理方面的能力。

Coppermine微架构(0.18微米Pentium III,属于Pentium Pro家族第3代改进型)

其实Pentium II和Pentium III的设计来自于对Pentium Pro的改进。1995年11月1日,Intel推出了当时看来可以用“硕大”来形容的Pentium Pro处理器(中文名称是高能奔腾),这款代号P6的产品和Pentium相比革新相当大,例如整数流水线采用了10级工位的超级流水线;能作多重分支预测和猜测执行;具备能够把x86指令转换成RISC风格微操作的译码器;实现了乱序执行等。

如图,Intel CPU晶体管集成数量的发展

在规格上,Pentium Pro相当强大,其晶体管集成度发展速度甚至超越了摩尔定律,使CPU的性能进一步提高到惊人的水平。即使是这样,在整个Pentium III时代,Intel仍无法超越AMD,Athlon优秀的架构抵挡了所有来自Pentium III的进攻,在性能上几乎全面领先。更重要的是2000年3月6日,AMD抢在Intel之前,在美国加州的Sunnyvale发布了第一款实用的1GHz Athlon处理器(Magnolia核心),跨越了一个新的里程碑。对于奉行摩尔定律的Intel来说这样的局面是无论如何也抬不起头的。这在当时被称作AMD完全的胜利!

如上图,Athlon在当时的各种测试中终于让AMD扭转乾坤,也使CPU市场格局发生了翻天覆地的变化。Athlon取得不可动摇的性能领先。

在这个需要支持SMP的测试中,Athlon虽败给了双路Celeron,但用测试人员的话说:不可想象未来配备在服务器上的双路Athlon将会取得怎样的领先。

第一代Athlon 1GHz在生产时没有能得到高性能的SRAM晶圆,所以很可惜,其L2 Cache是以1/3于CPU主频速度运行的。反而随着Pentium III的频率上升,性能的增益也越来越强,不要忘了其所采用的全速Cache。在1GHz 决战时,迟到的Pentium III终于超越了Athlon。

● 延续辉煌——Thunderbird

AMD当然没有放松,Athlon开始改用新核心——拥有全速L2 Cache的Thunderbird(雷鸟)。新核心除缓存速度发生变化,几乎没有其他改进,却让Athlon再次全面开花,压制了同频Pentium III。同时Thunderbird将频率提高到1.4GHz,配套芯片组如AMD 760、KT133、KT133A也日臻成熟。

更重要的是AMD削减Athlon 的L2 Cache到64KB,打造了低端明星Duron(毒龙)。Duron(毒龙)是AMD首款基于Athlon核心改进的低端微处理器,核心面积是100平方毫米,内部集成的晶体管数量为2500万个,比K7核心的Athlon多300万个。在浮点性能上,Duron具有三个全流水乱序执行单元,一个用于加/减运算,一个用于复合指令还有一个是浮点存储单元。其他规格方面,Duron外频为200MHz,内置128KB的一级缓存和64KB的全速二级缓存,工作电压为1.5V,功耗要较Thunderbird小一些。Duron由于缓存结构的差异没有像Celeron那样性能严重降低。

Duron是AMD面向低端市场的利器,凭借先进的CPU设计构架和优良的血统,在性能上完全超过了Celeron II,特别是Duron芯片内的L2 Cache较小,芯片面积(die size)只有100mm,其功耗以及发热量也相对较低。而最令用户对毒龙难以忘怀的,自然还是其极为强大的超频能力,Duron 600通过铅笔破解倍频之后至少能够超频到800MHz,不少极品甚至达到1GHz,使很多DIYer所乐此不彼。

Duron对于AMD的意义在于将K7的架构优势成功地转换成为市场优势,其良好的性价比对Intel低端市场造成了严重威胁,至此,AMD成为了消费者心中性价比的代名词。产品层次的划分标志着AMD有能力稳定驾驭市场,并逐步走向成熟。

图为Socket 462接口的Thunderbird核心Athlon 1.4GHz

在外部封装上,Thunderbird同样表现突出。直立式的Slot A插槽变为陶瓷封装、体积小巧的Socket 462接口,这一接口也一直沿用到2003年9月22日K7生命终结。Thunderbird同样带动了AMD的再一次腾飞,强大的1.4GHz主频、200 MHz系统总线、全速L2 Cache、工作电压为1.70V~1.75V,相应的功耗也比上一代Athlon小,恐怖的超频能力同样诱人。当然不要忘了Duron,有它在低端的配合,市场上掀起了一股抢购AMD处理器的狂潮,用专业媒体的话说:Athlon、Duron市场供应闹饥荒。

● 开始革新——Palomino

微架构的研发对一代甚至几代CPU产品都有着重要影响,其研发时必须考虑制造工艺、晶体管集成度、未来发展趋势等很多方面。Intel在1998年开始了对NetBrust(网络爆发)微架构的研发并在2000年取得成效。AMD也在98年前后开始了对新的64位微架构Hammer(大锤)的研发并在2001年生产了少量测试产品。但是Hammer最终在2003年推出市场,而使得Athlon必须在这一段时间独立面对Intel。

依靠强大的产能和市场控制力,Intel在Pentium III时代依然保持了良好的上升势头。但Intel连续在与AMD的性能斗争中失利,让剧情在这里发生了变化。Intel站在岔路口上:是继续增强Pentium III的能力,提高其主频?还是转向新的微架构?迫于Athlon的压力和自己在CPU市场的地位,Intel高层做出了一个惊人的举措,决定把P6微架构的发展暂时冻结(已成功生产的Tualatin核心Pentium III必须为Pentium 4让位),转向激进的甚深流水线架构——NetBrust,也被称作P68。

如图,Pentium III和Pentium 4的流水线长度对比

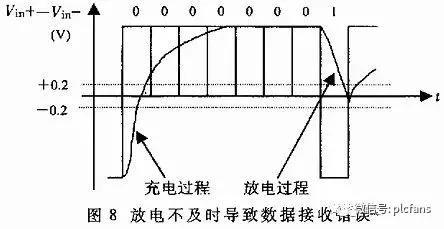

采用甚深流水线的目的为了在同样的工艺下获得更快的时钟频率,NetBrust正是如此,它采用了20级超长流水线,配合Intel的制造工艺,获得非常高的运行频率。但长流水线也有致命的缺陷——执行效率低下。流水线越长,对于采用乱序+猜测执行的处理器来说,预测失败的成本就越高。Pentium III的流水线在预测失败的时候会损失10个周期,而在第一代的Willamette Pentium 4 上就达到了20个周期。即使这样,Pentium 4照样把频率提得超高,一定程度上弥补了分支测错造成的性能损失。

Athlon开始面对一场从未预料到的战斗,对手Pentium 4采用了疯狂飙升频率的办法来打压自己,Athlon的战略也不得不做调整。

2000年11月20日,Intel发布Pentium 4 1.4GHz、Pentium 4 1.5GHz处理器,采用了0.18微米工艺技术,提供256K的二级缓存。这是采用了Willamette核心的第一代Pentium 4,虽然将频率提升到2.0GHz,但相对落后的工艺和缓存容量限制了性能的提升空间,Athlon还是能战胜它。但这时的Athlon已明显感觉体力不支,并预测到未来会迎接更猛烈的挑战。同时Athlon XP策划已经出炉,越来越多的信息表明AMD要改进核心来应对Intel。

2001年8月27日,Intel发布Pentium 4 2.0GHz处理器,采用了最新0.13微米工艺技术,提供512K的二级缓存,这标志着Northwood核心正式启用。随后,Pentium 4在1年多的时间里将频率迅速提至3.06 GHz,并引入超线程技术。而AMD则开始艰苦的追随战。

AMD于2001年10月9日正式发布新型的Athlon XP处理器,AMD Athlon XP中的XP指Extreme Performance(卓越性能),它支持更大的高速缓存、专业3Dnow!技术和QuantiSpeed架构。首批Athlon XP采用Palomino核心,制造工艺没有像人们预想的那样有所提升,而是沿用了上一代的0.18微米工艺,二级缓存的大小也维持了256KB,Palomino将Thunderbird的核心元件位置做了更改,内核形状由原来的长方形变为正方形,当时普遍认为这样的改动是为将L2提升到512KB做调整,很可惜实际的产品并没有证实这个想法。Palomino相对于Thunderbird当然还是有一些改进的,它将一级缓存中Data TLB数据缓存中的4K寻址页的地址变量寄存器由Thunderbird的24项提升到32项。这样可有有效增强缓存命中率,在缓存数量不变的情况下,有效增强了效率,商业应用下性能进一步提升。同时新核心加入了第三代3D Now!指令集,使3D Now!通过一些转换能够兼容一些SSE指令。其余架构方面完全没有改动。

如图,Athlon XP基本的架构没有发生变化,而Pentium 4则完全不同了。Athlon XP相对于Pentium 4拥有更高的IPC是不争的事实,性能(Performance)=频率(Frequency)×每一时钟周期内所执行的指令多少(IPC instructions per cycle),IPC是一个较为公正的效率值。比如Athlon XP 1600+,实际频率为1333MHz,它的性能大约相当于1颗1.6GHz的Pentium 4。

针对自己拥有高IPC,而对手拥有高频率,AMD提出了QuantiSpeed架构理论来反击“频率至上论”。QuantiSpeed架构理论有以下几个部分组成:

1、超标量完全管道化微体系结构。QuantiSpeed体系结构的核心是同时发出9条指令的超标量完全管道化微体系结构。这种体系结构能提供更多的路径,并应用指令传送到核心的执行机制,因而处理器能够在给定的时钟周期内完成更多的任务(高IPC)。路径(管道)深度与处理器操作频率之间的良好平衡能产生极高的性能。如果只是管道更长,就会产生较低的IPC和高操作频率。如果只是管道更短,将提高IPC,但频率会降低。AMD Athlon XP处理器能够保持管道深度与处理器频率之间的平衡,因而能实现极高的总处理器性能。

2、超标量完全管道化浮点QuantiSpeed采用了超标单元量完全管道化浮点运算单元(FPU),与x86处理器相比,不但能够在每个时钟周期内完成更多的浮点操作,还能提高操作频率,因而能产生最强大的x86 FPU。AMD Athlon XP处理器有足够的计算能力,能满足计算最密集的软件应用的要求。

3、硬件数据预取将指令从系统内存预取到处理器的一级指令高速缓存中,提高了处理器的工作吞吐量,从而提高整体性能的通用作法。QuantiSpeed体系结构的这种特性能将数据从系统内存预取到处理器的一级数据高速缓存中,从而缩短了向处理器输入关键数据的时间,提高了工作吞吐量。因此,在使用带QuantiSpeed体系结构的AMD Athlon XP处理器时,应用性能将自动得到增强。

4、非复用TLB。QuantiSpeed体系结构中的TLB结构能保留关键数据表以及靠近处理器的指令。当再次请求数据或指令时,这种设计使处理器无需等待就能开始操作。这些TLB结构现在更大,在高速缓存之间是唯一的,具有预测性。更大的TLB使AMD Athlon XP处理器能访问其它图形;这些结构的排他性消除了信息复制,在二级高速缓存中释放出更多的空间,留给处理器使用其它有用信息;推测使AMD Athlon XP处理器能快速产生关键数据和指令的未来图形。对TLB结构的这3种增强进一步提高了每个时钟周期能完成的工作量,从而提高了AMD Athlon XP处理器的实际应用性能。

QuantiSpeed架构理论实际上是完全相对NetBrust微架构提出的,它全面总结了Athlon XP一贯的架构优势,间接地说明对方高频低能。Athlon XP在此理论背景下重新启用了废弃多年的PR值对CPU性能进行标注,当然这也是在Intel的高频压力下被迫做出的举动。特别是像Pentium 4这样使用长流水线的CPU,IPC相对Athlon XP偏低,所以频率较低的CPU使用PR值来标注性能是完全可行的。

在其他方面也有一些变化,与Thunderbird核心相比Palomino对核心做了一些优化,如晶体管数量增加的同时CPU功耗大大减少。新核心中集成了热敏二极管和温控电路,使处理器具备内核温度探测和过热保护功能,增强了CPU的稳定性和易用性,改变了以往给人们不稳定的印象,性价比在Pentium 4的压迫下也同样很高。Palomino最终把频率提到1733MHz,PR值为2100+。

当然实际频率低会造成CPU在流媒体和数据转换应用中性能下降,所以Pentium 4在这些方面一直保持着对Athlon XP的压制。还有一点是不能忽视的,在FSB方面,Athlon XP也一直没有超越Pentium 4,这意味着Athlon XP在数据密集型,内存敏感型等方面不能和Pentium 4相比,Athlon XP运用EV6总线最终将FSB提升到400 MHz,而Pentium 4则使用QDR-speed四倍速前端总线技术把FSB做到800 MHz,内存吞吐量达到6.4GB/s。

● 坚持斗争——Thoroughbred(A/B)

2002年6月10日,继Palomino之后,AMD又再发布了新品——采用Thoroughbred核心的新版本Athlon XP处理器。与此前的Palomino核心的相比,Thoroughbred核心在处理器逻辑线路上并没有重大改动,主要区别在于采用了0.13微米制程的新工艺。

在Athlon时期,很多用户对AMD产品的性价比还是满意的。但是,发热量过高和核心脆弱而且易烧毁是AMD始终没有解决的问题。采用Thoroughbred核心的新版本Athlon XP处理器,就是这一情况下的产物。

Thoroughbred A核心是AMD首次采用0.13微米工艺的处理器,新工艺将核心面积缩小到80平方毫米,而且在相同集成度的情况下能有效减弱并提高频率,相应将超频能力也做提升。同时CPU内部单元的位置进行了更改。

如图,Thoroughbred-B处理器

不过由于工艺制程的不成熟,加之超频能力不强,这款产品事实上也没有获得太多的市场认可。而此后,AMD为了解决Thoroughbred的问题,再次对其进行改进,也就是改良版本Thoroughbred-B。与早期版本Thoroughbred相比,改良版本Thoroughbred-B最大的改进就是发热量下降,频率提升,而且拥有不错的超频能力。

但当Thoroughbred全面上市为Athlon XP争取市场时,Pentium 4已将频率提高到不可思议的3.06 GHz并开始将中端产品全面铺货,加上娴熟的市场操作能力,Intel控制了主流市场并开始普及Pentium和Celeron品牌。AMD由于产能和性能问题,在高、低端市场已无力对抗,被迫放弃低端经典Duron品牌,由低频的Athlon XP对抗Celeron,高端方面则艰辛地提升频率,推出PR值更高的产品。Thoroughbred A和B最终将频率提到1800 MHz和2250 MHz,PR值上升为2200+和2800+。

当然AMD没有放弃Hammer(未来的Athlon 64),甚至为了Hammer的开发AMD耗费了大量精力,直接影响到了Athlon XP。功夫不负有心人,AMD已经生产了一些Hammer并送往芯片组开发商,越来越多关于Hammer的消息向外界传来。同时AMD开拓了一些市场,如AMD发布了面向笔记本电脑的处理器——Mobile Athlon XP,同时AMD还拓展市场,发布了基于Athlon XP核心,针对工作站、PC服务器的Athlon MP。

如图,Athlon MP的配套芯片组,支持双路CPU

当然此时的AMD也背上了严重的财务负担,亏损巨大,债务沉重。人们将期望的目光投降Hammer,因为这才是AMD真正的出路,这颗神秘的CPU能担当起振兴AMD的重任吗?

● 完美谢幕——Barton

在得知Pentium 4 3.06 GHz附带HT技术发布时,AMD做出强有力的回应。AMD于2003年2月10日正式推出他们全新采用0.13微米制程,基于Barton核心的Athlon XP 3000+处理器。Barton仍属于Athlon XP,采用333MHz FSB,内建512KB L2 Cache。Barton核心面积从84mm2增长到101mm2,而晶体管数目也远远高于Thoroughbred的3,760万,达到接近于Northwood的5430万个。

如图,左边是新的Barton,右边是Thoroughbred,核心形状明显增长了。

如图,核心形状的变化在上图中得到体现。

L2的扩大带来了面积的增长,当然缓存容量的变化也会引起TAG(二级缓存检索表)的变化,总的来说,这两款核心并没有涉及到内核基本架构的变化。AMD随后再接再厉,将Barton的FSB提升到400 MHz,主频也达到2200 MHz,终于达到了Athlon XP的极限PR值3200+。此后AMD于2003年10月24日正式公开了新的roadmap蓝图,宣布了Hammer市场计划,也同时不声不响地宣布了Athlon XP的生命结束。

增加的256KB L2 Cache比较有效地提升了Athlon XP的性能,特别是一些商业和数学应用中,Athlon XP相对于Pentium 4取得一些领先,在3D应用中,几乎追平了Pentium 4。AMD在没有大改核心的情况下继续稳定提升了性能,保证了一定的市场占有量。更重要的是它为Claw Hammer(AMD第八代处理器K8)做了市场过渡。

上图为Athlon XP时代所有CPU规格细节

从现在来看,Barton是AMD第七代处理器(K7)的第七代核心,它成功地为K7时代划上圆满的句号,而没有轻易向Intel屈服。回顾前面所列举的7种不同Athlon核心,我们会发现这样一个有趣的现象,Athlon的L1 Cache一直为全速128KB,没有发生变化。而L2 Cache从最初的片外512KB到片内256KB,直到Barton的片内512KB。缓存容量似乎划出了一个圆圈,Pluto是起点而Barton是终点,起点与终点的不同是这512KB的缓存从核心外集成到核心内,而CPU的运行频率也提升了4倍,从最初的500 MHz提升到3200+的2200 MHz。这个圆圈,AMD花了4年时间终于圆满完成。

● Athlon第二个4年(2003年9月23日——2007年第三季度)

当年K7的发布让AMD第一次在竞争中占据主动,Athlon处理器捍卫了AMD的尊严。然而性能优秀的K7核心并不能挽回AMD在市场策略上的颓势,市场手腕的缺乏不是仅凭优秀的硬件设计就可以挽回的。在AMD身处逆境的时候,K7成了AMD苦苦支撑战局的唯一武器。这一切一直延续到AMD向大众宣布K8处理器才得到改观,在2001年的微处理器论坛上,人们重新对AMD寄予了无限的希望。

2003年末,Intel发布了支持超线程(HT)技术的P4至尊版 3.20 GHz,采用0.13 微米制程,具备 512 KB二级高速缓存、2 MB 三级高速缓存和 800 MHz 系统总线速度。Intel显然在继续着NetBrust微架构的发展路径,将提升频率作为首要任务。当然Intel也在计划着新的核心架构——Prescott,它采用新的90纳米工艺,加入了应变硅技术支持。当然它依然遵循NetBrust微架构,流水线长度破记录地达到31级,全力提升频率。

2003年4月24日,AMD在美国纽约发布了AMD第一款64处理器——Opteron,它在专业领域使用,表现出了强劲的性能,但真正的反击还在后面。而2003年9月23日,AMD完全改变了历史。研发代号为Hammer的第八代CPU(K8)——Athlon 64登场,全新的架构,全新的计算技术,全新的总线设计,又一次给Athlon这个光荣的代号带来巨大的性能提升。

K8是一款倾注了AMD几乎所有CPU研发资源的产品,其从98年开始研发。K8系列的核心集成了1亿500万晶体管,核心面积达到193平方毫米,新核心包括9组功能单元(3组ALU、3组AGU、FADD、FMUL和FMISC,包括3组整数和3组浮点运算器)以及3组x86译码器。一级缓存的容量上也没有发生变化,指令缓存和数据缓存各64KB,总容量128MB,同时增加了ECC校验电路。

而K8最大的特色就是对64bit计算技术的支持,凭借x86-64架构,将传统x86的32bit模式扩展到64bit,这样,CPU就可以在同样的一条指令中,处理整数数值并管理更大的内存区域。此外,在Athlon64处理器架构中,AMD还首次引入了HyperTransport总线,主要负责处理器与北桥芯片间的数据传输。

另外,K8还集成了内存控制器,极大地降低了Athlon64数据收发延迟、缩短读写请求的反应时间,同时也简化了主板北桥的功能。除此以外,K8还改善了K7的功耗问题,在CPU中加入了Cool'n'Quiet技术,降低发热和耗电。从K8开始,AMD不再是“电热炉”的代名词,相反,高功耗则成为了Intel需要解决的问题。

如图,Athlon 64内部架构简表。核心设计中的以下几个热点我们必须关注:全新设计的AMD 64核心;x86-64计算技术;集成DDR内存控制器;HyperTransport总线;Cool’n’Quiet与EVP。

● 1、全新设计的AMD 64核心

上图为,Athlon 64内部架构,我们可以看到和K7相比,K8执行单元的的物理数目是一致的,同样的3个负责整数运算的ALU、AGU单元,同样的3个负责浮点、3DNow!等多媒体指令运算的浮点单元。如果不考虑新的64位指令执行状况,基本上两者处理数据的流程将非常相似。我们注意到K8核心同时用于桌面系统和企业级应用,出于这点考虑,在核心中加入更多的执行单元对K8并没有明显的意义。接下来,我们看到从K7开始就有的微小改进:尽管K8和K7采用了一样数目的浮点调度程序窗口(scheduling window),但是整数单元从K7的18个扩充到了24个。

第二个改进就是缓冲部分,一级缓存、二级缓存部分,K8同K7核心相比,除了将二级缓存容量统一提升到1MB,二级缓存位宽相比K7核心的64bit倍增为128+12bit之外,并没有在结构上做出太大的变动。然而CPU中另一类重要缓存——主管内存地址翻译的TLB的相关参数,却在K8中相对K7处理器做出了较大的变动。

TLB的英文全名为:Translation Lookaside Buffer,我们可以翻译为旁路转换缓冲,也可以把它理解成页表缓冲,因为它里面其实存放的是一些页表文件(虚拟地址到物理地址的转换表)。

对于寻址空间更大的K8,增加TLB条目数,改变TLB联合方式显然具有更重要的意义。同时,在TLB控制机构方面,为了提高在程序间切换时的处理器性能,Athlon 64也相应K7核心做出了一些变化。此外,更大的TLB对于多线程处理和多处理器发展有相当大的积极意义,和Intel的超线程技术一样,更大的TLB有助于在多核心多线程应用的发展上迈出有意义的一步。

Hammer在TLB的连接方式上也有一些变化。TLB也分为2级,主要用于更快的完成虚拟地址向物理地址的映射。这是由于Hammer处理器没有储存或访问物理地址的能力,它必须通过虚拟地址来完成对主存空间的访问。将虚拟地址转化为物理地址需要3个时钟周期。TLB将以前的映射的结果保存下来,这样当需要用到原先访问过的数据时就可以直接在TLB中搜索相关的物理地址,而不需要进行映射运算,这样只花费1个时钟周期。

如上图,接下来还有一个重要的改进,它在执行单元数目不变的情况下大大增强了效率,那就是改进的分支预测单元。分支预测技术让流水线式工作的处理器成为可能,在K8中,AMD将K7中的分支预测单元做了改进。global history counter buffer(用于记录CPU在某段时间内对数据的访问,我们可以称之为全历史计数缓冲器)比起Athlon来足足大了4倍。全历史计数器是一列2比特的计数器(2比特计数器从0计数到3),它决定是否应该执行特殊的分支。当一个分支指令到达后,分支预测单元读取指令中一部分地址(有时对地址进行一些逻辑操作),并用来把它作为全历史计数器的索引,这直接决定了哪一个计数器进行工作。对索引页的计数器进行检验,如果它的值大于或等于2,那么分支被预测为执行,然后执行分支。如果分支被错误预测,那么计数器的值会减一,但是如果下一次预测准确的话,计数器的值会再次加一。现在这种方法带来的问题是,如果你有两条分支指令同时给出了同一个索引值,相关的计数器会武断的增值或减值,这被称为干扰(interference)。全历史计数器的容量越大(大于2比特),发生干扰的几率就越小。于是把干扰的几率降低,执行单元便能得到更为准确的分支预测。

正因为如此,K8才能够“记住”更多的分支,从而提高分支预测的整体效率。要想获得较高的命中率,仅仅是对原有预测机构进行简单修正显然是不够的,AMD还为改进的分支预测单元加入了分支地址计算器(branch address calculator简称BAC)。BAC可以快速(5个时钟周期)准确的计算出下一条分支的地址。

说到这里,大家很容易想到NetBrust微架构,它就是因为流水线过长,而引起分支预测错误带来的损失非常大,冗长的管线一旦遇到分支测错,就必须从新填充,造成了高频低能。而K8核心这次增强分支预测的能力,正是要为加长流水线长度——提升频率做准备。

如上图,和我们熟悉的K7架构10级整数流水线相比,K8加长了2级,增加2级线管深度的目的在于提升K8的核心频率。流水线的级数越多,每个时钟频率的负荷就越小,因此CPU就可以运行在更高的频率。拥有很强大的分支预测能力做保障,AMD完全有把握加长流水线,获得更高频率,事实也证实了AMD正确的选择。2级新增的流水线让K8的极限频率达到3.0GHz,这相对于NetBrust微架构最终将频率提升到3.8GHz是很划得来的。一般说来,专家认为当处理器的核心频率处于1G到几G的范围内,最理想的管线深度应该在12至13级。

● 2、x86-64计算技术

从CPU能够处理的指令长度来划分,Athlon 64属于64位CPU,这彻底区别于所有的Athlon XP和Pentium 4处理器。K8能运行64位程序,正是得益于x86-64计算技术,而x86-64的精髓则是向下兼容。

我们在这里说的位数,也叫做字长。在信息技术领域,“字长”是衡量计算机性能的重要标准之一。字长在很大程度上决定着计算机的内存最大容量、文件的最大长度、数据在计算机内部的传输速度、处理速度和精度等性能指标。

(通用)寄存器是处理器内部在运算过程中暂时存放数据的存储单元,里面保存着那些正准备要处理的数据或者是已经处理过的数据。CPU的运算单元访问寄存器所用时间要比访问处理器缓存以及内存的时间都要短。我们知道CPU能不能运行一条长度最长为64位的指令,最终是由其寄存器位数决定的。而且位数不仅决定了处理能力,也制约着CPU在存储器中的寻址能力,32位CPU只能进行32位的内存寻址(2的32次方byte),也就是说CPU只能直接访问4GB(4千兆字节)的虚拟地址空间,但64位CPU理论上能够对2的64次方byte(1600亿亿字节,180亿GB)内存进行访问,可在今后相当长时间内完全满足计算需求。

好了,让我们回到Athlon 64的x86-64计算技术,看看AMD是怎样实现寄存器升级的。

x86-64寄存器的扩展方式如下:

AL范围表示0-7的8位寄存器,AH则表示16位寄存器,EAX就是我们大多数用户使用的32位寄存器,如Athlon XP和Pentium 4,RAX则是AMD拓展的64位寄存器。它能够存放一个64位长的数据,从而让CPU直接处理。从EAX到RAX的扩展,就同15年前Intel发布i386处理器时,将AX扩展为EAX的做法一样。当时i386在应用程序方面比起它的前辈i286来说,表现相当优秀。现在K8也采用了相同的做法,让该处理器可以很轻松的运行32位代码,在这种情况下CPU是没有满负荷运行的。

如下图要完成这些运算AMD为其引入了少量的新寄存器,作为现有寄存器的扩充:

与以往的32位X86结构相比,K8在原有的8个通用寄存器的基础上又增添了8个寄存器。这8个寄存器工作在64位下,经过64位编码的程序就可以使用到它们。AMD同时也将原有的EAX等寄存器扩展至64位的RAX。从扩充方式上看,EAX等寄存器可以看作是RAX的一个子集,系统仍旧可以完整地执行以往的32位编码程序。通用寄存器除了可高效的存储数据外,还可作为寻址时的地址指针,从而缩短指令长度和指令执行时间,加快CPU的运算处理速度,同时也给编程带来方便。单单从寄存器结构来看,X86-64较多的寄存器将会大幅度的提升处理器的性能,也会更加受到软件开发人员的喜爱。

下表则反应了Athlon 64的x86-64所用寄存器的具体区别:

现在新增加了R8-R15通用寄存器(GPR),这些寄存器都工作在64位模式下(这意味着在该模式下程序需要重新编译),原来的寄存器诸如EAX、EBX也由32位扩张至64位。Athlon 64在SSE单元中新加入了8个新寄存器以提供对SSE2的支持,寄存器数量的增加将直接带来性能的提升。

64位指令工作原理示意图

需要强调的是,通常所说的64位指令,并不是指指令的全长或操作码的长度为64位,而是指操作数所能达到的最大位数为64位。通过上面的图示,可以很好地理解64位指令和64位处理器的本质。

为了更好的在32/64位混合模式下工作,X86-64结构提供了多种处理器工作模式:

“长模式”下如果用户使用64位操作系统以及为64位计算编译的软件,那么就可以获得8个新增64位通用寄存器、扩展6 4位通用寄存器等众多新特性。“长模式”下还包含了一种“兼容模式”,在此模式下用户可以在64位操作系统上运行32位的应用程序,从应用程序的角度看,在“兼容模式”下其所使用的处理器也就是普通32位X86处理器。而从操作系统的角度来看,常规的地址变换,中断以及系统数据结构操作都是在64位“长模式”下进行的。

“传统模式”则是AMD的64位处理器为32位应用所提供的运行模式,这种模式下的X86-64结构处理器的运行与一般的32位处理器没有区别,可以完全兼容目前的32位操作系统以及32位应用程序。如果一颗Athlon 64运行在32位操作系统(和32位软件支持)下,它会自动在32位代码后补32个0,构成64位代码,轻松跨平台工作,实现无缝兼容,最大限度保护用户投资。按照AMD的说法,这个过程造成的性能损失在1%左右,“传统模式”下的Athlon 64其实就是一颗高性能的32位CPU。

在64位CPU问题上,Intel一直在尝试推广并将其在Itanium上使用的IA-64架构引入桌面级CPU,以达到64位应用的普及。但从上表我们可以看出这是很难实现的,IA-64要求软件代码完全重写才可以获得更高的性能,但这个代价是巨大的。当然Intel也预料到了这些问题,它在很早准备了一套B计划(Yamhill技术,这是一种具有64位扩展空间的32位芯片技术,完全类似于AMD的X86-64)。现在我们所使用的64位Intel处理器实际上都加入了Yamhill技术来获得对64位软件的支持。这也同时表示了Intel放弃IA-64架构,加入到AMD的X86-64阵营。Yamhill技术现在实际的应用名称为EM64T(Extended Memory 64 Technology,扩展64位内存技术)。

AMD与Intel的关系正在变得越来越“微妙”:一方面,相对Intel而言AMD是弱小的,难以对抗其在多方面的优势及成功。但另一方面,AMD又具有相当的实力,它的处理器足以与Intel产品在主流市场相抗衡,加之其发布的兼容X86的64位架构CPU,正如15年以前Intel在它的80386中所做的一样——同时兼容32位和16位程序,今天聪明的AMD也正在让它的64位处理器重复着当年Intel的成功。

● 3、集成DDR内存控制器

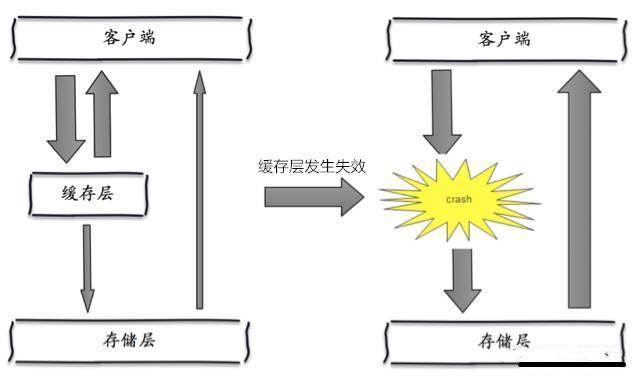

为了彻底铲除CPU与内存间的瓶颈,尽可能减小内存到CPU的延迟时间,AMD把以往北桥芯片中的主要部分——内存控制器内建在CPU中。和通常的做法不同,将内存控制器集成在处理器芯片中从而代替了传统的北桥芯片,这样做最大的优点就是该控制器运行频率可以达到处理器核心频率的水平,因此其潜伏期将变得更短。而且随着处理器频率的提高,潜伏期将越来越短。

我们知道内存中的数据被调往CPU要经历多个环节,其中内存到芯片组的速度和芯片组到CPU的速度是产生延迟(潜伏期)的罪魁祸首,已有过许多芯片组因为设计失误导致延迟过长而降低性能。许多测试也表明Athlon 64的延迟时间表现很出色。

集成DDR内存控制器看似简单,其实更重要的作用是在SMP(对称多处理)架构中建立高效的内存读取机制。实测表明,集成内存控制器使K8系统的延迟大幅度低于Xeon、高频P4等系统。同时这项技术可以简化芯片组的设计,如NVIDIA支持AMD64位CPU的nForce3芯片组省去了北桥芯片,成为单芯片芯片组。

现在不少CPU都根据其应用需求把内存控制器集成于CPU内,例如IBM的Bluegene/L、Cell、SUN的UltraSPARC T1(Niagara)等,按照Intel在中科院高性能计算机研讨会上演讲的一份资料,该公司的下一代Itanium体系架构——Tukwila也将会集成内存控制器。Cache再大也是难以避免命中失败,失败后CPU必须去内存寻找数据,当初DEC的Alpha处理器研发人员就一直很渴望把这样的损失透过集成内存控制器降低到最低,Athlon 64终于实现了这一点。

当然集成内存控制器也是把双刃剑,它在提高性能的同时要求AMD必须及时更新内存支持标准,及时发布新品以支持新的内存标准,同时老的CPU即使更换平台也不能对新的内存进行支持。还有一点需要注意的,Athlon 64并没有将AGP控制器集成在CPU中,如果使用集成显卡,图形芯片需要获得帧缓存(显存),必须检测从HT总线到CPU内建内存控制器部分数据,这将降低整合图形核心的性能。

但是这些缺陷不足以对集成DDR内存控制器的正确性构成威胁,AMD这次的设计还是相当见效的,毕竟对手的模仿也说明了自己的成功。

● 4、HyperTransport总线

HyperTransport(简称HT,超传输),是AMD为K8开发的一种双向的“点对点”高速数据传输总线,运行于处理器与芯片组或芯片组间其它部分的连接中。HyperTransport的发展历史可回溯到1999年,它原名为“LDT总线”(Lightning Data Transport,闪电数据传输)。2001年7月,这项技术正式推出,AMD同时将它更名为HyperTransport。随后,Broadcom、Cisco、Sun、NVIDIA、ALi、ATI、Apple、Transmeta等许多企业均决定采用这项新型总线技术,而AMD也借此组建HyperTransport开放联盟,从而将HyperTransport推向产业界。

在基础原理上,HyperTransport与目前的PCI Express非常相似,都是采用点对点的单双工传输线路,引入抗干扰能力强的LVDS信号技术,命令信号、地址信号和数据信号共享一个数据路径,支持DDR双沿触发技术等等,但两者在用途上截然不同—PCI Express作为计算机的系统总线,而HyperTransport则被设计为两枚芯片间的连接,连接对象可以是处理器与处理器、处理器与芯片组、芯片组的南北桥、路由器控制芯片等等,属于计算机系统的内部总线范畴。

在SMP架构中,处理器间也是通过内建额外的HT控制器进行连接的,AMD将这称为“glue less”(免中介)方式。

| 有效频率 MHz | 总线宽度 (number of pins) | ||||

|

| 2 | 4 | 8 | 16 | 32 |

| 600 | 150MB/sec | 300MB/sec | 400MB/sec | 800MB/sec | 1600MB/sec |

| 800 | 200MB/sec | 400MB/sec | 600MB/sec | 1200MB/sec | 2400MB/sec |

| 1000 | 2500MB/sec | 500MB/sec | 800MB/sec | 1600MB/sec | 4000MB/sec |

| 1200 | 300MB/sec | 600MB/sec | 1000MB/sec | 2000MB/sec | 4800MB/sec |

| 1600 | 400MB/sec | 800MB/sec | 1600MB/sec | 3200MB/sec | 6400MB/sec |

HT本身具有很多的优点:高速、低延迟时间、结构紧凑。该总线最大可以提供6.4GB/s的带宽,通过简单的设定总线位宽(2位到32位)和工作频率(400MHz到1600MHz)来灵活改变总线的带宽(100MB/s到6.4GB/s)。

上图表示的是K7时代多路CPU与芯片组连接的方式,它采用同为点对点传输的EV6前端总线技术,前端总线数据传输率为总线运行频率的2倍,即200×2=400MHz。多CPU间不仅共享前端总线,同时还必须共享集成在北桥里的内存控制器,这个带宽必须做到很大才可以提供足够的数据量来满足CPU,这是很困难的。传统的连接方式缺陷有两方面,其一是由于前端总线和内存控制器外置,导致CPU同内存进行数据交换时的延迟较大;其二是由于AGP显卡等I/O设备和内存一起共享前端总线同单CPU或多CPU交流,特别是在多处理器的环境下,由于前端总线为多处理器共享,造成前端总线“交通拥挤”,效率不佳。

新的K8使用了全新的北桥架构,把北桥一分为二,将传统北桥的内存控制器和北桥总线接口内置到CPU核心中,而传统北桥中的AGP控制器以及同南桥进行数据交换的接口界面则仍然外置。新的北桥架构通过外置HyperTransport总线将北桥的内置部分同外置部分的AGP控制器等连接在一起。这样做还透露出AMD一个更长远的打算,那就是优化SMP的结构性能,如图。

这张图中,我们看到的是K8的专业版——Opteron,它是AMD为服务器和工作站设计的优化支持SMP的CPU。它区别于Athlon 64的一个重要特点就是集成了3个HT控制器。如图,每个大方框就是一颗Opteron,它包括一个CPU核心,一个系统请求对列(SRQ)中,一个内存控制器(MCT),一个切换控制器(XBar,负责管理内存控制组、CPU核心、以及3个HyperTransport端口之间的数据传输)。4颗Opteron利用自身的优势不需芯片组特别支持,便组成了一个高效的SMP系统,如下图。

在SMP架构中,多颗CPU同时执行程序的单一副本,须调用同一内存。但由于Opteron内置了内存控制器,使得每颗Opteron处理器都有独立的内存通道,并且是双通道DDR内存(PC2700),可提供最高2.7×2GB/s=5.4GB/s的带宽。这说明了一个重要的问题:每颗CPU不用再与其他CPU共享带宽,而独享内存提供的带宽。这对于SMP架构是又一次革命。直到Intel最新的Itanium2,都是4颗CPU用同一总线与CPU连接,共享6.4GB/s的带宽,平均单颗1.6GB/s,不能与单颗Opteron的5.4GB/s相提并论。这一切都应归功于上面的两项技术。如果CPU没有集成内存控制器,每颗CPU都必须要与北桥芯片相连并得到可怜的带宽,在64位运算下,这样的带宽是显然不够用的。在上图所示的模型中,系统能够支持多达32个DIMM,在使用PC2700内存时可以提供高达21.3GB/s的系统有效带宽。

如上表,AMD为我们列出了所有Opteron处理器所具有的特性和优势。x86-64计算技术,集成DDR内存控制器和HyperTransport总线设计功不可没。

● 5、Cool’n’Quiet低功耗技术与EVP硬件防毒技术

Cool’n’Quiet低功耗技术与EVP硬件防毒技术分别可以为Athlon 64提供动态功耗调整和硬件底层防止溢出型病毒攻击。它们作用于CPU不但没有提升性能,反而消耗了系统资源,而正是这两项技术,让我们看到了AMD的成熟和一个大厂的风范。

总的来说,Cool’n’Quiet(读音来自Cool and Quiet连读)是一项能让CPU在闲置状态下自动降低电压与频率的节能技术,看到这里我们会想到在移动领域,CPU一般都带有类似技术,但将这种技术应用于桌面CPU,AMD还是为数不多的厂商。

长远来看,这项技术还是很有必要的。第一次发布的0.13微米工艺制造的Athlon 64功耗已经达到89W,而同期Intel的Prescott核心Pentium 4功耗已达到103W,CPU在整个硬件系统中所占的功耗比重越来越大,同时带来了发热和散热所制造的噪音也越来越不能被忍受,Cool’n’Quiet的提出有效缓解了这些问题,当只运行小型程序或系统负荷较轻时,它通过硬件监控让CPU在闲置状态下降低电压和频率,随之带来的更低的功耗和发热,有效地节约了资源,延长了CPU寿命。

开启Cool’n’Quiet功能后,CPU会以每秒30次的频率自动监测系统负载,并且根据负载情况动态更改工作频率和借供给电压,将CPU从全速状态下解放出来,从而达到节省电力消耗的目的。以Athlon 64 3000+为例,该处理器频率为1.8GHz,默认的外频为200,倍频为9,电压为1.378V。当该CPU处于空闲状态或处于文字处理等简单的工作时,由于CPU占用率很低,Cool’n’Quiet技术便开始发挥作用,在外频不改变的情况下把倍频降低至5X,电压降至1.1V,这时CPU工作在1GHz的模式下,功率便降低到40W左右,当然也就达到了降低功率和发热量的目的。

AMD于2004年8月,与微软一起设计研发了AMD的新芯片功能“Enhanced Virus Protection”(EVP增强型病毒防护)。AMD 64位处理器(包括Athlon 64/Athlon 64 FX/Athlon 64移动版本/Sempron移动版本等)冀哂蠩VP功能。

EVP是AMD应用在全部K8 CPU中的一项技术。它可以防止溢出型病毒的攻击,这种病毒本质上是一种让CPU因缓冲区溢出而执行恶意代码的攻击技术。AMD介绍说,应用这项新技术后,缓冲区的数据将会只被读取而不能执行,这就有效防止了恶意代码的运行。AMD这次发布硬件底层防病毒安全技术领先于竞争对手,尽管Intel表示在2004末会在其芯片中加入类似技术,但离投放市场还有很长一段时间。而EVP在被开启后立即可以配合Windows XP SP2在CPU上运行。

面向服务器市场的Opteron也支持EVP功能,但需要在安装Windows Server 2003 SP 1以及面向X86-64架构的Windows Server 2003版本后才能够打开这一功能。据AMD公司表示,EVP技术将能够更好地保护计算机在完成接收电子邮件、从互联网上下载文件等日常任务时的安全性。

下面让我们以Athlon 64的核心变迁为主,简要回顾Athlon在第二个4年的足迹。

● 反击开始——SledgeHammer

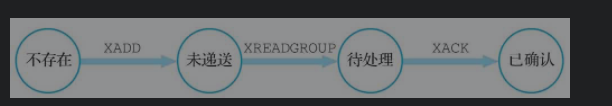

2003年4月24日。AMD宣布将开发代号为“SledgeHammer”的64位处理器正式定名为“AMD Opteron”。这是AMD于美国当地时间4月24日宣布的。它是AMD第八代面向企业的处理器。

Sledgehammer是AMD服务器CPU的核心,一般为940接口,0.13微米工艺。Sledgehammer功能强大,集成三条HyperTransprot总线,128K一级缓存、集成1M二级缓存,可以用于单路到8路CPU服务器。Sledgehammer集成内存控制器,支持双通道DDR内存,由于是服务器CPU,支持ECC校验。

严格地说它不属于Athlon 64核心,但它为AMD吹响了反攻的号角,开始了在高端领域的应用,为后面即将上市的产品营造了良好的市场和舆论氛围。

Sledgehammer同样和中国结下不解之缘,中科院计算所国家智能计算机研究开发中心在2004年初完成了曙光4000A巨型计算机的搭建,该机共使用了2560颗AMD Opteron 848处理器(支持4或8路CPU,主频2.2GHz),5TB内存总容量,42TB磁盘总容量。Cluster架构使得这些硬件均匀分布在曙光4000A的各个运算节点上。曙光4000A Linpack成绩为8.061万亿次,峰值运算力达到11.264万亿次,Linpack运算效率更达到71.56%的世界第一,位居当时全球超级计算机TOP500排名第10位。Sledgehammer的应用让中国当时一跃成为世界上第三个能制造和应用10万亿次以上超级计算机的国家。

利用自己在桌面市场的性能优势,AMD还用Sledgehammer打造了桌面顶级CPU——Athlon FX,用来和Intel的至尊版CPU——Pentium 4 EE进行全产品线对抗。让广大硬件玩家也有了更广阔的选择空间。

● 全面进攻——Clawhammer

借助Sledgehammer的成功,AMD继续发布了面向桌面市场的Clawhammer,它就是2003年9月23日发布的Athlon 64。初期产品采用成熟的0.13um制造工艺,核心电压1.5V左右,二级缓存为1MB,封装方式采用mPGA,集成一条Hyper Transport总线,内置1个128bit的内存控制器。采用Socket 754、Socket 940和Socket 939接口。Clawhammer拓展了AMD 64位CPU的应用范围,使64位应用飞入寻常百姓家,它的发布也是公认的64位时代的开始。

如图,Clawhammer的核心图,1MB的L2 Cache占据了很大面积。

而此时的Intel则停留在32位应用与NetBrust微架构下,在经历了散热、工艺、总线频率支持等诸多磨难之后,Prescott终于在2004年初发布了,但采用了90纳米新工艺的Prescott发热巨大,同时由于在流水线长度达到31级,效率同样低下。

2004年Athlon 64全面对阵Prescott核心Pentium 4,并取得了领先。在市场占有率上AMD开始逐渐抢夺Intel的份额,同时AMD开始了又一轮与大厂商的广泛合作,基于Athlon 64的个人电脑开始上市并热销,当然服务器市场上的Opteron也表现抢眼,AMD开始走出低谷。

● 适应市场,创造市场——Newcastle

这是AMD于2004年8月发布的新核心。Newcastle与Clawhammer的最主要区别就是二级缓存降为512KB,socket 939(这也是AMD为了市场需要和加快推广64位CPU而采取的相对低价政策的结果)。按照AMD的预计,新的Newcastle核心将全面取代Clawhammer,同时使用新接口,降低二级缓存以降低成本。

● 新工艺加入——Winchester

AMD在2004年中尝试了新的90纳米工艺,并将该工艺首先应用在Sledgehammer的升级核心Troy上,同时AMD向Troy添加了200MHz外频,1GHz HyperTransprot总线,SSE3指令集,当然Troy核心也带来了新的性能更强的Athlon FX。随后AMD发布了90纳米工艺的Winchester。

Winchester是AMD Athlon 64核心,一般为939接口,90纳米制造工艺。这种核心使用200MHz外频,支持1GHz HyperTransprot总线,512K二级缓存,性价比较好。Winchester集成双通道内存控制器,支持双通道DDR内存,由于使用新的工艺,Winchester的发热量在实际测试中并没有比旧的Athlon 64小,性能基本稳定,功耗方面Winchester相对与Newcastle有大约12%的下降。Winchester并非是完全成熟的90纳米产品(特别是高频下),所以Winchester实际的超频性能不及预想的那么好。

而此时Intel给我们带来的只有一些信息而没有实际能与Athlon 64向对抗的产品,包括双核心的Montecito Itanium 2投入应用,新的65纳米工艺,值得我们重视的则是两款双核心产品,他们分别是已经投入生产的笔记本双核心Yonah和未来将上市的桌面双核心Smithfield。

● 新工艺完善——Venice

2005年4月,AMD的新工艺已经成熟,新的桌面CPU核心也应运而生。Venice核心是在Winchester核心的基础上演变而来,其技术参数和Winchester基本相同:一样基于X86-64架构、整合双通道内存控制器、512KB L2缓存、90nm制造工艺、200MHz外频,支持1GHyperTransprot总线。Venice的变化主要有三方面:一是使用了Dual Stress Liner (简称DSL)技术,可以将半导体晶体管的响应速度提高24%,这样是CPU有更大的频率空间,更容易超频;二是提供了对SSE-3的支持,和Intel的CPU相同;三是进一步改良了内存控制器,一定程度上增加处理器的性能,更主要的是增加内存控制器对不同DIMM模块和不同配置的兼容性。此外Venice核心还使用了动态电压,不同的CPU可能会有不同的电压。

Venice核心的Athlon 64很快成为当时市场上最热销的AMD处理器之一,由于使用了新的DSL工艺,Venice的主频可以轻松的大幅提升。在超频爱好者手中,Venice核心的Athlon 64又是一块宝贝,大家普遍使用了300MHz外频,主频能达到3.0GHz的Athlon 64也越来越多。

● 单核心极限——SanDiego

还是在2005年4月,AMD在Venice核心基础上推出了SanDiego核心。SanDiego核心与Venice一样是在Winchester核心的基础上演变而来,其技术参数和Venice非常接近,Venice拥有的新技术、新功能,SanDiego核心一样拥有。AMD公司将SanDiego核心定位到顶级Athlon FX之上,这是Athlon FX的第二次核心升级,名称上升到Athlon FX 59,频率达到3GHz。我们可以将SanDiego看作是Venice核心的高级版本,只不过缓存容量由512KB提升到了1MB。当然由于L2缓存增加,SanDiego核心的内核尺寸也有所增加,从Venice核心的84平方毫米增加到115平方毫米,同时也带来一些功耗提高,当然价格也更高昂。

在2005年2月,一直对桌面64位应用持消极态度的Intel,终于在64位软件的推动下发布了Pentium 4 6XX系列CPU。Intel在Prescott架构基础上向Pentium 4添加了EM64T以及节能技术和硬件防毒,二级缓存也增长为2MB,频率从3.0GHz到3.6GHz,并发布了3.73 GHz主频、1066MHz前端总线的至尊版。在媒体搭建的测试平台上,3.73 GHz的64位Pentium 4终于在与Athlon FX 55的竞争中取得少数胜利,但它的对手应该是Athlon FX 59。

● 双核时代开始——Manchester与Toledo齐飞

SanDiego核心从规格和频率方面都为AMD创造了单核的奇迹,它也是AMD单核心CPU的性能终结者,接下来AMD也拿出了准备已久的双核心产品——AMD Athlon64 X2。但是首先发布的还是面向服务器领域的双核Opteron。

AMD准备在2005年4月21日发布双核Opteron。Intel得知这一消息后,为了不输在起跑线上,提前在4月18日发布了其双核产品Smithfield核心Pentium D。

2005年05月31日,AMD在台北电脑展(Computex 2005)上以“在更短的时间内完成更多任务”为主题发布桌面级双核产品Athlon64 X2。迟到的AMD带给人们的是更强大的性能和更先进的核心设计,带给Intel Pentium D的则是美梦的破碎。

多核心CPU的实现看似简单,但Intel与AMD却在技术方面分道扬镳。

从集成的角度来看,业界通常把多处理器计算机系统分为“紧耦合”和“松耦合”两种形态。一般我们将通过将多台计算机组成集群(Cluster)的方式来增加计算机系统处理器数量以提高计算性能的做法就是一种相对比较宽松的耦合。这样的计算机群有各自独立的CPU、内存、主板和显卡等周边配件;而通过SMP(对称多处理器)架构来增加处理器数量的方式就是一种紧耦合,比如一板双芯的方式就是一种比较典型的SMP计算机耦合方式。假如,我们将2个处理器放在一个芯片内,或者一块基板上,这就是一种更加紧密的耦合状态,业界将它称为CMP(单芯片多处理器)架构。简而言之,AMD和Intel新推出的双核心处理器都符合CMP的逻辑架构,他们之间并无详细的区分。

下面给大家带来的是AMD和Intel双核CPU技术示意图:

AMD Athlon 64 X2处理器与Intel双核P4的最大不同在于仲裁通信系统的位置。AMD的双核心技术使用的是一种特别的架构,AMD内部称其为Direct Connect architecture。与Pentium D相比,它增添了“系统请求接口”(System Request Interface,SRI)和“交叉开关”(Crossbar Switch)。它们的作用是对两个核心的任务进行仲裁、及实现核与核之间的通信。AMD的两个核心会把请求放在系统请求对列(SRQ)中,当资源允许的时候,会把任务分配给合适的核心去处理,整个过程都在CPU内部完成,系统性能也就此大大提高。同时也可以让每个核心都有独享的I/O带宽、避免资源争抢,实现更小的内存延迟,并提供了更大的扩展空间,让双核能轻易扩展成为多核。而Intel的双核产品就没有按照这样的思路来进行设计,它们将任务分配控制单元和仲裁单元从CPU中脱离出来,放在北桥芯片中。因此Intel的双核处理器也被称为是“两颗处理器在一条前端总线上的简单复合”。

AMD认为Intel仅仅是将2个完整的处理器核心简单的集成在一起而已,它们非但没有直接受到任务仲裁器的控制,而且还同时连接到一条带宽有限的前端总线上。这样的设计架构势必会造成2个处理器核心单元抢夺总线资源,从而影响性能。AMD当初坚持将内存控制器整合在CPU中,就是出于“距离越短,速度越快”的原则,从而降低延迟,提高系统效率。由此我们可以看出优秀的架构设计对AMD在以后的战斗中胜利奠定了坚实的基础。目前业界也公认AMD在芯片的连接技术中的确领先,即使是Conroe,在这方面依然不是具有HyperTransport总线的Athlon64的对手。

Manchester与Toledo就诞生在这个背景下。Manchester是AMD于2005年4月发布的在桌面平台上的第一款双核心处理器的核心类型,是在Venice核心的基础上演变而来,基本上可以看作是两个Venice核心通过上述技术耦合在一起。Manchester核心采用90nm制造工艺,支持1000MHz的HyperTransprot总线,全部采用Socket 939接口,两个内核都独立拥有512KB的二级缓存。不过,由于Manchester核心仍然是两个内核的缓存相互独立,从架构上优于Smithfield核心Pentium D,但不如以Yonah核心的共享缓存技术Smart Cache。但在与Pentium D的对抗中,Manchester取得了AMD期待也预计中的圆满胜利。

Toledo是AMD于2005年4月在桌面平台上的新款高端双核心处理器的核心类型,它和Manchester核心非常相似,差别在于二级缓存不同。Toledo核心采用90nm制造工艺,支持1000MHz的HyperTransprot总线,全部采用Socket 939接口。Toledo核心的两个内核都独立拥有1MB的二级缓存,Toledo核心与Manchester核心相比,除了每个内核的二级缓存增加到1MB之外,其它都完全相同,可以看作是Manchester核心的高级版,AMD同样利用它打造了Athlon FX 6X系列。

但是不要忘记,Pentium D的单个核心使用的还是NetBrust微架构,初期的双核之战实际上是将AMD原有的胜利再次演绎,而Athlon 64的另一个对手早已在Intel酝酿中。

● AM2新接口应用——Orleans与Windsor直面Conroe

先让我们回顾一则新闻:2006年3月7日,国外知名硬件网站Anandtech抢先放出了Conroe处理器的照片以及测试成绩,结果令人乍舌:Conroe 2.66GHz在与超频到2.8GHz Athlon 64 FX-60的对抗中全面胜出,最大领先幅度达到40%以上,平均也有20%!消息一出,业界一片哗然。尽管当时出现了各种声音,但Anandtech的测试结果可信度还是相当高的,如果大家有兴趣,可以查找Conroe 所使用的Core微架构的相关说明,这里不再提及。

Orleans与Windsor这次要面对的正是这样的强敌,Conroe所使用的不再是AMD熟悉的NetBrust微架构,而是巨人Intel在经历了痛苦和颠覆之后重新思考,精心设计的全新Core微架构,它拥有诸多优势,使Athlon 64的领先被彻底终止。但AMD也有了新的微架构计划,测试成绩的公布标志着AMD在新架构出世之前,必须使用Athlon 64继续反击。

Orleans是2006年5月底发布的第一种Socket AM2接口单核心Athlon 64的核心类型,其名称来源于法国城市奥尔良(Orleans)。它采用成熟的90nm制造工艺,支持虚拟化技术AMD VT,1GHz HyperTransport总线,二级缓存为512KB,最大亮点是支持双通道DDR2 667内存,这是其与只支持单通道DDR 400内存的Socket 754接口Athlon 64和只支持双通道DDR 400内存的Socket 939接口Athlon 64的最大区别。

如图,笔者正在是用的Orleans核心Athlon 64 3000+,很轻松地将外频提到260MHz。Orleans核心Athlon 64同样也分为TDP功耗62W的标准版(核心电压1.35V左右)和TDP功耗35W的超低功耗版(核心电压1.25V左右)。除了支持双通道DDR2内存以及支持虚拟化技术之外,Orleans核心Athlon 64相对于以前的Socket 754接口和Socket 940接口的Athlon 64并无架构上的改变,但是它继承了前辈们所有优点,尤其是在与Intel的斗争中,性价比更高。

Windsor是2006年5月底发布的第一种Socket AM2接口双核心Athlon 64 X2和Athlon 64 FX的核心类型,其名称来源于英国地名温莎(Windsor)。Windsor核心定位于桌面高端处理器,采用90nm制造工艺,支持虚拟化技术AMD VT,仍然采用1GHz HyperTransport总线,二级缓存方面Windsor核心的两个内核仍然采用独立式二级缓存,Athlon 64 X2每核心为512KB或1024KB,Athlon 64 FX每核心为1024KB。

Windsor核心的最大亮点是支持双通道DDR2 800内存,这是其与只支持双通道DDR 400内存的Socket 939接口Athlon 64 X2和Athlon 64 FX的最大区别。Windsor核心Athlon 64 FX目前只有FX-62这一款产品,其TDP功耗高达125W;而Athlon 64 X2则分为TDP功耗89W的标准版(核心电压1.35V左右)、TDP功耗65W的低功耗版(核心电压1.25V左右)和TDP功耗35W的超低功耗版(核心电压1.05V左右)。

在测试中,其性能不敌Intel于2006年7月底发布的Conroe核心Core 2 Duo和Core 2 Extreme。AMD从降低成本以提高竞争力方面考虑,除了Athlon 64 FX之外,已经决定停产具有1024KBx2二级缓存的所有Athlon 64 X2,只保留具有512KBx2二级缓存的Athlon 64 X2。在2007年6月,AMD再次发力将其90nm工艺的Windsor核心频率提高到3.0GHz,发布了迄今为止桌面CPU规格最高的Athlon 64 X2 6000+。

此外,面对Intel推出咄咄逼人的四核CPU,AMD为了填补空白把Opteron平台向下延伸,开发了AMD 4X4平台,名称为AMD Quad FX。它使用两个安装在同一主板上的具有3个HT总线的Egypt核心双核Opteron,如图。

这套顶级装备暂时最高可以使用到2颗Athlon 64 FX 74(双核心 3.0GHz主频)性能几乎追上了新的Core 2 Extreme QX6700,但由于CPU微架构的差异,AMD还是输了。而且其使用的实际上是一个双路CPU系统,并没有把4个核心集成在一个管芯内,统一封装。2007年AMD将会继续推出Athlon 64 FX 76,届时主频将达到3.2GHz。客观来说,Athlon 64相对于酷睿2所使用的Core微架构已显得老迈,酷睿2的真正对手应该是AMD下一代重新设计的核心——K8L(也被称作K10)。

● Athlon最后一搏——Brisbane

2006年12月5日,AMD位于德国的Fab 30工厂推出了65nm新工艺生产的Athlon 64 X2,最早上市的是4000+、4400+、4800+、5000+这4个型号。这次使用的65nm绝缘硅(SOI)源自此前的90nm低功耗SOI技术,充分利用了AMD在90nm功耗控制技术方面的优势,所以4款产品的最大TDP功耗全部控制在了65W,这批产品的核心名称就是Brisbane,这是Athlon时代的最后一款核心,同样向Intel挥出了有力一拳。在媒体实际测试中,AMD利用新核心再次将高功耗的帽子甩给了Intel的桌面酷睿2系列。

Brisbane拥有1.538亿个晶体管,同样采用AM2接口,功率65W,采用mPGA封装,配备1000MMhz前端总线,200外频,一级缓存上64K数据缓存+64K指令缓存,二级缓存512K*2。支持最高双通道DDR2 800内存,支持虚拟化技术和AMD VT,支持多媒体指令集(MMX、3D NOW!、SSE、SSE2、SSE3 ),核心温度比上一代产品下降了15%,功耗则只有90nm Athlon 64 X2的73.3%。

● Athlon时代结束之后

2007年,AMD的Athlon产品将走过最后一段路程,随着新品牌Phonom的登陆,Athlon品牌将会逐渐淡出市场。Phonom将继续沿用成熟的65nm工艺,同时针对Intel在2007年末首产45nm工艺产品,AMD将其65nm技术视为打击45nm的秘密武器。

如图,AMD 65nm PMOS器件中的应变层和嵌入式SiGe层。Semiconductor Insights公司的首席技术官Edward Keyes对AMD的65nm工艺做了深入分析,他认为AMD工艺的最大创新在于其增加晶体管驱动能力的移动增强技术,特别是双应变层技术的使用和相关技术的突破,使得AMD创造了一个具竞争力、高性能的65nm工艺,并为AMD微处理器未来的业务前景做了很好铺垫。到2007年中期,AMD预期其位于德国德累斯顿的Fab 36将完全转向65nm。

2007年对于AMD是至关重要的一年,市场需求在多种力量的推动下不断增长,对手也在疯狂的进攻,收复失去的市场份额,并把AMD一步步逼向绝路。AMD在此时一方面使用了降价等市场手段巩固市场,同时加速了配套芯片组的开发,打造出了AMD690G这样高性价比的平台。但最重要则是新核心的开发,K10相关信息已越来越多,它到底能带来多大的性能提升?我希望在这里对K10做一些简单的预览。

K10是AMD下一代CPU的架构,AMD声称其K8L架构四核心具备一系列“革命性设计”,其中最大的卖点是“原生”,另外还有每核心512KB二级缓存、共享2MB三级缓存、HyperTransport 3.0总线、增强型PowerNow省电技术、AMD-V虚拟化技术、领先的性能每瓦特指标等。

如图,K8L的一个单核图解

首先,K10将引入共享三级缓存,同时每个核心拥有自己的一级缓存和二级缓存。如果处理器请求的数据存在于一级缓存中,则直接载入;如果在任何一个二级缓存中,则直接或者通过交叉开关载入一级缓存,并将二级缓存中的原数据标记为无效,这也是AMD的独特设计;如果在三级缓存中,则数据载入后仍然存在,其他核心还能继续访问,从而实现共享。

K10的整合内存控制器(IMC)将有一些新特性,其将可以通过64-bit通道访问内存,使用ECC错误校验的话则是72-bit,这样可以令读取和写入数据同步进行,提高多核CPU在无序访问中的效率。而在CPU的超频性能方面,K8L将采用分离式能耗设计IMC也可以根据各个处理器核心独立自定频率和电压,这将令到玩家在超频时可以忽略内存的频率。而在多核心CPU的通信设计方面,K8L依然采用内部的交叉开关,全部在处理器之内完成,效率更高。

而在CPU最重要的功耗能耗设计方面,K10采用了一系列的新节能设计。K8L架构下,各个处理器可以运行在独立的频率,AMD称之为“P-States”,空闲的核心可以降低频率甚至完全关闭,负载的则全速运行。K10还将配备新的热传感器,以便改善过热保护。此外,对于分支预测能力和提升ICP的相关技术方面,新的K8L核心同样做出了很大改进。

K10系列CPU将全部被命名为Phonom,制造工艺也全部升级为65nm。最初确定了1个单核核心,2个双和核心,2个四核核心,但最近AMD取消了单核计划,Phonom将全部以双核、2.0GHz主频起跳。Athlon则会逐渐减产、淡化出市场。

最后要送给大家的是一张1554x1422像素的巨大的K10核心照片

第一个4年+第二个4年,我们一起回顾了这个Athlon带给我们的神话。几年之后,如果你偶尔在电子市场看到一颗Athlon,请记得收藏它,将它安放在一个漂亮的盒子中,或打个孔作为一个精美的挂件。但是不要忘记,Athlon这个光荣的代号,曾在芯片发展史上划出壮丽的一笔。

![linuex查看繁忙_[个人笔记] 关于linux的常见问题合集](/images/no-images.jpg)