配置时序

在sample中只需要设置为User时序即可,如下图:

用户时序的结构体:

typedef struct tagVO_SYNC_INFO_S

{

HI_BOOL bSynm; /* sync mode(0:timing,as BT.656; 1:signal,as LCD) */HI_BOOL bIop; /* interlaced or progressive display(0:i; 1:p) */HI_U8 u8Intfb; /* interlace bit width while output */HI_U16 u16Vact ; /* vertical active area */HI_U16 u16Vbb; /* vertical back blank porch */HI_U16 u16Vfb; /* vertical front blank porch */HI_U16 u16Hact; /* herizontal active area */HI_U16 u16Hbb; /* herizontal back blank porch */HI_U16 u16Hfb; /* herizontal front blank porch */HI_U16 u16Hmid; /* bottom herizontal active area */HI_U16 u16Bvact; /* bottom vertical active area */HI_U16 u16Bvbb; /* bottom vertical back blank porch */HI_U16 u16Bvfb; /* bottom vertical front blank porch */HI_U16 u16Hpw; /* horizontal pulse width */HI_U16 u16Vpw; /* vertical pulse width */HI_BOOL bIdv; /* inverse data valid of output */HI_BOOL bIhs; /* inverse horizontal synch signal */HI_BOOL bIvs; /* inverse vertical synch signal */

} VO_SYNC_INFO_S;

如SDK中默认的PAL时序:

{0,0,0, 288,22,2 ,720,132,12, 1, 288,23,2, 126,3, 0,0,0}

上面部分属性,与显示通道的总体控制寄存器DHDCTRL(0x205ca000)是对应的。

常用到的属性是如下:

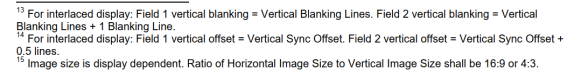

这里u16Vbb在隔行输出时是指顶场垂直消隐后肩,逐行输出时:垂直消隐后肩加垂直脉冲的宽度,单位是行。u16Vfb与u16Vbb对应,指的是前肩,两者加在一起的和应该一个定值的。u16Hbb是水平消隐后肩,u16Hfb是水平消隐前肩,单位为像素,两者加起来的和也应该是为一定的值。所以我们一般可以通过修改这两对值,来实现画面在一定的范围内,在显示器上的上下左右移动。可以通过接口配置,也可以直接修改寄存器(Vbb和Vfb与DHDVSYNC寄存器0x205ca004对应,Hbb和Hfb与DHDHSYNC1寄存器0x205ca008和DHDHSYNC2寄存器0x205ca00c对应)。

u16Bvbb指隔行输出时,底场垂直消隐后肩,u16Bvfb指隔行输出时,底场垂直消隐前肩,单位为行。这里注意,如果是隔行输出,修改了顶场图像的前后肩,则应该对应修改底场图像的前后肩,否则可能出现图像抖动。

以1080i0HZ为例说明个别参数:

底场垂直消隐后肩为垂直消隐+1,底场垂直消隐前肩为垂直消隐前肩,如下图:

垂直的有效行数等于垂直后肩有效行数,水平有效像素数为1920,底场水平有效像素数为 == 水平像素数-空白像素数)/2 + 偏移像素数, 即((1920-280)/2 +88),如下图

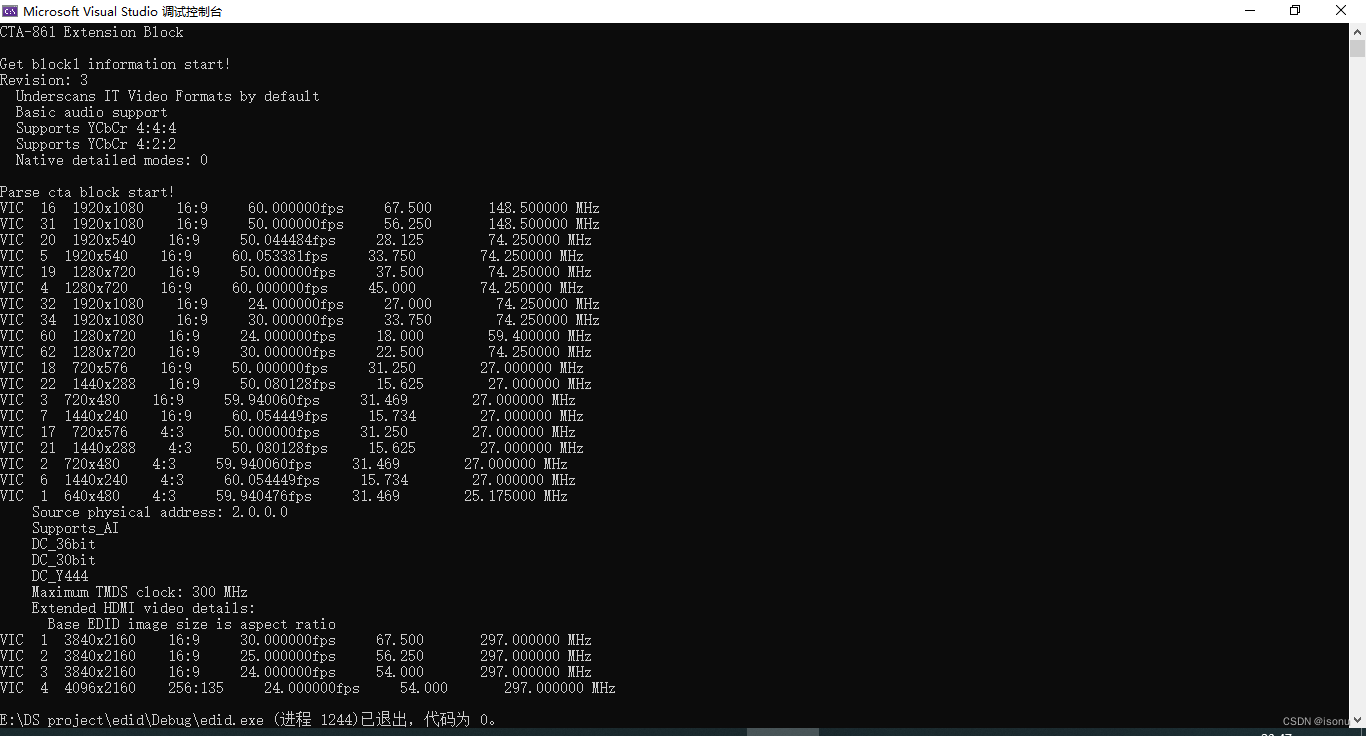

2、配置时钟

我们以3531为例,在一些特殊分辨率,像640x480@60,在vo设备中没有支持这个时序,但是HDMI有支持这个时序,所以可以用vo的用户时序来实现,只需要配置好上吗的User 时序和HDMI后,配置相应的vo的时钟。就可以正常输出。

表3-3 Hi3531 PLL 与各功能模块对应关系

这里可以看到,对于VDP模块,是由VPLL0或VPLL1来分配时钟。其中注意的是VPLL1会2分频后作为VDP HD/HDMI源时钟

一、这里,首先需要确认的是,当前的芯片,HDMI 时钟源选择。

例如,跑./sample_vio 0 读取寄存器0x20030038,结果如下:

值为:0x02017cfe

对应的第22位的值为0,所以此HDMI时钟选择,为HD0

对应的第17到19位的值为000,所以此HD0的时钟选择为VPLL1 DIV2时钟

所以如果需要配置的时钟为VPLL1。

二,计算VPLL1各个寄存器的值

Hi3531芯片手册中,表3-4列出了方法,这里我举一个例子

以配置VPLL1 为例,VPLL1 输出FOUTPOSTDIV 的2 分频给VDP 模块。

最终的VO时钟是FOUTPOSTDIV = FOUTVCO / (pstdiv1 x pstdiv2);

FOUTVCO = 24 x (fbdiv + frac / 2^24) /refdiv

pstdiv1、pstdiv2、fbdiv、frac和refdiv的值,都将通过配置进寄存器。

这里,refdiv为分频系数,像在配置VPLL1的时候,文档中写到二分频后作为VDP HD/HDMI源时钟。所以refdiv为2.

FOUTVCO的值有要求,应该大于等于800MHz,小于等于2.4GHz。

而frac一般都配置为0

所以需要进行凑的数,就是fbdiv、pstdiv1 和 pstdiv2。

这三个变量的意义如下:

PERI_CRG4(0x20030010)寄存器的

和PERI_CRG5(0x20030014)寄存器的

由上面的值得知,我们在搭配的时候,pstdiv1 和 pstdiv2的取值范围是0到7.

例如当HDMI需要输出640x480@60的时候,需要的时钟是50.4M,

FOUTPOSTDIV = (24 x (fbdiv + frac / 2^24) / refdiv) / (pstdiv1 x pstdiv2)

50.4M = (24 x (84 + 0 / 2^24) / 2) / (4 x 5)

所以fbdiv = 84、frac = 0、refdiv = 2、pstdiv1 = 4,pstdiv2 = 5.

综上,修改的寄存器值为:

将地址为0x20031010的值修改为0x25000000,

地址为0x20030014的值修改为0x006C2054。

这样就配置出了640x480的时钟。

详细见网址:

https://blog.csdn.net/huangyangquan/article/details/77487626

https://www.cnblogs.com/kongqiweiliang/p/3243610.html

https://wenku.baidu.com/view/331f712ca22d7375a417866fb84ae45c3b35c208.html