AG10KL144是一款超低成本的FPGA,可以替代ALTERA的EP4CE10。目前越来越多的工业客户选择AG10KL144。

AG10KL144是一款超低成本的FPGA,逻辑资源有10KLE,可以替代ALTERA的EP4CE10E22I8N。价格远低于其他品牌同等资源的FPGA器件。目前越来越多的工业客户选择AG10KL144,提高产品的综合性价比。

我司是AGM的授权代理商,拥有强大的技术支持团队,AGM原厂也对重点客户进行一对一的支持。

我司可以为工程师提供技术支持服务,如需要设计选型等,我们可以给提供选型指导。

AGM是国内领先的FPGA厂商,AGM的部分器件可以直接PIN TO PIN兼容ALTERA和LATTICE的FPGA或者CPLD。

AGM的SOC器件已经广泛应用于应用环境恶劣的LED户外屏市场,性能及成本优势广受客户好评。AGM很多器件的价格不到竞争对手的2/3,可以为用户提供超有竞争力的价格支持。

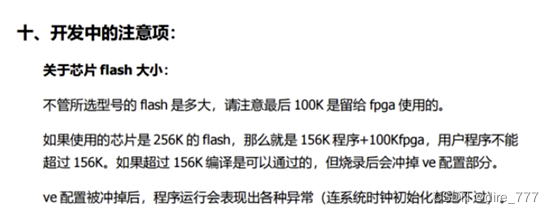

AGM FPGA之AG10K 系列的开发建议二

- PLL

AGM FPGA在配置成功时,PLL已经完成锁定,lock信号已经变高;如果原设计中用lock信号输出实现系统reset的复位功能,就不能正确完成上电复位;同时,为了保证PLL相移的稳定,我们需要在PLL启动后做个延时的复位,设计中可以参考下面Verilog代码,这里需要PLL的areset或pfdena引出,通过复位信号控制。

reg [5:0] reset_init = 6’b0 /* synthesis syn_preserve = 1*/;

wire init = reset_init[5];

always @ (posedge inclk) begin

if (!init) begin

reset_init <= reset_init + 1’b1;

end

end

PLL inst (

.inclk(inclk),

.areset(!init),

.pfdena(init),

…

);

-

Flash管脚

如果在设计中对配置FLASH进行读写,则要在Quartus II中把4个SPI配置管脚设置为“Use as regular I/O”。 -

上升和下降沿采样建议

如果在设计中用时钟下降沿采集的,而他的上一级是上升沿,这样两者之间就只有半个时钟period. 这样时序会紧张, 建议用同沿。 -

VccINT

如果FPGA的资源利用率达到90%以上,且时序要求较高,建议把1.2V的VccINT电压,升高到正常电压范围的1.25V,会有效提高FPGA性能和稳定性。 -

FLASH编程文件

烧写配置用SPI FLASH,使用XXX_master.bin,可通过FLASH编程器烧写。如使用其它兼容Altera POF文件的烧写工具,需注意Altera文件MSB-LSB为反向,需倒置后才可正确烧写。 -

AS在线烧写FLASH

如果使用USB-Blaster通过AS接口在线烧写配置用SPI FLASH,由于AG10K的DCLK、nCSO、ASDO管脚并未输出三态,因此需分别串接1KΩ电阻,使得USB-Blaster驱动能力高过这些管脚的输出能力,且DCLK时钟降低频率,即可实现正常烧写和配置。

如FPGA有JTAG接口,则可直接通过Supra软件烧写XXX_master.svf或XXX_master.prg文件到已连接的SPI FLASH中,无需通过AS接口,更为方便。 -

CLK输入管脚

CLK专用输入管脚,没有内部上拉电阻,所以在悬空没有输入状态时,会得到0的电平数据。这和Altera EP4C的高电平结果不同。如果正常输入时钟或信号,则没有影响。 -

Latch 锁存器

支持 latch, 但建议设计不用 latch, 异步电路时序不容易分析操作,建议不使用。 -

conf_done

所有 fpga逻辑必须发生在fpga配置完成之后(conf_done为高),否则fpga无法稳定接受开始工作。

欢迎加Q或者weixin(同号): 150–615-^255 或者联系#0755-,2780,-9180(去掉中间的标点符号) 咨询交流。