概述

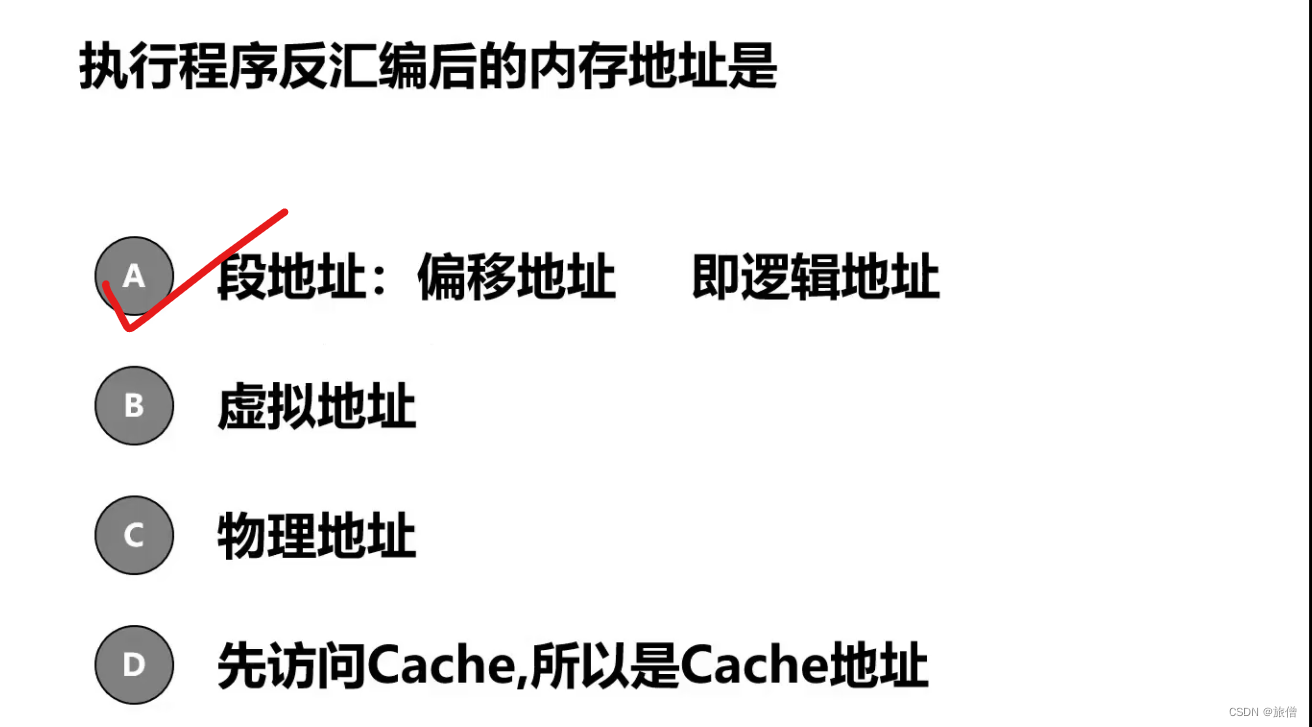

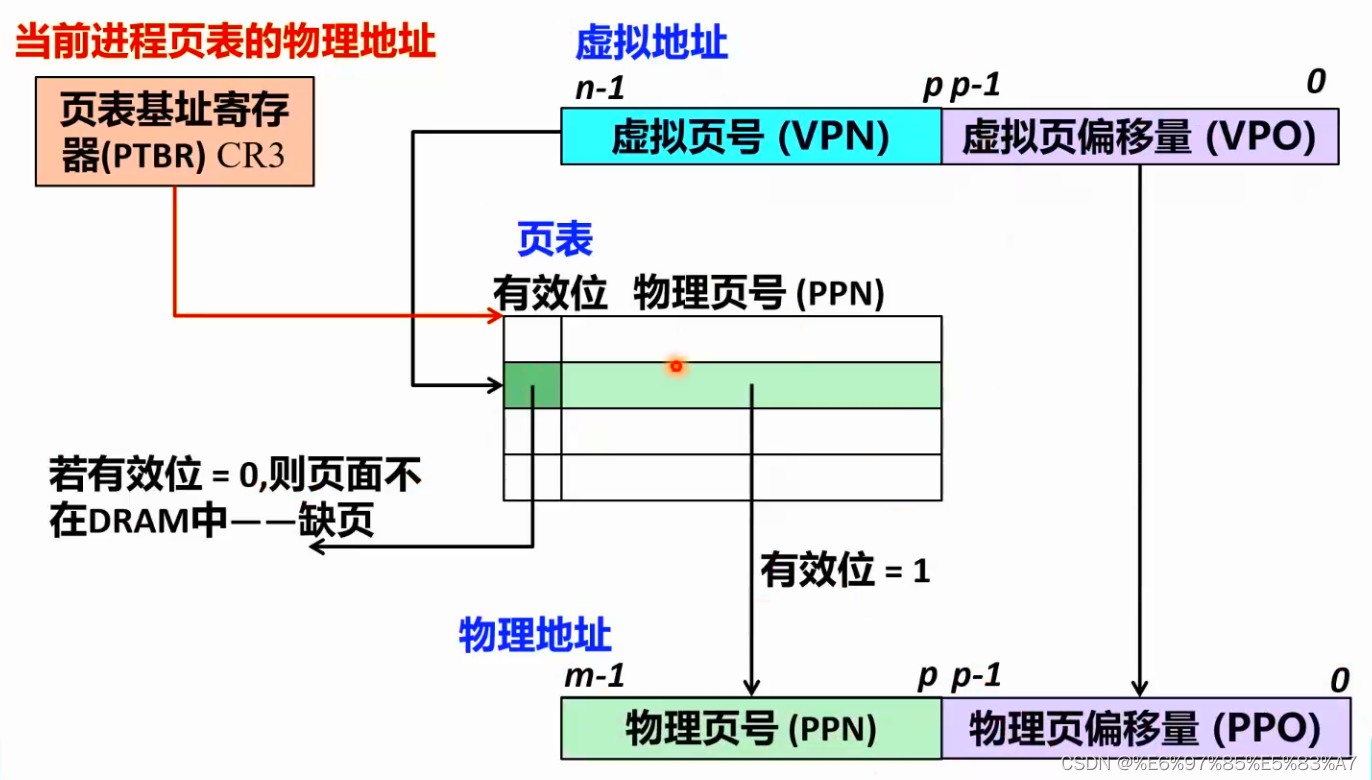

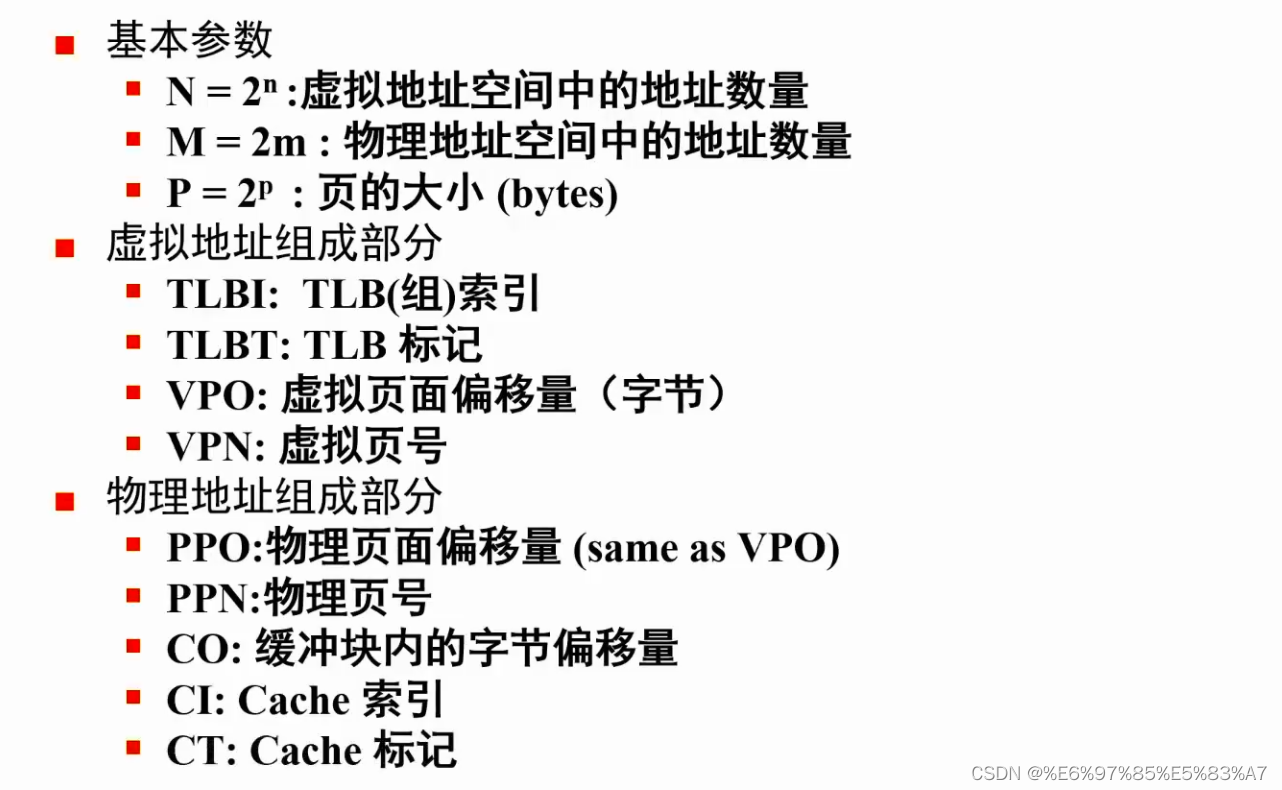

程序是存放在虚拟地址空间中,运行是在物理空间中,如何进行转换是虚拟内存需要研究的问题。

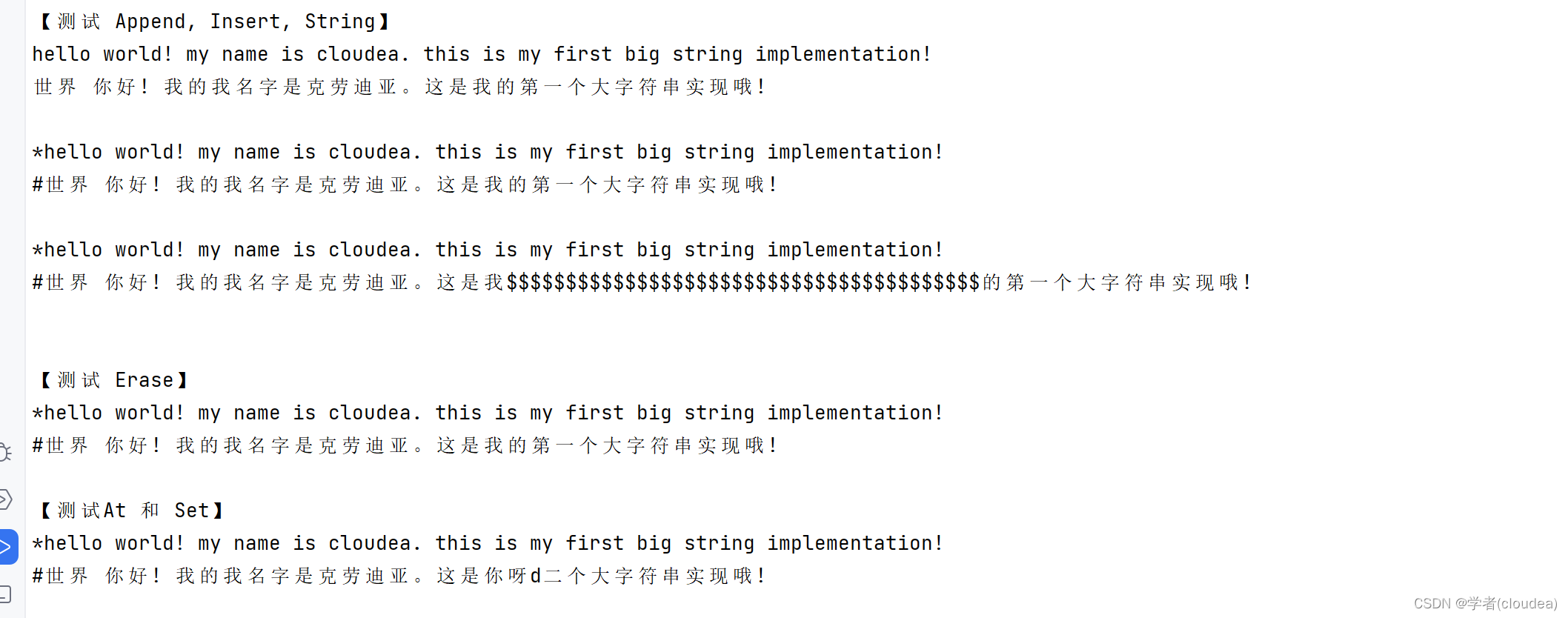

完成逻辑地址到虚拟地址再从虚拟地址到逻辑地址映射的机构叫MMU

两个部件 段式管理和页式管理

之前有提到,cache的管理是通过cache映射表,但是虚拟内存到物理内存每一次映射都需要一次翻译的过程,如果每一次都查表的话,速度就会降下来,所以引入数据结构页表 页表是DRAM是放在内存里

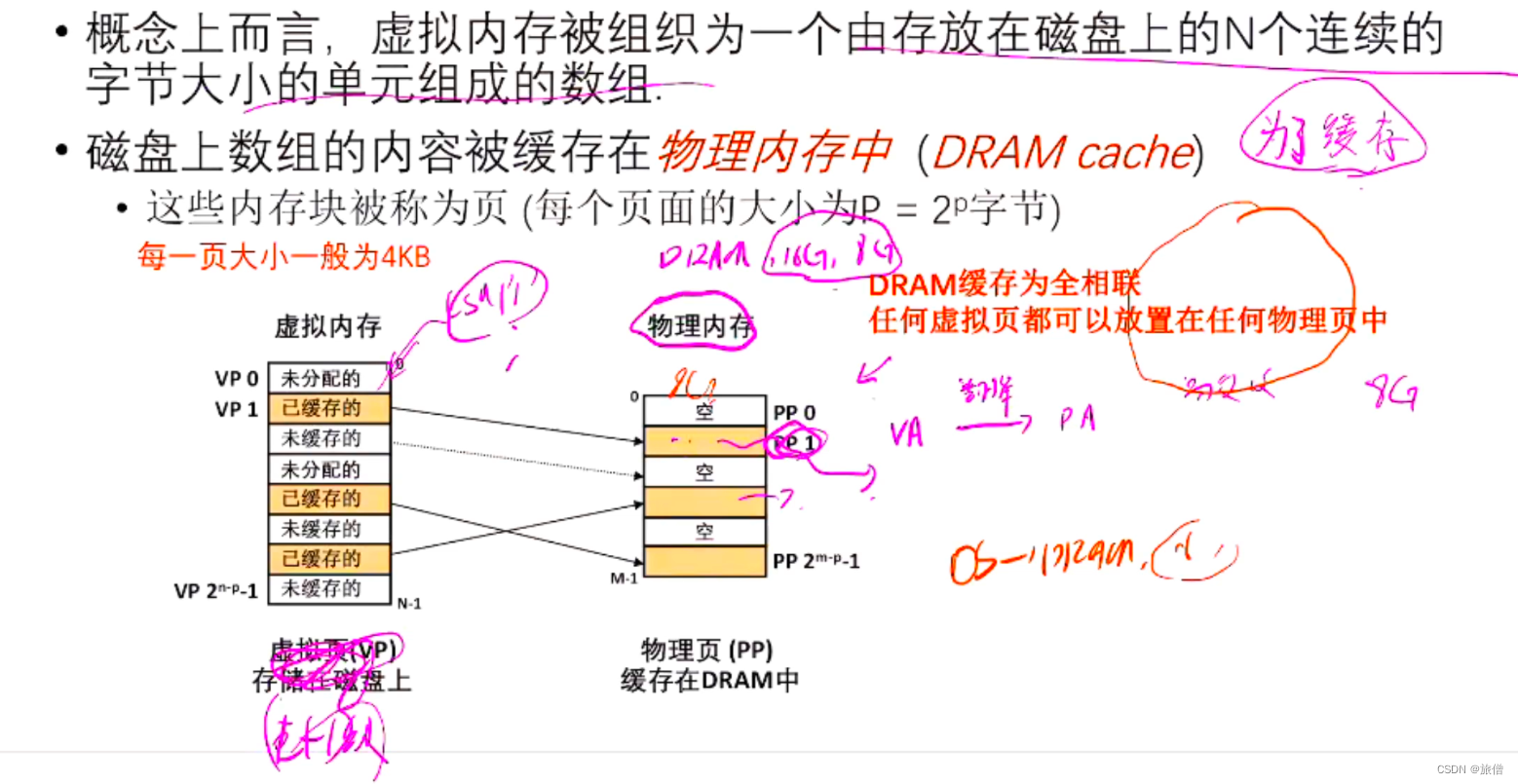

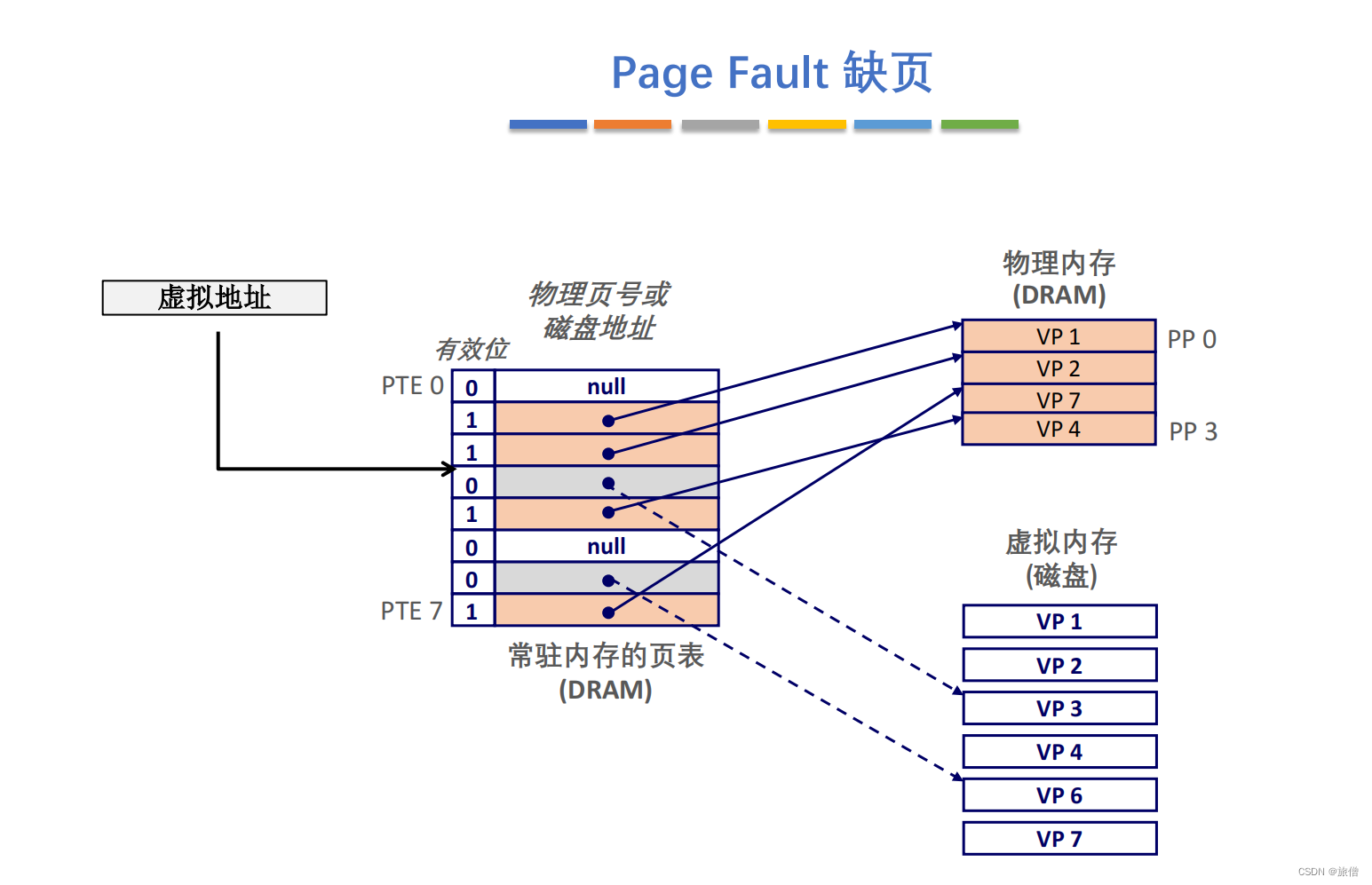

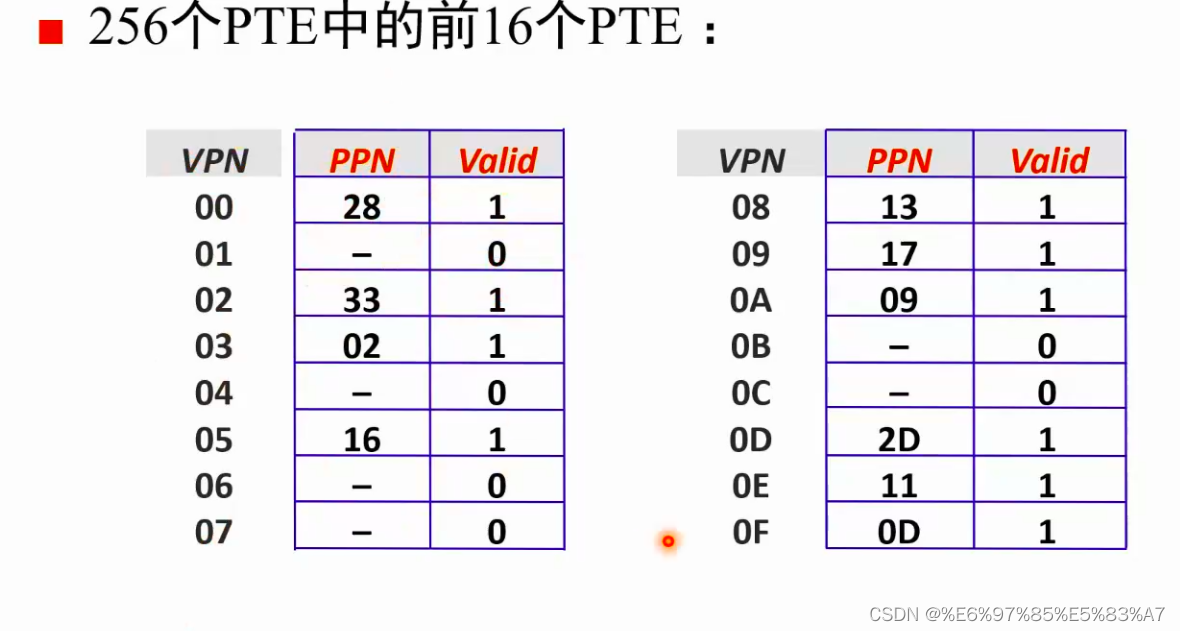

三种状态已缓存 未缓存 未分配 DRAM是全相联映射 ,页表是存放在内存中

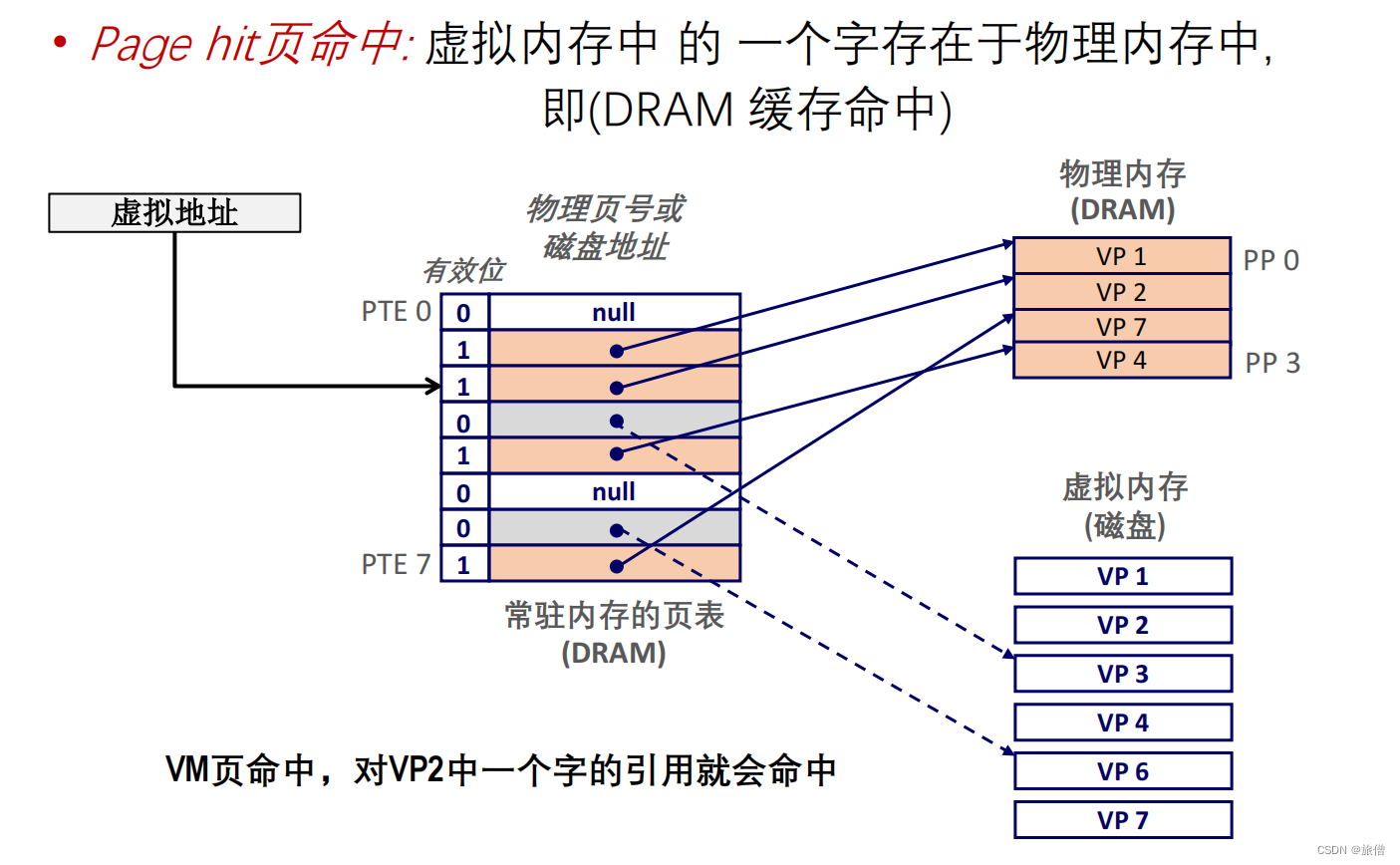

页命中 有效位是1

CPU内部使用的是虚拟地址

几个基本概念 页表条目 PTE 有效位 页表 页表是存放在CPU中 存储芯片是DRAM

又是程序局部性救了我们

每个进程可以共享物理空间

程序运行时不用真正去执行,建立好映射,这样程序可以直接运行在虚拟空间上

页面的保护

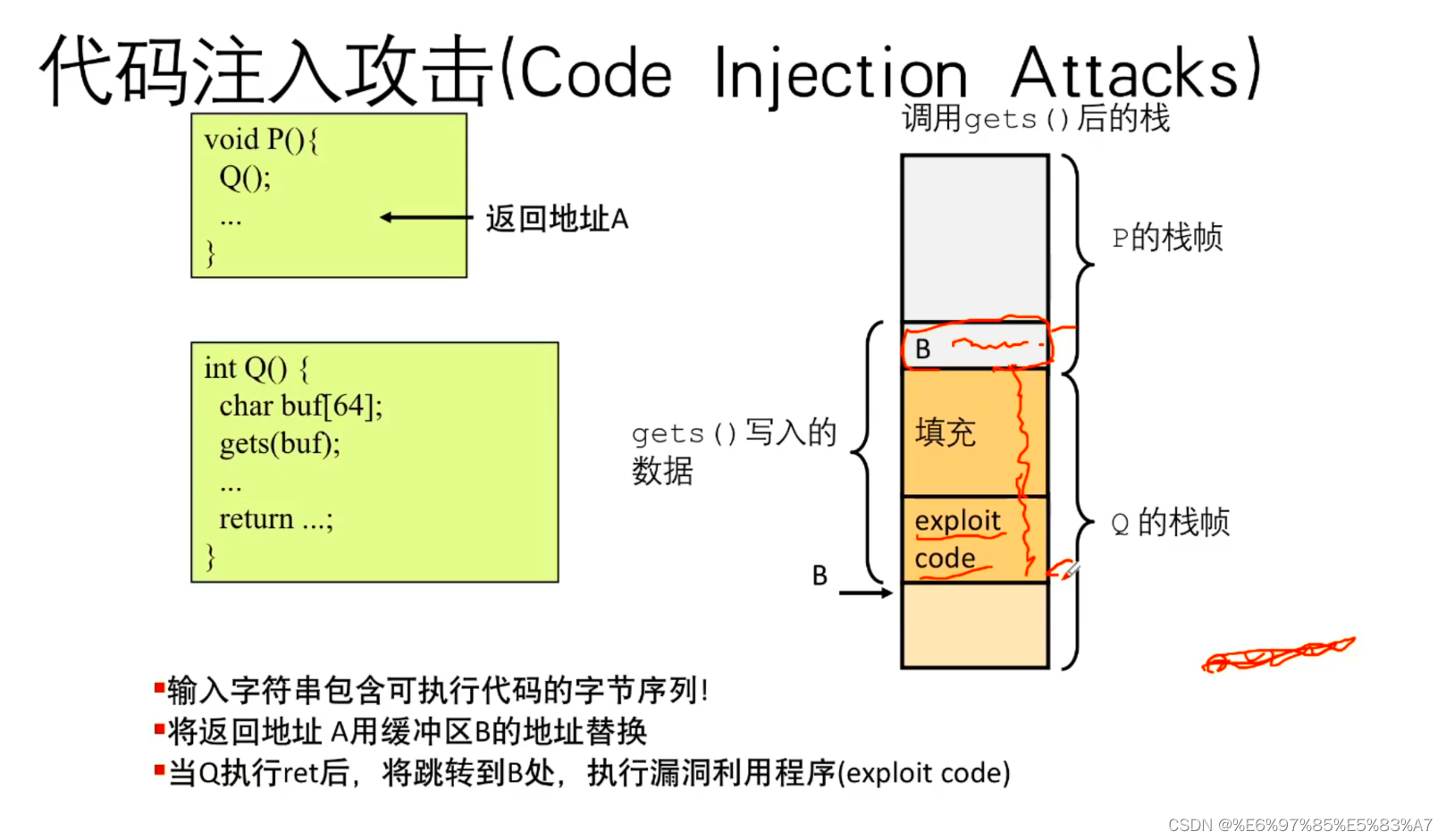

首先我们回顾之前的缓冲区溢出攻击

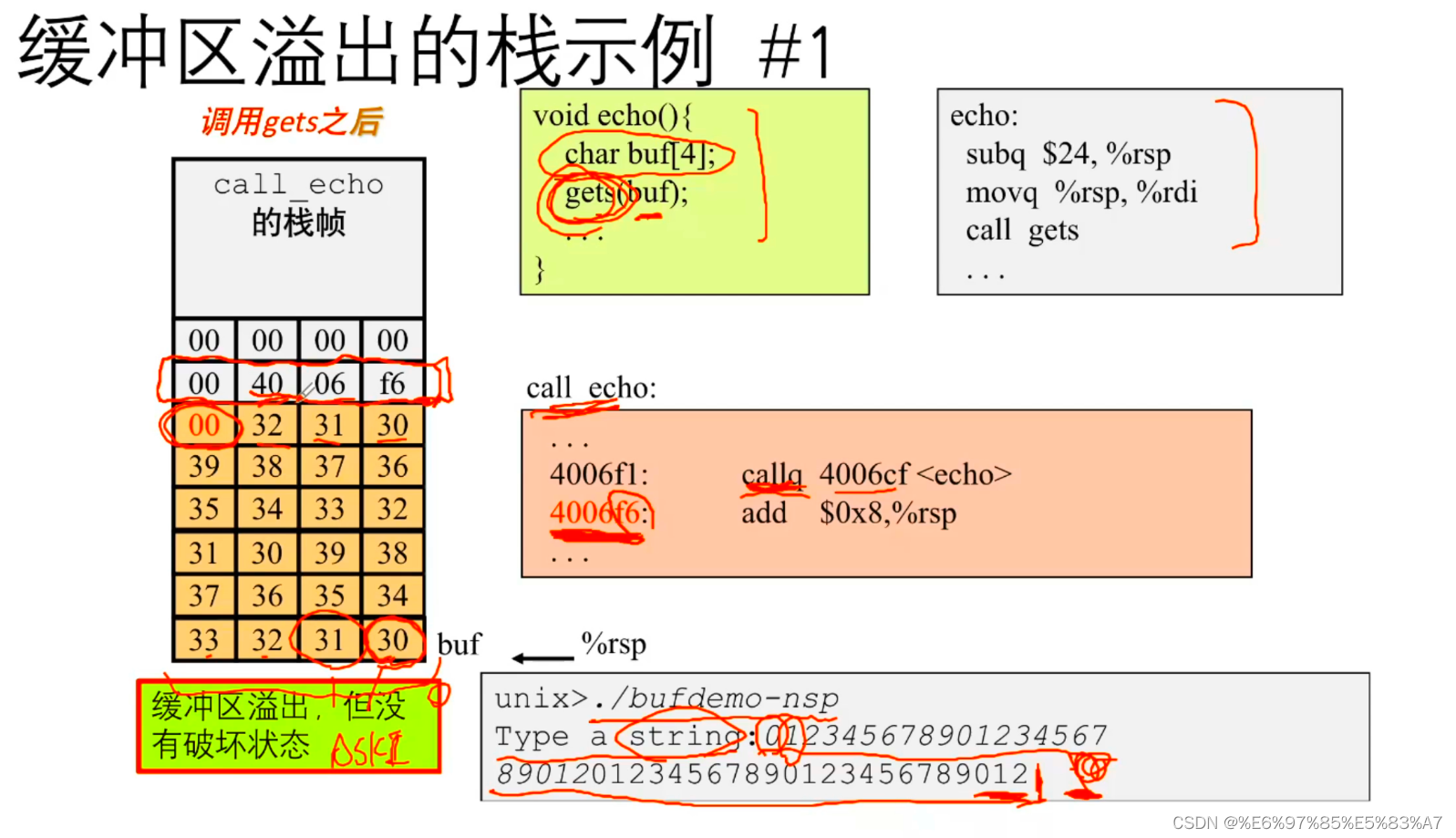

这个函数的目的是读取缓冲区的数据将其存入栈中,地址在栈中是以小端法的方式储存

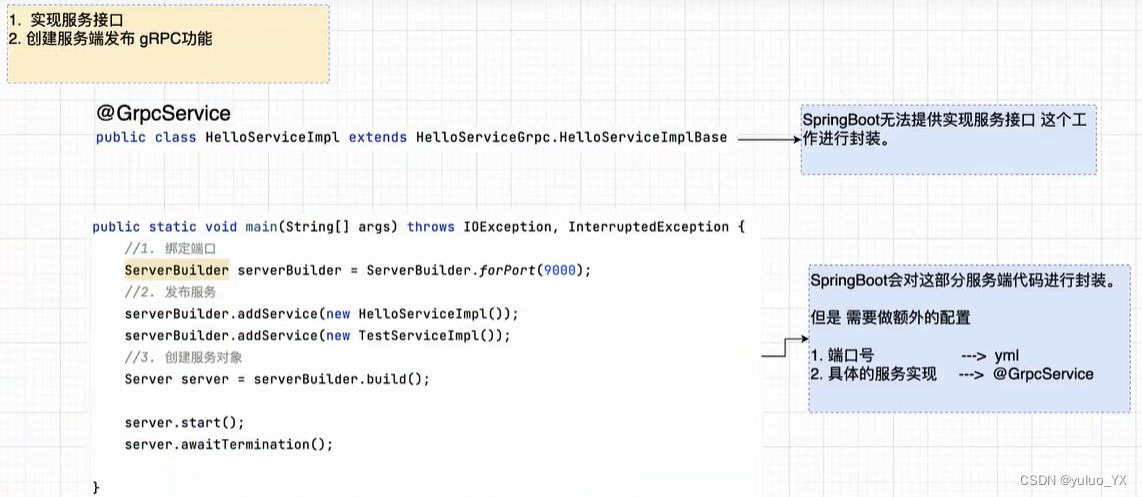

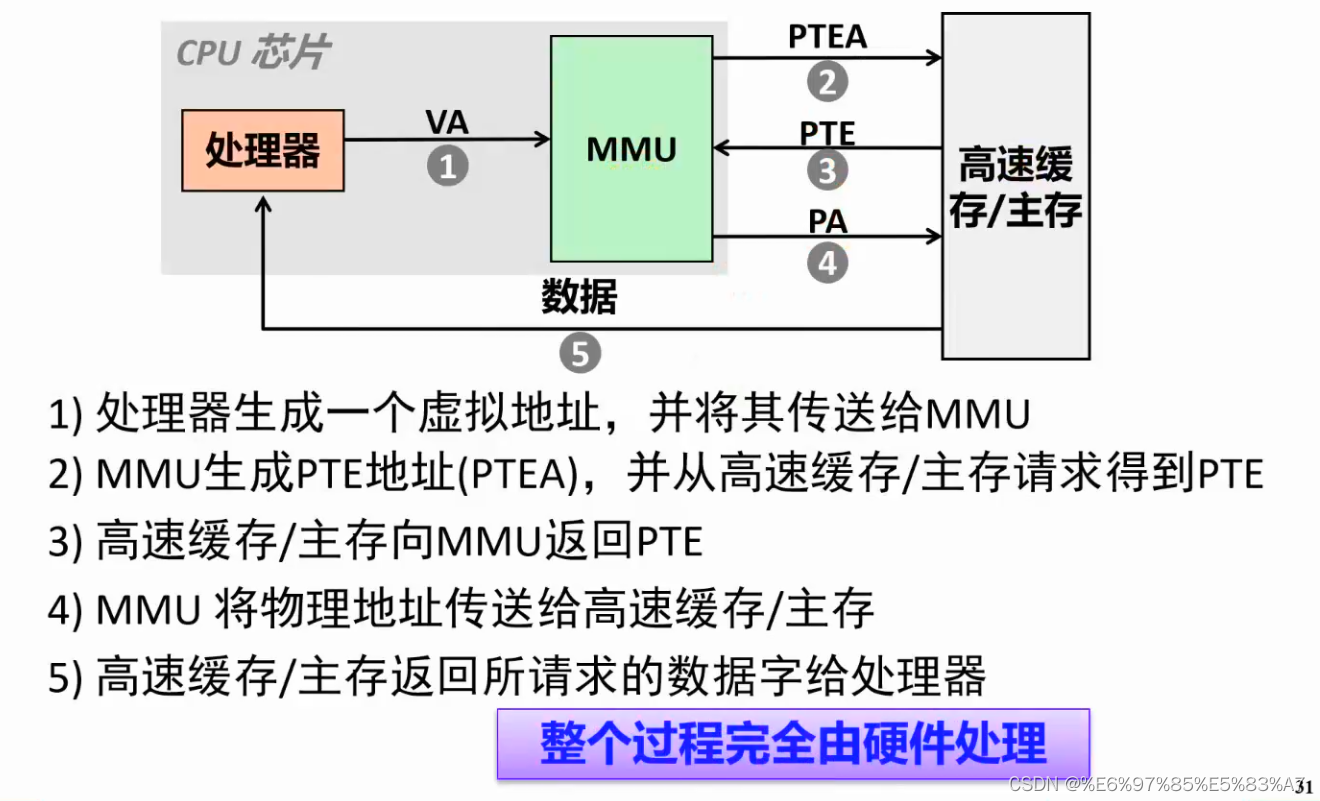

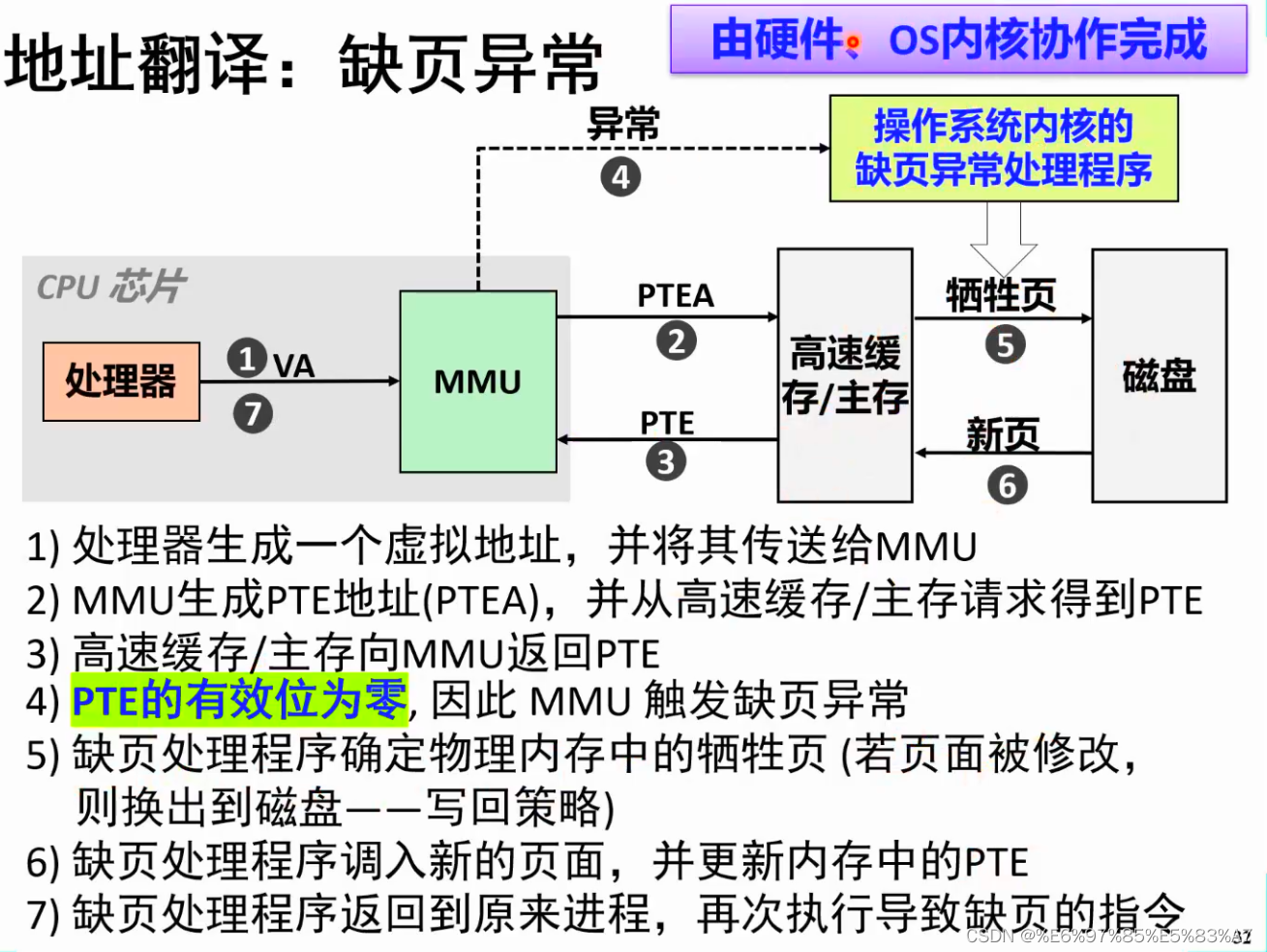

地址翻译过程

命中地址翻译完成过程,因为都是由硬件来完成所以速度很快。

PTEA是物理地址 知道PTA就知道PPN,又因为VPO和PPO是相等的 所以做一下拼接就变成乐物理地址

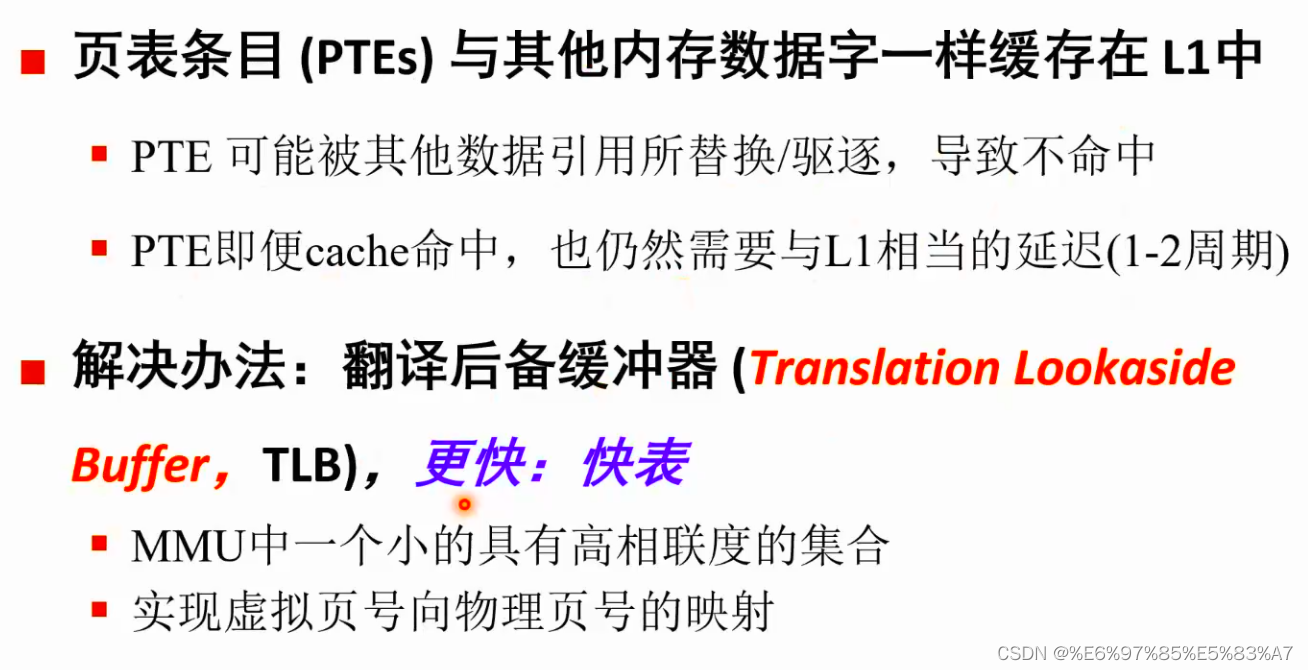

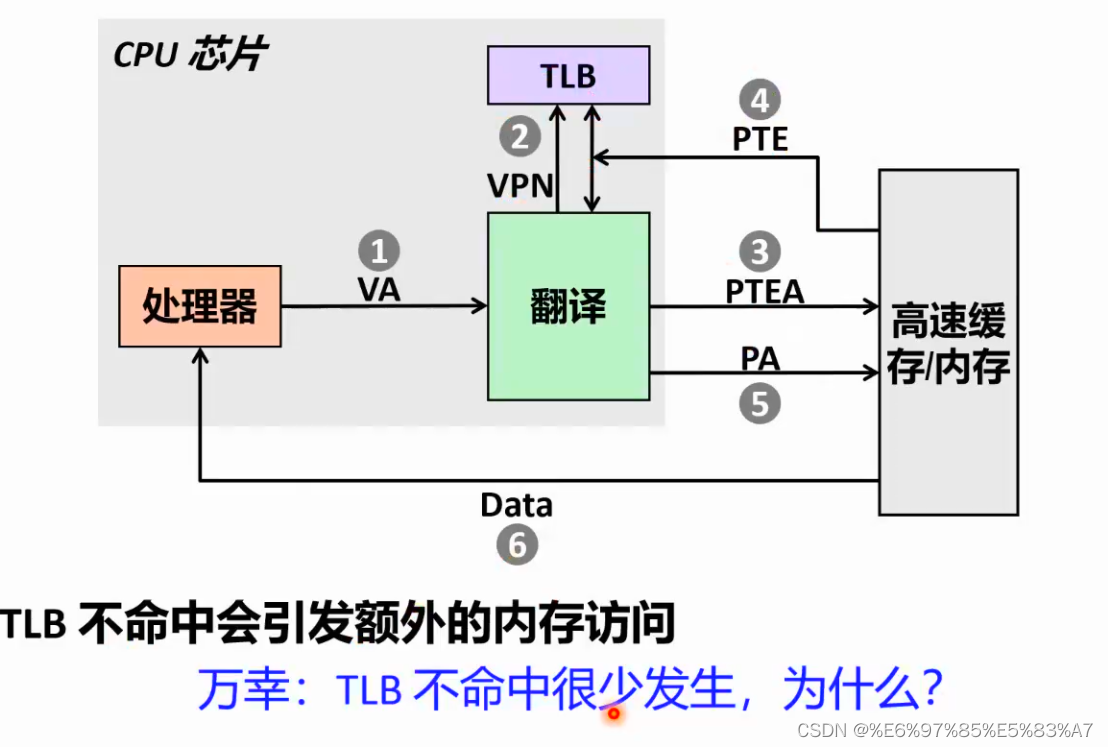

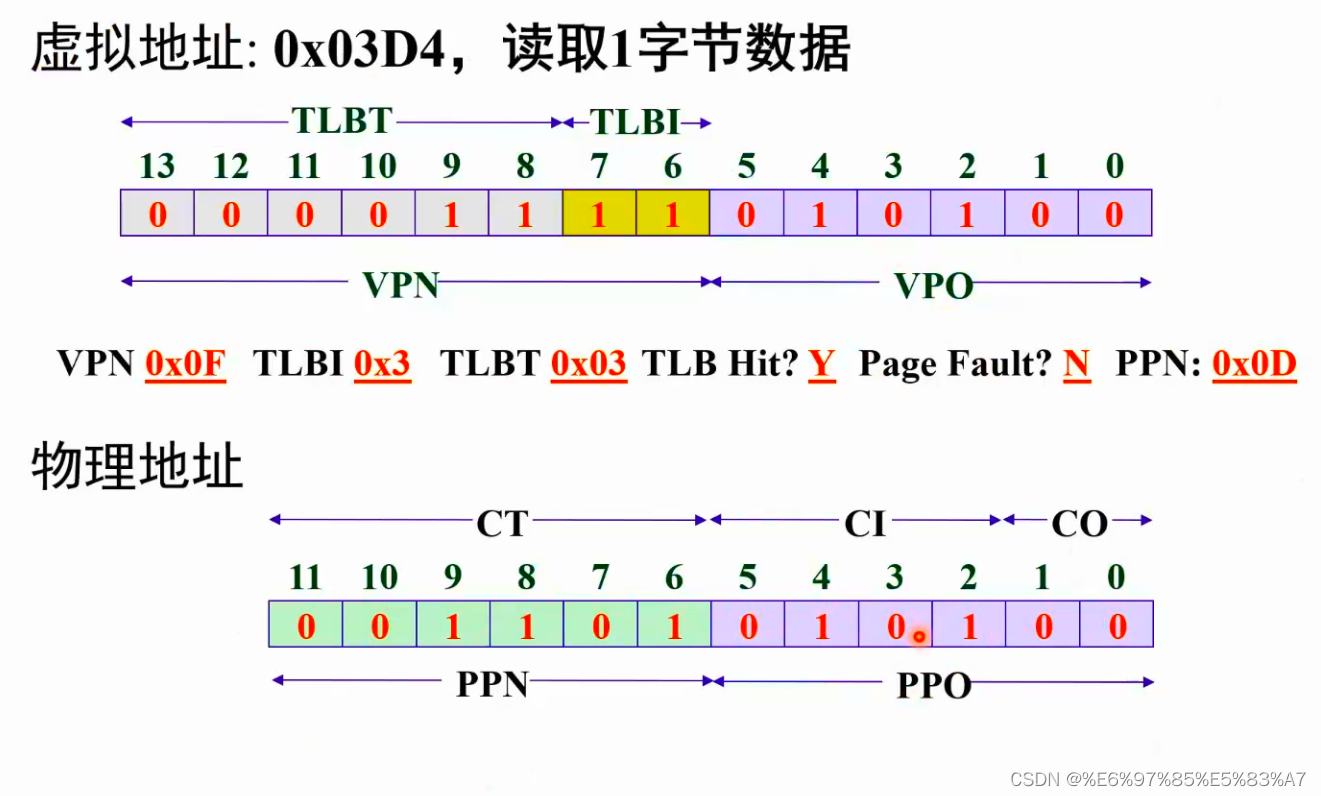

利用TLB快表加速存储器的访问

通过上图可以知道 无论页面是否命中 都要访问两次MMU 也就说至少要访问两次缓存cache,而主存的速度显然没有cache中的L0速度快,为了加快访存速度,我们引入硬件结构快表,

程序的局部性 页表存的数据是4K或者4M很大 所以命中率很高。

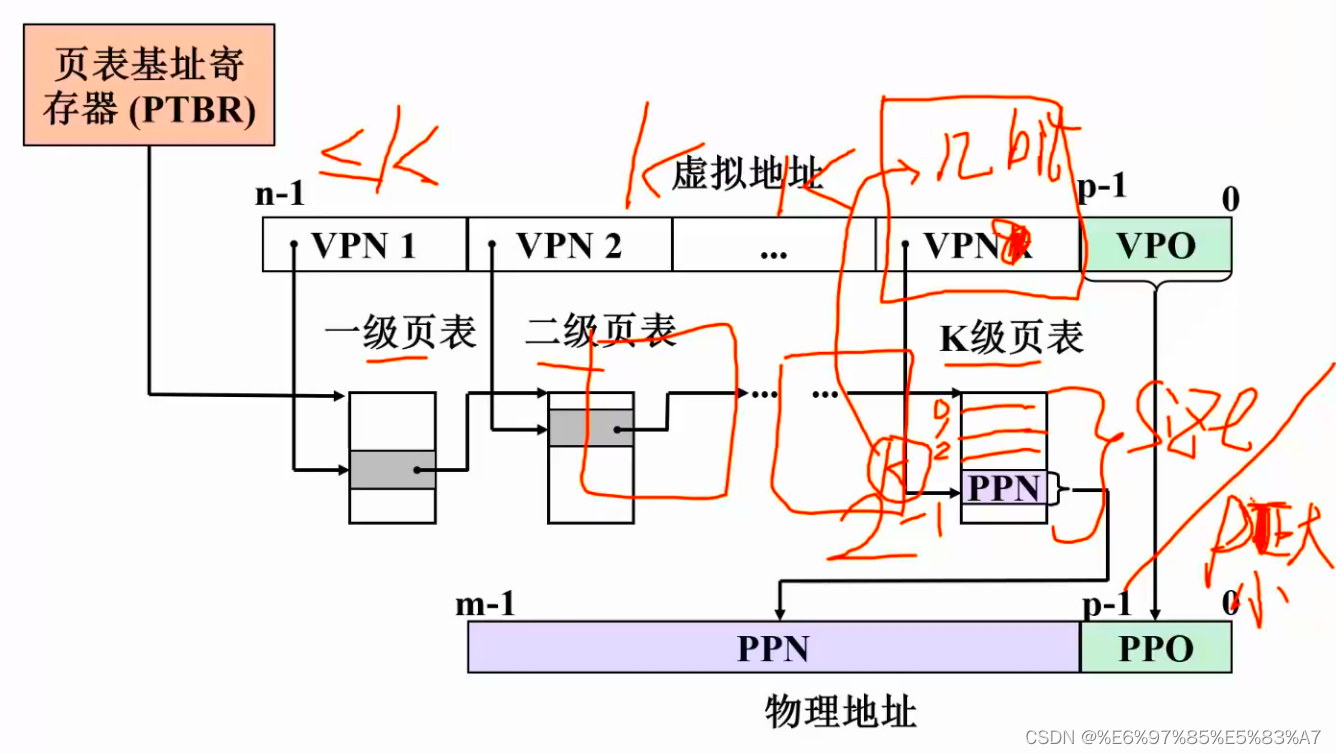

一个PTE是四个字节 一个页面是4K 一个页面可以放4KB/4个PTE

根据映射计算页表条目数量 根据映射原理 第K级页表数量是2 ^ K次方

虚拟内存-----系统

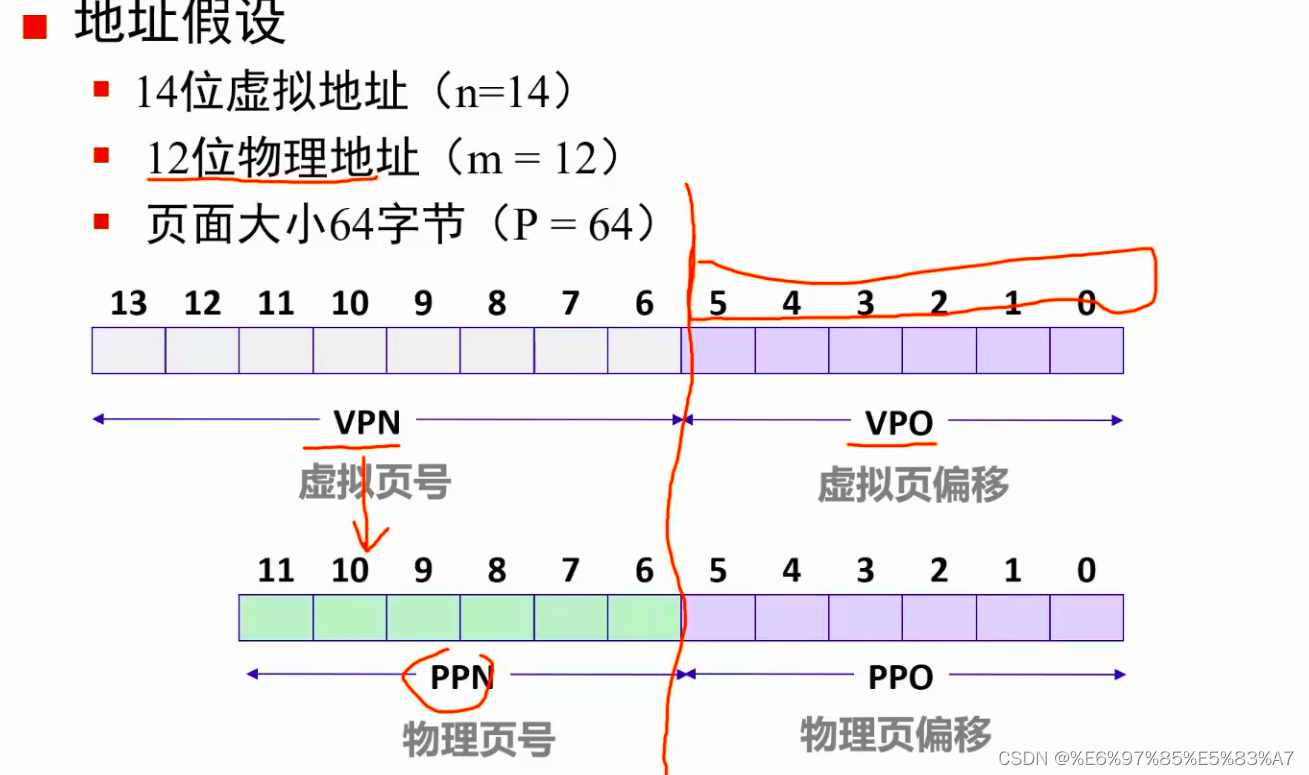

一个小内存系统的例子

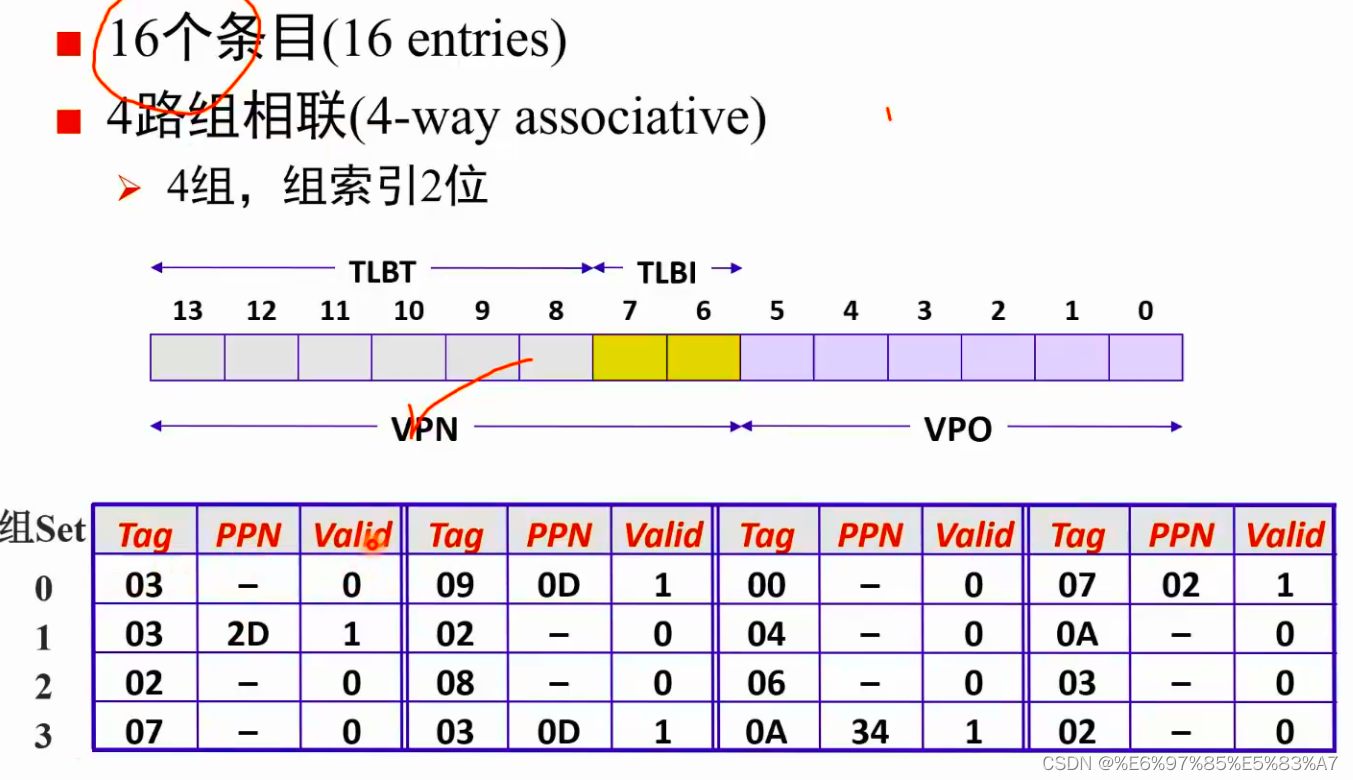

采用四路组相联的方法 就是每个组有四个块 设计地址格式 有2个位置用于标记组号 5位标记块内地址,TAG位用于标记比对 Valid检查条目是否有效 TAG表示高位地址

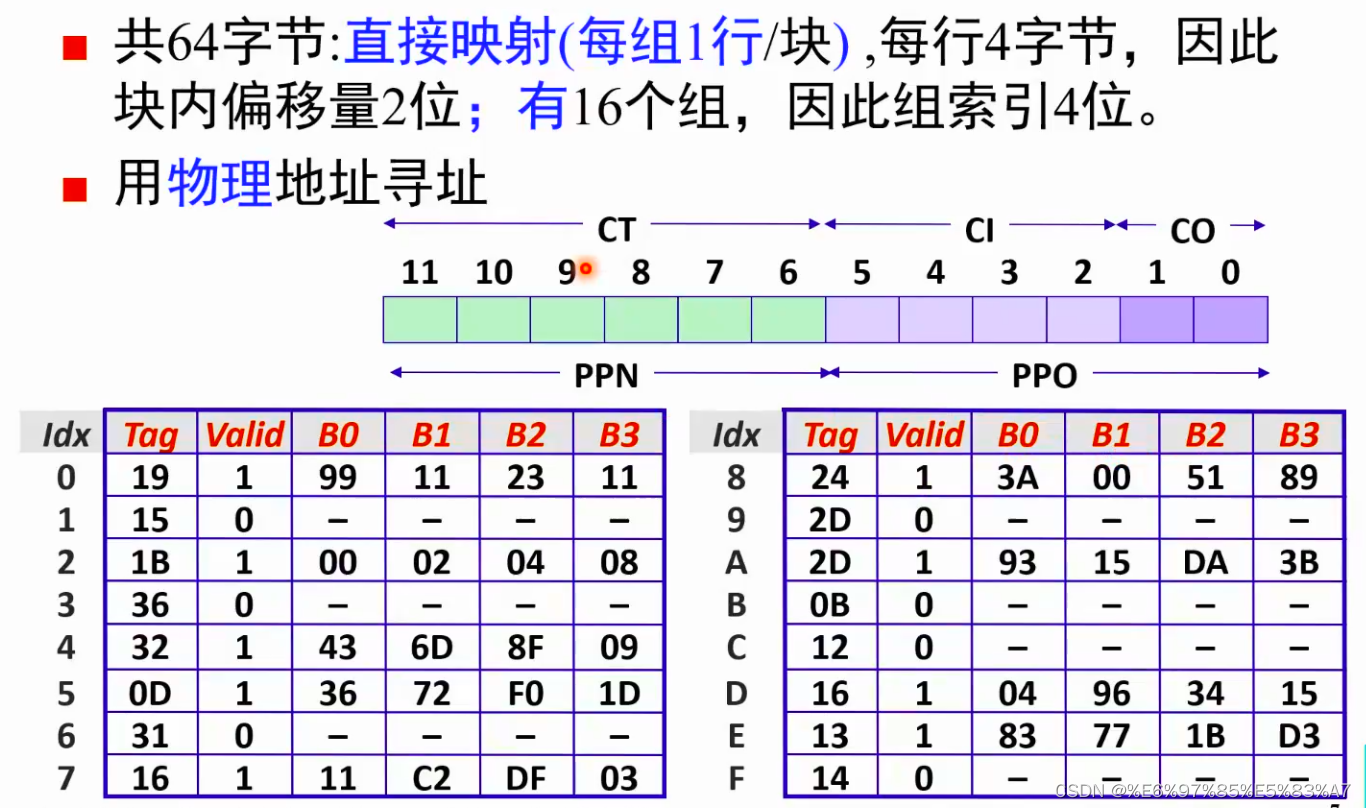

Cache

从虚拟内存到 物理地址cache 进而查找是否命中的例子 先划分地址的层次结构 ,因为是16组直接映射所以留下PPN中的四个位置标记,然后根据虚拟 地址的VPN查表得到是否命中 发现命中得到条目 得到条目之后和VPO或者是PPO拼接成物理地址 再对比cache 因为是组相联 查组是11 第三组

看第五组有没有tag是0D的块 然后读出第0个字节36

如果没有命中 他会上缓存中找 缓存中没有再去主存中找

Core i7的地址翻译过程

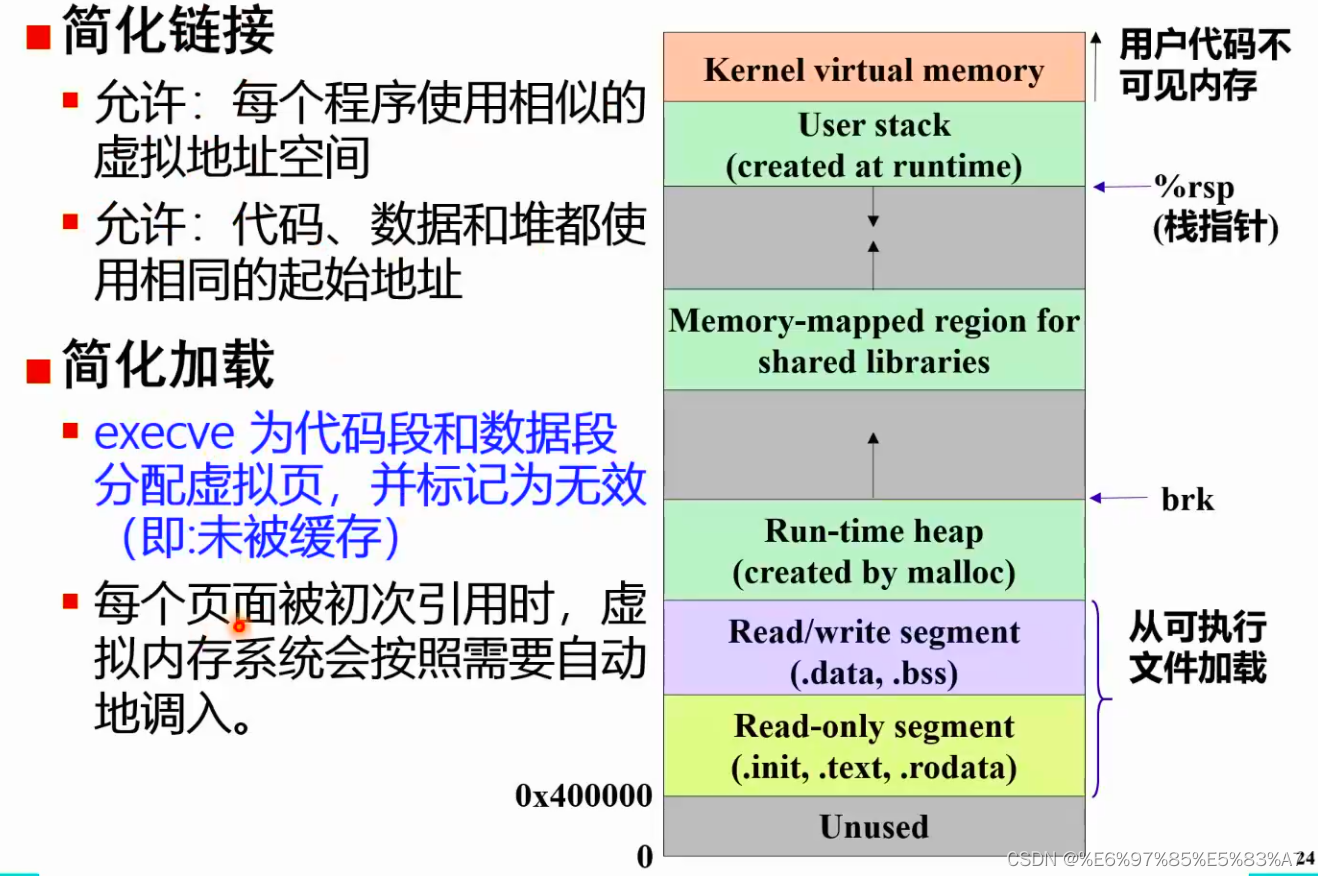

进程的虚拟地址空间分配

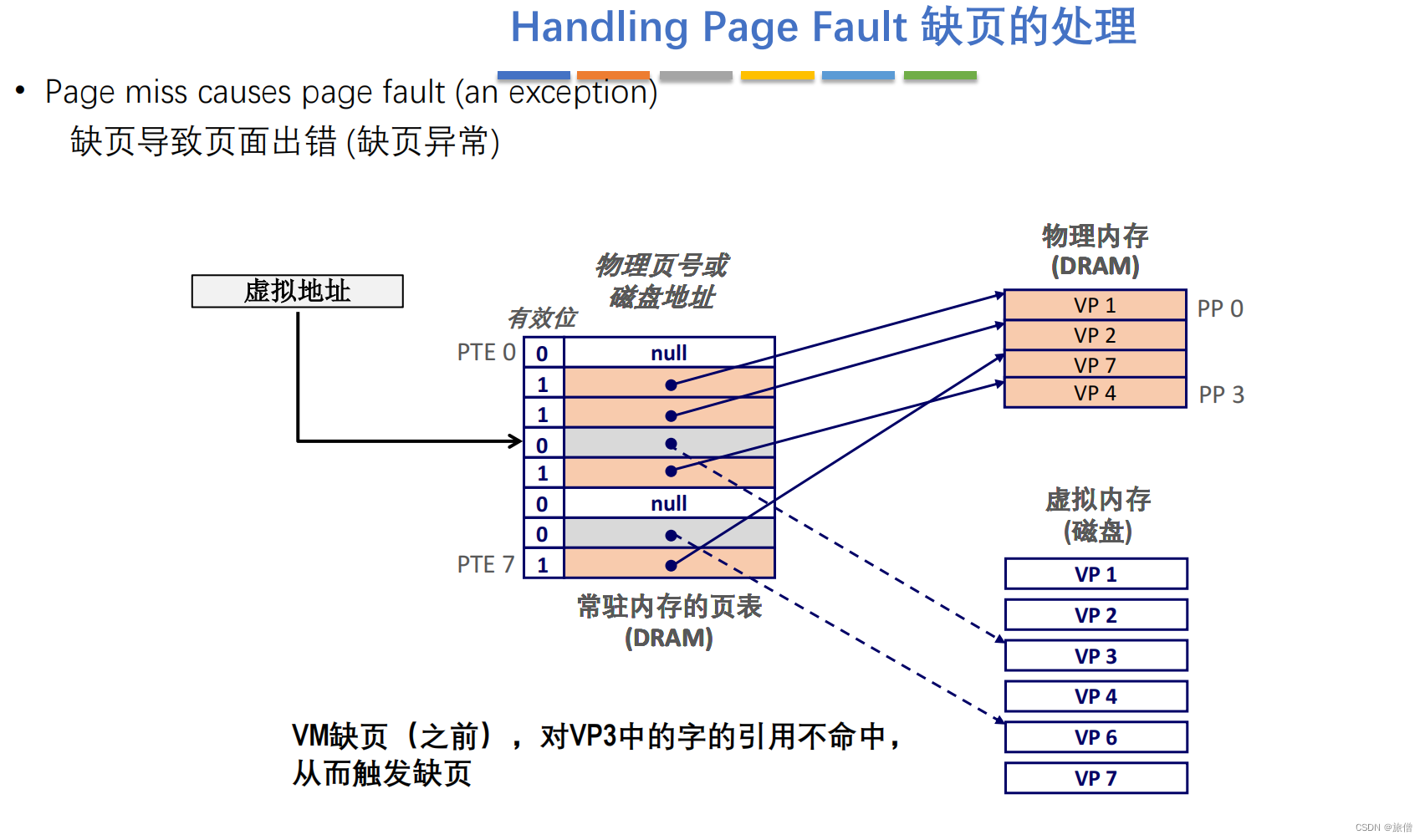

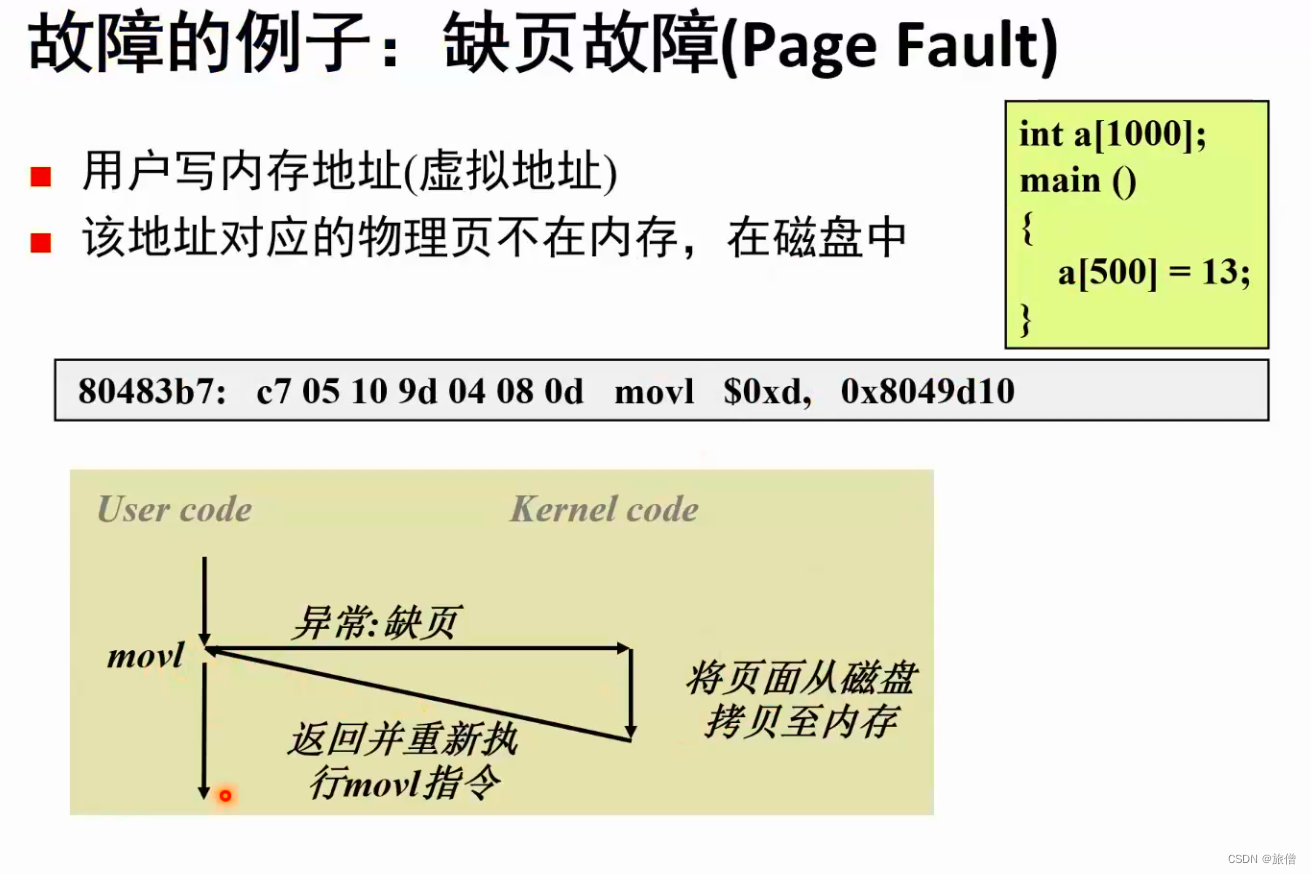

回忆我们第八章缺页异常的例子 他是一个当如果发现没有内存的时候 他会创建一个物理页面。