在通信中,PLL应用于同步和解调电路。例如,在FM解调和频移键控中,他们是常用的。除此之外,当想要输入的比特流中恢复时钟时,使用锁相环是很有可能的。此外,在通信系统中,为了抖动和降噪,通常使用锁相环。

PLL的常见应用之一是频率合成器以及音调形成。因此使用锁相环可以生成输入频率的倍数的输出频率。而在微处理器中,它们被用于产生稳定的系统时钟。

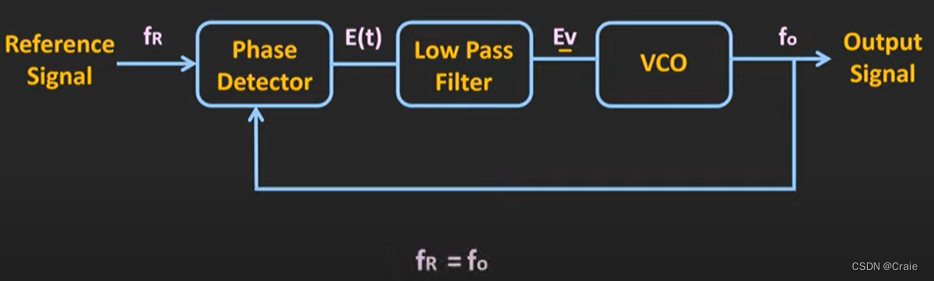

是控制系统或者控制回路,在输入和输出信号之间保持相同的相位。

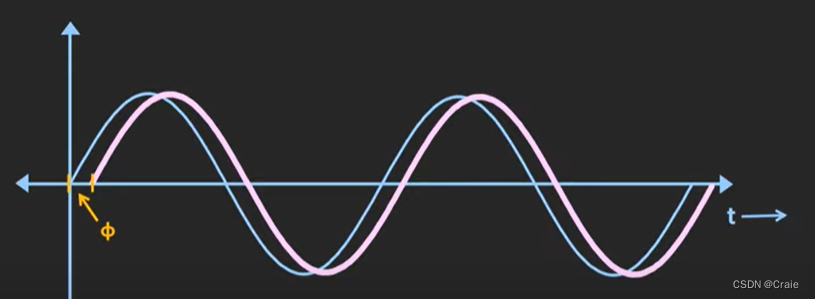

首先了解,什么是相位差?

如下图所示,两个信号具有相同的频率,但两个信号之间存在恒定的相位差

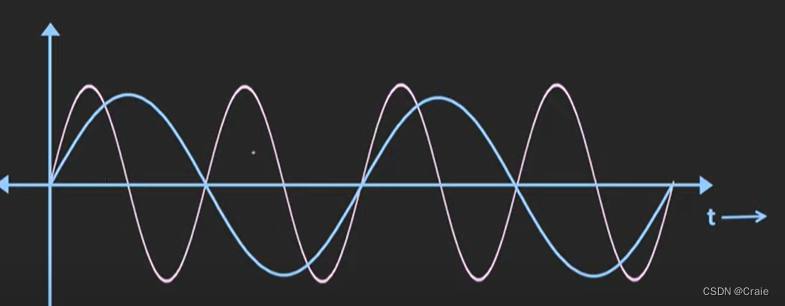

在下图中,两个信号之间的相位随时间不断变化。

因此锁相环系统使输出信号与输入信号在相位和频率上同步:

fo=fin 相位差=constant 环路处于锁定状态

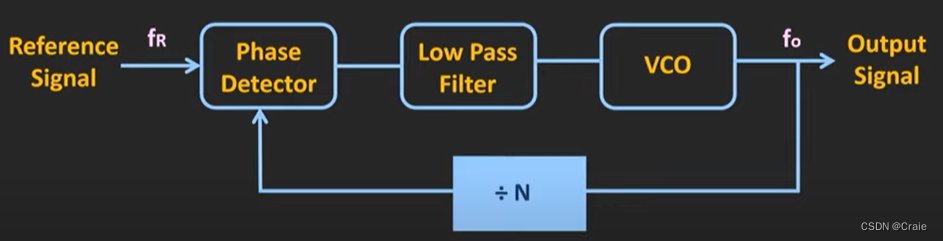

因此锁相环由三个基本模块组成:

当环路刚刚打开,VCO就会以中心频率运行,这个频率被称为自由运行频率。

现在相位检测器将输入或参考信号与振荡器频率进行比较,并在此基础上生成误差信号。这个误差信号通过低通滤波器,低通滤波器根据误差信号产生误差电压。根据这个误差电压,VCO要么减少要么增加振荡器频率,直到振荡器频率锁定在输入频率。

在锁定条件下,两个信号之间可能存在无相位差或恒定相位差。

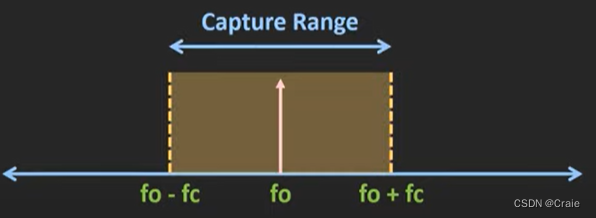

在无锁定条件下,只有当输入信号在PLL的捕获范围时,PLL才能获取锁定。这意味着,只要输入信号在捕获范围内,VCO就可以锁定输入信号。这意味着这捕获范围时VCO中心频率附近的输入频率范围

。只要从解锁条件开始,环路就可以锁定在该范围内。

因此PLL的另一个重要规格就是锁定范围。锁定范围定义了输入频率的范围,在该范围内,一旦捕获了输入信号,环路就会保持锁定状态。

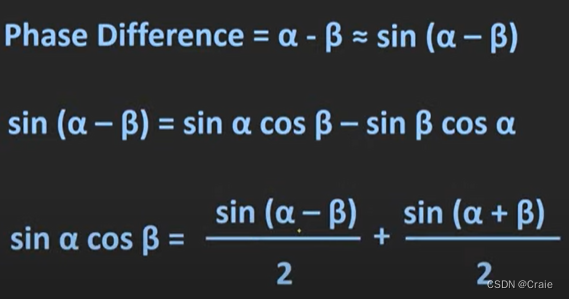

鉴相器如何识别两个信号之间的相位差?

假定在给定的时间点,一个信号具有某个相位 α \alpha α,另一个信号具有相位 β \beta β。两个信号之间的相位差为 α \alpha α- β \beta β。

如果相位差非常小,那么我们就说 α − β ≈ s i n ( α − β ) \alpha-\beta≈sin(\alpha-\beta) α−β≈sin(α−β)

其中第二项时高频信号,可以通过低通滤波器消除。这意味只要将两个信号相乘,就可得到两个信号之间的相位差。当这个信号通过低通滤波器时,他就会为VCO提供所需要的误差电压。

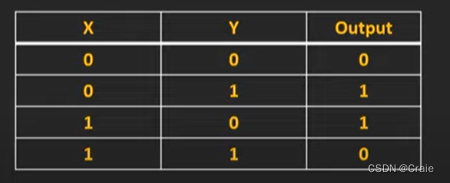

因此在射频上,平衡混频器用作相位检测器。而对于数字信号,相位频率检测器甚至异或门都可以用于相位检测。

如何将异或门用作相位检测器?

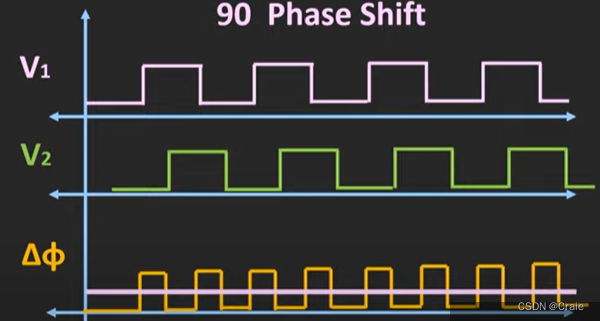

这意味着,只要两个信号之间没有相位差,那么理想情况下,异或门的输出应该等于0。但实际上在过度出会有一些尖峰,所以我们取这些相位差信号的平均值,那么它将大约等于0。同样,当相位信号差为90°时,会得到如下图所示的输出,对输出相位差信号取平均,会得到峰值一半的输出电压。

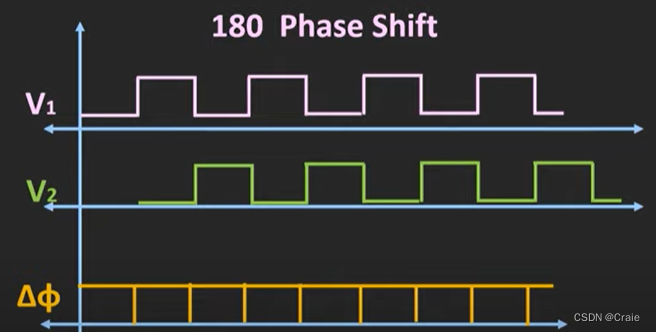

当两个信号之间的相位差为180°时,输出如下所示,输出将是最大的。理想情况下,它将会一直很高。但实际上,过渡处会有一些尖峰。

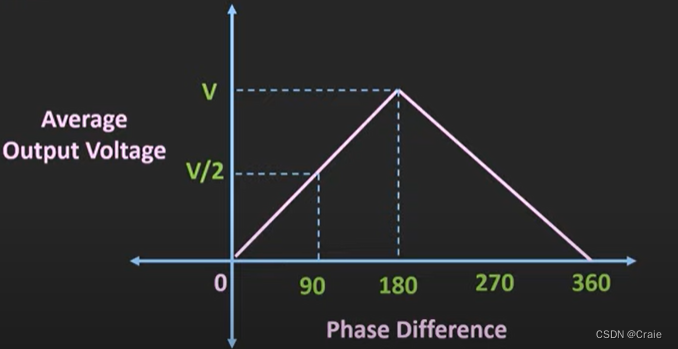

这意味着,两个信号之间的相位差增加,输出波形的平均值将增加。下图所示为低通滤波器饿相位差和平均输出值的图。

这意味着,相位检测器时线性相位检测器。但是相位关系仅在0-180°时是线性的。

但是理想情况下,相位检测器应该提供0-360°的线性相位关系。但是在异或鉴相器中,当相位差超过180°时,平均输出电压将降低,因此很难识别哪个信号领先或落后。

此外,要是异或门用作线性相位检测器,两个信号都应该具有大约50%的占空比。并且,每当两个信号在不同的频率下运行时,环路很可能会锁定到谐波频率。这都是异或门作为鉴相器的问题。

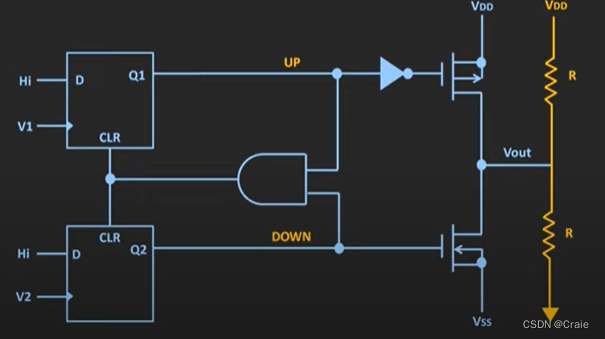

使用相位检测器应该可以解决这些问题。用D触发器和与门作为相位频率检测器。

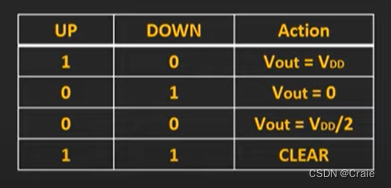

检测器的输出通常提供给电荷泵电路。因此,这里检测器的输出被提供给PMOS和NMOS电路。

这个相位检测器的工作原理:

两个D触发器的输入都连接到逻辑高电平。我们要检测相位差的两个信号作为时钟信号提供给这个D触发器。因此在这些输入信号的上升沿,D触发器的输出将变为高电平。上图中UP和DOWN变为高电平 ,则与门得到输出也变为高电平。这将reset这个D触发器。而一旦D触发器接收到清零信号,则UP和DOWN输出将变为0。因此在这种特殊情况下,当UO和DOWN输出都为0时,输出将与检测器电路隔离(就是图上vout断开)。在这种情况下,vout=VDD/2。

现在,只要这个UP输出为高电平,那么上部晶体管就会变为高电平。正因如此它将起到短路的作用。在这种情况下,vout=VDD。

同理,当DOWN输出为高电平时,此可下晶体管将变为高电平,将vout拉低到0。

因此,使用该电路可以识别哪个信号超前或滞后。此外,如果两个信号都以不同的频率运行,那么也可以对其进行矫正。

在这个基本的PLL环路中,当我们在反馈引入N分频计数器时,就可以将输出频率乘以N倍数。

![[P4]p4 integrate/resolve/copy](/images/no-images.jpg)