本设计是使用verilog实现秒表计时器。

秒表指示的时间由nexys4 DDR开发板的8个数码管显示,从左到右数码管的前两个显示小时(范围0-24),第3-4个数码管显示分(范围0-59,计数到60,向小时位进1),第5-6个数码管显示秒(范围0-59,计数到60向分位进1),第7-8个数码管显示毫秒(范围0-99,计数到100向秒位进1)。

要求实现如下功能:

(1)跑表的计时范围为0.01s~59min59.99s,计时精度为10ms。

(2)具有异步清零、启动功能。

(3)计时频率为100Hz。

(4)数字跑表的分和秒在数码管上显示出来,百分秒的BCD码在8个led上显示出来。

通过一个开关进行控制,开关为0时处于清0状态,开关为1,开始计时,从0秒开始,有毫秒,秒,分,时显示,共8个数码管显示。

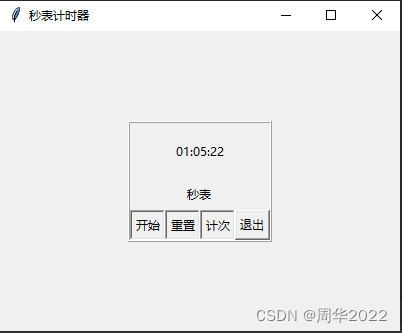

下面是vivado2017.4工程截图及仿真截图: