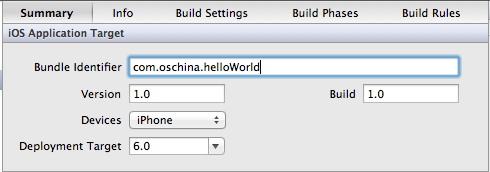

设计思路:

模24计数器,从零开始计数,计数到23时(10111),产生一个进位信号1,同时计数状态清零。

原理图:

功能模块代码:

module counter100(clk, rst_n, en, dout, co);

input clk, rst_n, en;

output[4:0] dout;

reg [4:0] dout;

output co;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

dout <= 5'b00000;

else if(en)

if(dout == 5'b10111)

dout <= 5'b00000;

else

dout <= dout + 1'b1;

else

dout <= dout;

end

assign co = dout[0]&dout[1]&dout[2]&dout[4];

endmodule测试模块代码:

`timescale 1ns/1ps

module counter100_tb;

reg clk, rst_n, en;

wire[4:0] dout;

wire co;

always

begin

#1 clk = ~clk;#2 $display("clk:%b -- rst:%b -- en:%b -- dout:%b -- co:%b", clk, rst_n,en,dout,co);

end

initial

begin

clk = 1'b0;

rst_n = 1'b1;

en = 1'b0;

#2 rst_n = 1'b0;

#2 rst_n = 1'b1; en = 1'b1;

end

counter100 u1(.clk(clk), .rst_n(rst_n), .en(en), .dout(dout), .co(co));

endmodule运行图: