RISC-V技术与展望

RISC-V(发音为“risk-five”)是一个基于精简指令集(RISC)原则的开源指令集架构(ISA)。

与大多数指令集相比,RISC-V指令集可以自由地用于任何目的,允许任何人设计、制造和销售RISC-V芯片和软件。虽然这不是第一个开源指令集,但具有重要意义,因为其设计使其适用于现代计算设备(如仓库规模云计算机、高端移动电话和微小嵌入式系统)。设计者考虑到了这些用途中的性能与功率效率。该指令集还具有众多支持的软件,这解决了新指令集通常的弱点。

该项目2010年始于加州大学伯克利分校,但许多贡献者是该大学以外的志愿者和行业工作者。

RISC-V指令集的设计考虑了小型、快速、低功耗的现实情况来实做,但并没有对特定的微架构做过度的设计。

截至2017年5月,RISC-V已经确立了版本2.22的用户空间的指令集(userspace ISA),而特权指令集(privileged ISA)也处在草案版本1.10。

本文参考文献链接

https://baike.baidu.com/item/RISC-V/22606314?fr=aladdin

https://mp.weixin.qq.com/s/xrwPaxlvKlGmKdeJPKwmmg

特点

完全开源

对指令集使用,RISC-V基金会不收取高额的授权费。开源采用宽松的BSD协议,企业完全自由免费使用,同时也容许企业添加自有指令集拓展而不必开放共享以实现差异化发展。

架构简单

RISC-V架构秉承简单的设计哲学。体现为:

在处理器领域,主流的架构为x86与ARM架构。x86与ARM架构的发展的过程也伴随了现代处理器架构技术的不断发展成熟,但作为商用的架构,为了能够保持架构的向后兼容性,其不得不保留许多过时的定义,导致其指令数目多,指令冗余严重,文档数量庞大,所以要在这些架构上开发新的操作系统或者直接开发应用门槛很高。而RISC-V架构则能完全抛弃包袱,借助计算机体系结构经过多年的发展已经成为比较成熟的技术的优势,从轻上路。RISC-V基础指令集则只有40多条,加上其他的模块化扩展指令总共几十条指令。 RISC-V的规范文档仅有145页,而“特权架构文档”的篇幅也仅为91页。

易于移植*nix

现代操作系统都做了特权级指令和用户级指令的分离,特权指令只能操作系统调用,而用户级指令才能在用户模式调用,保障操作系统的稳定。RISC-V提供了特权级指令和用户级指令,同时提供了详细的RISC-V特权级指令规范和RISC-V用户级指令规范的详细信息,使开发者能非常方便的移植linux和unix系统到RISC-V平台。

模块化设计

RISC-V架构不仅短小精悍,而且其不同的部分还能以模块化的方式组织在一起,从而试图通过一套统一的架构满足各种不同的应用场景。用户能够灵活选择不同的模块组合,来实现自己定制化设备的需要,比如针对于小面积低功耗嵌入式场景,用户可以选择RV32IC组合的指令集,仅使用Machine Mode(机器模式);高性能应用操作系统场景则可以选择譬如RV32IMFDC的指令集,使用Machine Mode(机器模式)与User Mode(用户模式)两种模式。

完整的工具链

对于设计CPU来说,工具链是软件开发人员和cpu交互的窗口,没有工具链,对软件开发人员开发软件要求很高,甚至软件开发者无法让cpu工作起来。在cpu设计中,工具链的开发是一个需要巨大工作量的工作。如果用RISC-V来设计芯片,芯片设计公司不再担心工具链问题,只需专注于芯片设计,RISC-V社区已经提供了完整的工具链,并且RISC-V基金会持续维护该工具链。当前RISC-V的支持已经合并到主要的工具中,比如编译工具链gcc, 仿真工具qemu等

开源实现

BOOM: Christopher Celio的RV64乱序处理器实现。Chisel, BSD Licensed。[GitHub][Doc]

BottleRocket: RV32IMC微处理器。Chisel, Apache Licensed。 [GitHub]

bwitherspoon: RV32微处理器。SystemVerilog, ISC Licensed。[GitHub]

Clarvi: 剑桥大学教学用RISC-V处理器。SystemVerilog, BSD Licensed。[GitHub]

F32: 针对FPGA的RV32微处理器,VHDL,BSD Licensed。[GitHub]

GRVI: Gray Research LLC. 针对FPGA优化的RV32微处理器,commercial licensed。[Web]

Hummingbird E200. 二级流水线,目标替代Cortex-M0/8051, Verilog, Apache 2.0 licensed。[GitHub]

invicta: 一级流水线的RV32微处理器。Verilog,BSD Licensed。[GitHub]

Kamikaze: RV32微处理器。Verilog,MIT Liencensed。[GitHub]

KCP53000: Samuel A. Falvo II的RV64处理器实现。Verilog, MPL Licensed。[GitHub]

nanorv32: 2机流水线的RV32实现。Verilog, GPLv2 Licensed。[GitHub]

OpenV: 支持RV32的开源微处理器,Verilog,MIT Licensed,OnChipUIS,来源于哥伦比亚的Universidad Industrial de Santander。[GitHub]

ORCA: 支持RV32的开源微处理器,VHDL,BSD Licensed,VectorBlox。[Github]

PicoRV32: Clifford Wolf设计的(针对FPGA)RV32微处理器,Verilog,ISC Licensed。[GitHub]

Potato: 针对FPGA的RV32微处理器。VHDL,BSD Licensed。[GitHub]

RI5CY:支持RV32的开源微处理器

• PULPino: SystemVerilog,Solderpad Licensed, 来源于苏黎世理工和博洛尼亚大学的PULP项目。[GitHub][Web]

River: GNSS Senor Ltd.基于Rocket架构开发的RV64处理器。VHDL, BSD Licensed。[GitHub]

Rocket: 支持RV64/32的开源处理器

• Rocket-Chip: Chisel,BSD Licensed, Free chips project, UC Berkeley分离的开源工程。[GitHub]

• Freedom: Chisel,Apache Licensed, SiFive, UC Berkeley分离的初创企业。[GitHub][Web]

• lowRISC:Chisel+SystemVerilog,Solderpad Licensed, 从剑桥大学发起的非盈利组织。[GitHub][Web]

• RoCC: the Rocket customized coprocessor interface 和Rocket处理器紧密互联的的协处理器接口。[BSG]

RV12: RoaLogic的RV32微处理器。Verilog, RoaLogic non-commercial Licensed。[GitHub]

SCR1: Syntacore的RV32开源微处理器。SystemVerilog,Solerpad Licensed。[GitHub]

SHAKTI:印度IIT-Madras的RISC-V处理器系列,Bluespec, BSD Licensed。[Bitbucket]

Sodor: 教学用的RISC-V处理器。Chisel, BSD Licensed。[GitHub]

uRV: 针对FPGA的RV32微处理器。Verilog,LGPLv3 Licensed.[ohwr]

VexRiscv: 用SpinalHDL编写的针对FPGA的RV32微处理器。SpinalHDL, MIT Licensed。[GitHub]

YARVI: Tommy Thorn设计的RV32I微处理器,Verilog,GPL2v Licensed。[GitHub]

成功的流片案例

已经有机构和商业公司流片的案例。可关注RISC-V社区了解具体信息。

社区贡献

完整的工具链维护,大量的开源项目。risc-v的google讨论组(名称:RISC-V ISA Dev)吸引各地自愿者参与讨论来不断改进risc-v架构。

成功尝试

处理器芯片CPU,电子设备的大脑,在几乎所有电子设备里都会找到。能做CPU的公司很多,但全世界的CPU却主要基于两种结构:一个是英特尔AMD在用的x86架构,另外一个是苹果高通海思等等很多公司在用的ARM架构。

直到最近几年,一个名叫RISC-V的新架构横空出世,谷歌、高通、英特尔等国外公司,阿里平头哥、华为、中兴等国内公司,都已经在深度布局RISC-V CPU了。甚至有人说,RISC-V会和x86和ARM形成CPU领域的三足鼎立。

RISC-V到底是什么,有哪些独到之处值得受到全球的关注?对中国的芯片行业、特别是最关键的处理器芯片领域,到底有哪些好处?能否帮助中国芯片实现突围?

RISC-V:x86与arm之外的第三极

处理器芯片是电子产品和设备的核心,处理器芯片的核心,就是指令集。指令集就好比是语言的语法规则,根据这套语法和规则,就可以遣词造句写出不同的文章。

不管是x86、arm还是RISC-V,其实都是一种指令集,就好像中文、英文、日文一样,都有着不同的语法和规则。根据指令集规范,就可以设计出不同的处理器,比如基于x86的酷睿和锐龙,基于arm的苹果M1和高通骁龙,基于RISC-V的平头哥玄铁和中科院计算所的香山,等等。

RISC-V之所以会受到越来越多的关注,因为RISC-V最大的特点就是开源、开放、免费。在RISC-V出现之前,主要的指令集都归少数几个大公司所有。比如英特尔和AMD拥有x86指令集的所有权,但并不对外授权,而是直接做成芯片自产自销,借着互联网的东风和个人电脑的普及,英特尔与微软达成了Wintel联盟,让x86成为了现在计算机领域使用最广泛的指令集。

相比之下,ARM稍微开放一点,并不自己设计生产芯片,而是授权给苹果高通英伟达这些公司,让使用ARM指令集架构去造芯片,每造出来一颗就收一点钱。而趁着移动互联网的浪潮,ARM与Android联手,主导了手机和平板电脑市场。

不过不管是x86还是ARM,这些语言的语法规则都是少数几个大公司制定的。你想说这门语言,或者你想用这门语言写文章,那你就要先花钱买这些公司的授权。如果张三有个绝妙的想法,需要用一种处理器芯片去实现,但是兜里连一个大钢镚都没有,那就没办法去实现这个想法了。

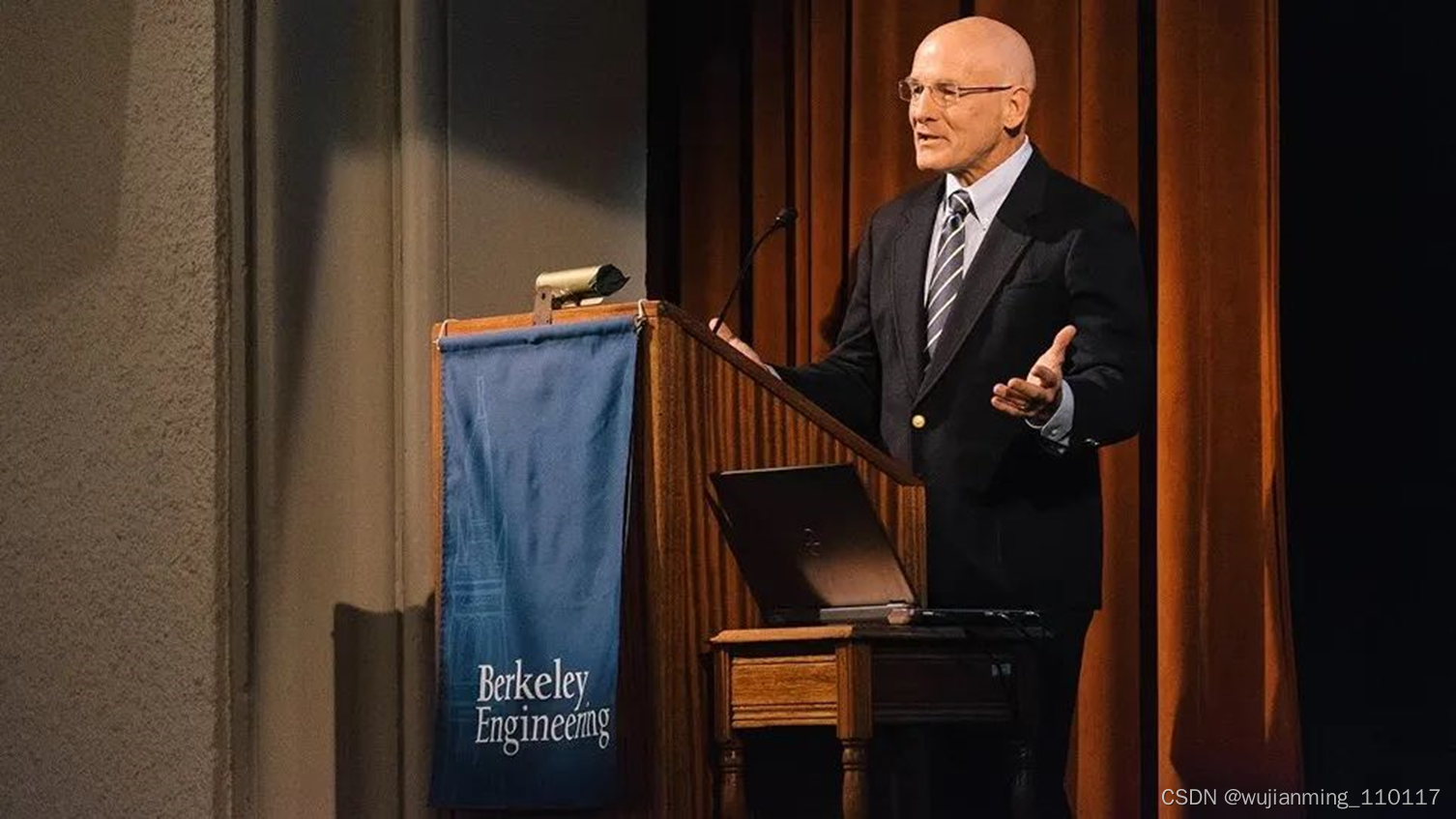

因此在2010年的时候,加州大学伯克利分校的几位学者,包括后来获得图灵奖的David Patterson教授提出了一个口号,叫做“指令集应该免费 - Instruction Sets Want to be Free” 。也就是说,需要有一个全球通用的指令集标准,这样全世界所有的张三、李四,以及所有的公司和大学,都可以基于这个标准去做自己的处理器。而更重要的是,这个指令集标准应该是Free的。当时团队4个人仅花了三个月的时间,就完成了RISC-V指令集的设计和开发。

值得一提的是,RISC-V这个名字由两部分组成,RISC指的是精简指令集。相对的是复杂指令集,也就是CISC,x86架构就是典型的CISC。而这个V其实是罗马数字的5,所以RISC-V的意思就是第五代精简指令集处理器。这是因为伯克利的David Patterson之前已经做了四代RISC,所以最终留下来的是第五代,也就是RISC-V。

RISC-V的核心理念就是“Free”,这个Free其实有几层含义。首先就是免费:和x86、arm不一样,RISC-V是完全免费的,没有授权费,没有黑心中间商赚差价,但这只是最底层的意义。

Free在英语中还有“自由”的意思,也就是说RISC-V是开放的,使用起来也非常自由,你可以自己给他加新的指令,可以在原有指令的基础上进行扩展,甚至也可以删掉那些不必要的指令,最终实现一个专门为你量身定做的处理器芯片。

就拿人工智能应用来举例,RISC-V里就有专门的矢量指令扩展,就是用来加速人工智能应用里常见的矢量运算的。很多的RISC-V处理器也通过在芯片里集成专门的矢量执行单元,来重点支持RISC-V的矢量指令。比如阿里平头哥的C906,就可以支持INT8到INT64、FP16到FP64,以及BFP16的这些新型数据格式。

RISC-V有着很高的灵活性和可定制性,这特别适合于AIoT这种非常碎片化的场景。很多的智能设备的功能各不相同,一方面并不需要一个面面俱到的CPU去进行控制,另一方面对某些特定的应用场景还需要专门的优化,同时还要兼顾高性能和低功耗。这样一来,RISC-V就可以通过各种不同的配置,特别适用于这种有很强碎片化的场景。

很多人觉得RISC-V只能做低端低性能的处理器,其实并不是这样。比如率先实现对安卓系统兼容的玄铁C910、还有很多朋友都听说过的香山处理器,都是高性能RISC-V处理器的代表。

除了通用性能之外,RISC-V在专用性能上也可以做的很高,比如前面说的平头哥C906对人工智能的优化实现,包括对矢量运算的支持、对不同数据精度的支持等等,都可以让C906的AI性能上一个大的台阶。

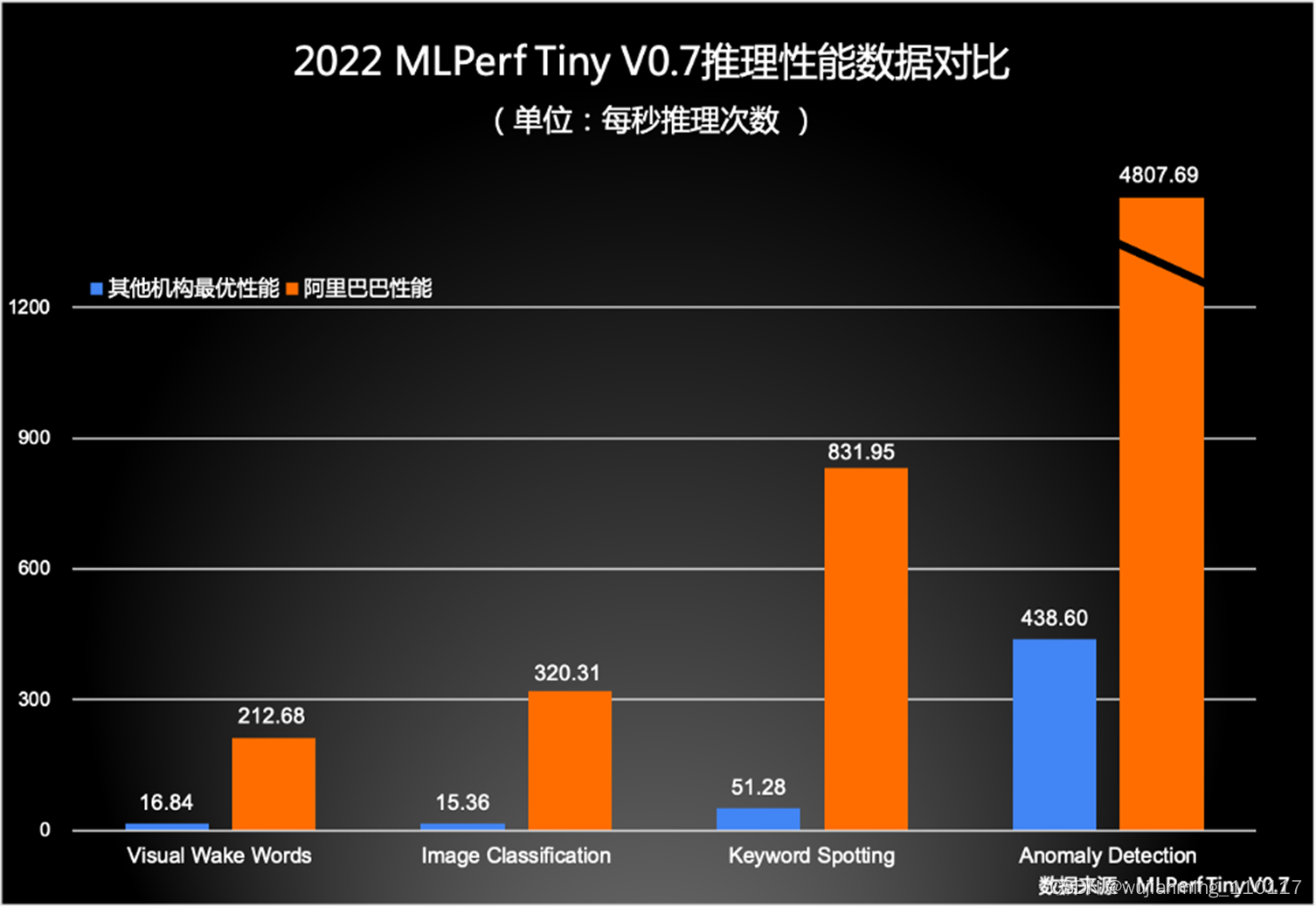

在全球的人工智能领域有个基准测试叫MLPerf,各种AI芯片做出来之后都会拿MLPerf跑个分。除了传统的那些人工智能的大规模高算力的场景,近两年MLPerf增加了一个叫Tiny的新分类,专门针对低功耗和高性价比的AIoT领域。

在4月7日的最新榜单里,平头哥玄铁C906在全部4个基准测试的数据上都拿到了世界第一,并且领先第二名10到20倍,这也创造了RISC-V架构在MLPerf tiny里有史以来的最好成绩。

值得注意的是,平头哥做的这个并不是AI加速器,而是直接在RISC-V CPU里提供对人工智能应用的支持。这样就比使用额外的AI加速器有更好的能效。

提升性能的秘诀:软硬件协同

有了指令集和处理器芯片本身,其实还远远不够。事实上,每个人都可以自立门户,在很短的时间里自己任意设计一套新指令集RISC-250。但是为了真正广泛的用起来,配合这个芯片硬件进行使用的软件同样重要。

之前写过,“没有软件,芯片就只是昂贵的沙子”,软件给芯片注入了灵魂。再拿人工智能举例,即使芯片上集成了指令集扩展和矢量加速引擎,也需要通过软件给开发者提供使用的方法。

但是说起软件,其实并不是只有一种。芯片厂商通常会提供一系列不同的软件,并且像夹心饼干或者汉堡一样把一层一层摞起来。这样最大的好处是能够让每一层专注于某个具体的功能,而不需要设计一个巨大巨复杂的软件负责所有事情。

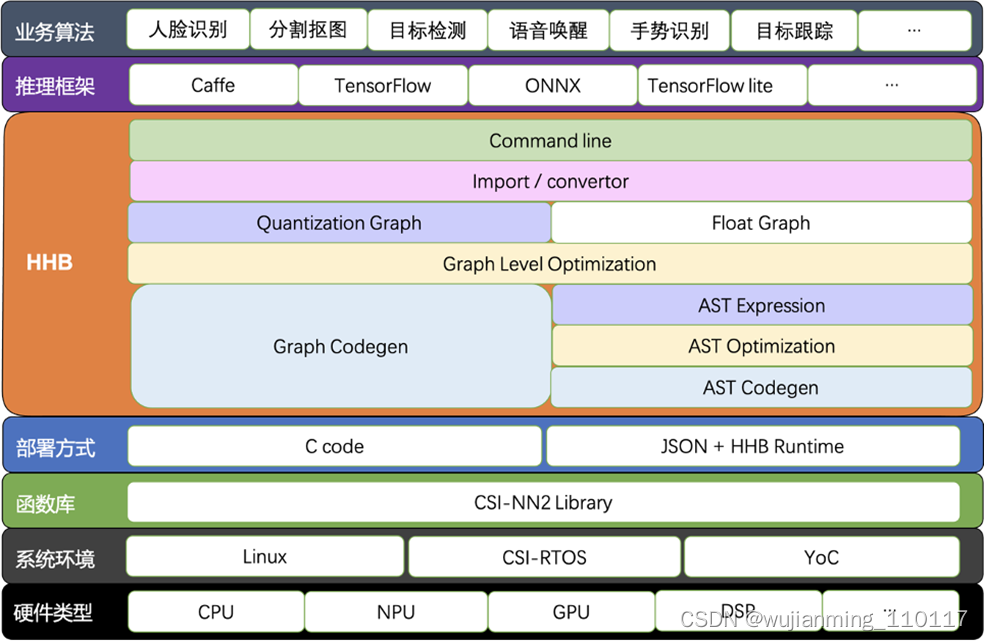

比如平头哥就有一个名叫HHB的软件框架,平头哥提供的一套针对玄铁 CPU 平台的神经网络模型部署工具集,包括了部署神经网络模型的时候需要的编译优化、性能分析、过程调试、结果模拟等一系列工具。

HHB在整个软件大汉堡的中间,上面是Caffe、TensorFlow这些业界通用的机器学习库和框架,下面是用于底层硬件实现的函数库和系统环境。HHB最重要的功能,就是负责将上层机器学习框架训练导出的各种模型文件,转换成底层的函数库的调用。HHB的功能还有很多,包括支持多种数据类型的多种量化方式 ,可以自动为指定的玄铁CPU平台选择最优的量化方案等等。

除了HHB,平头哥还有一个叫CSI-NN2的开源神经网络加速库。一方面对各种常用的算子进行了接口抽象,另一方面考虑了不同的数据精度和量化方法,针对CPU的流水线,分支预测和高速缓存这些硬件特性进行了代码优化。这种软硬件结合的优化方式,其实也正是现在处理器芯片设计和优化的最主流的方法。

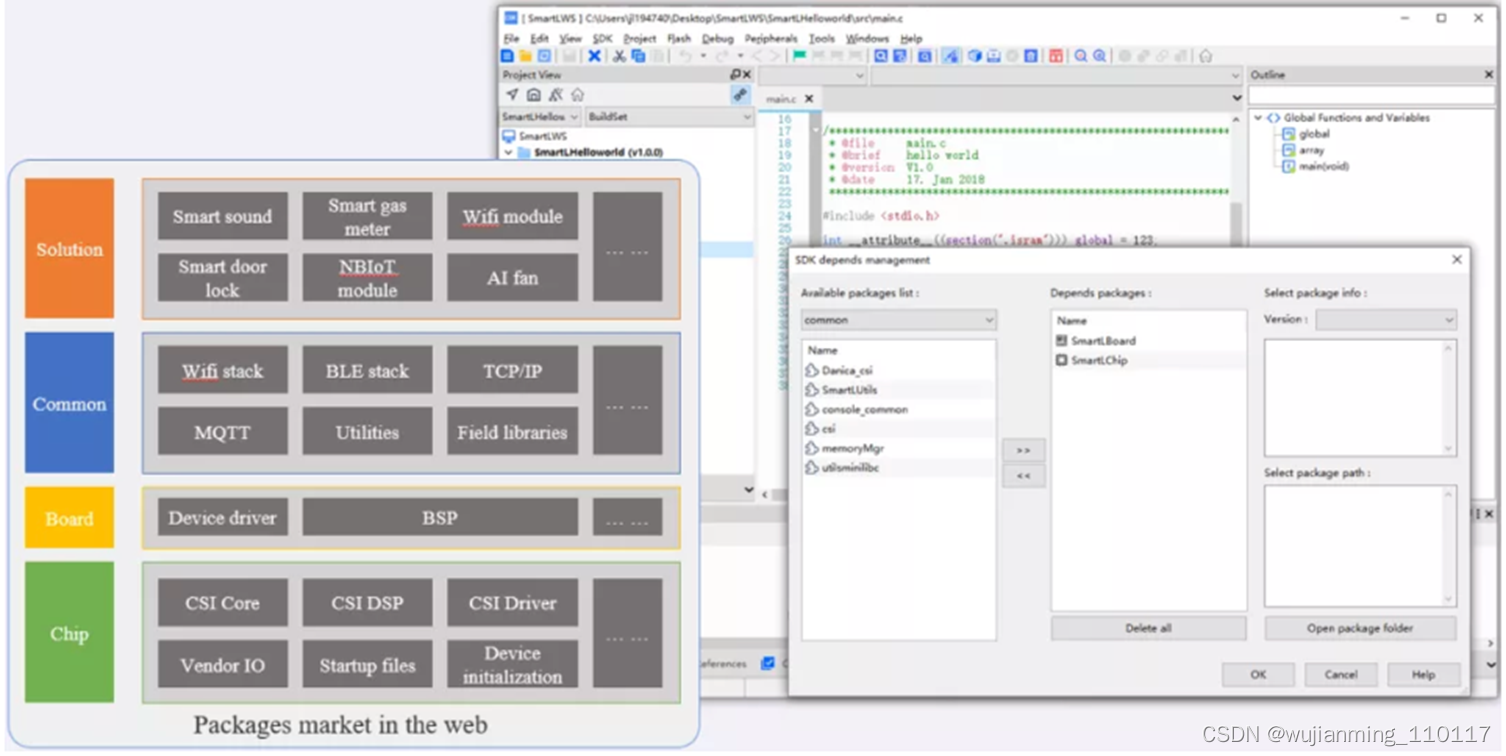

有了软件、框架和函数库,还需要一个集成的开发环境把这些工具整合起来,并且给软件工程师提供一个统一的开发界面。再拿平头哥举例,提供了一个叫剑池CDK的集成开发环境,能自动对接底层的RISC-V芯片平台,并且自动获取芯片上面的开发资源。

剑池CDK主要包含四个部分,分别是各种开发包和组件、图形化的编辑器、调试器、还有分析器。这四个部分,其实也是绝大多数软件或者嵌入式开发环境都会包含的主流配置,但是剑池CDK把这些集成到了RISC-V的芯片开发里。

通过提供的这些开发包和组件池,开发者可以直接在这个池子里选择需要的组件,然后拼接成系统,这一方面增强了组件重复使用的能力,另一方面也提高了芯片的开发速度,不需要开发者再造轮子了。而产业链下游的厂商,则可以根据对市场需求的了解,在此基础上进一步开发出更定制化的AI功能和应用。

处理器生态:走向成熟的必要条件

前面说过,RISC-V最重要的特点,就是开源开放。比如平头哥就开源了包括C910和C906在内的四个玄铁RISC-V处理器、以及相应的多个操作系统和全栈软件工具。这种开源的商业模式,和人们的传统理解相比其实有着很大的差异。

很多人都会有这样的疑问,如果把所有的源代码、文档和秘密都公开了,那还怎么赚钱,还怎么活?

开源的逻辑是,仅凭一家公司或机构,很难既完成核心技术突破,又能在此基础上实现丰富多样的应用开发,而后者就是通常说的生态,往往更能决定一个架构的兴衰成败。英特尔与微软,Arm与安卓,这两大架构的成功,都极端依赖于生态的繁荣。

有一个说法,在处理器上投入1块钱,生态就会长出20块钱,生态是处理器架构发展的价值放大器。这也好理解,如果每个人都守着自己的一亩三分地,那迟早会遇到发展的瓶颈。只有不断把生态这个蛋糕做大,每个人才能分到更多的蛋糕。

另外,生态的好处就是,每个人都可以针对擅长的领域去做,不需要从头造轮子,这也将极大加快创新涌现。事实上,软件开发早就基于开源生态了,比如某个公司想做一个APP,肯定绝大部分代码都不需要自己写,可以直接在开源社区里获取,而自己只需要专注在那10%的、和自己业务直接相关的代码开发上。而就是这10%,才构成了这个公司最重要的核心竞争力。

这就大大降低了软件创新的门槛,国内外的那些互联网巨头,其实都是通过这种方式成长起来的。也成为了软件开源生态的主要贡献者,比如前面说的TensorFlow、PyTorch这些AI框架,还有Linux、Redis、Kubernetes等等。

尽管硬件开源还是件新鲜事,但如何去做可以参考软件开源。比如想做一个定制的AI芯片,就完全可以拿平头哥开源的玄铁C906,然后在上面加上核心算法、或者对RISC-V的指令集扩展,并且再用开源的EDA工具,就能快速地完成一个AI处理器的设计开发。这种方式,在x86或者arm时代,是绝对不可能想象的。

结语

在开源软件里,Linux是整个生态的基石。基于Linux人们开发出了编程语言、编译器、开发框架模型等等一整套工具链和大量开源软件。

在芯片领域, RISC-V未来和可能会像Linux那样,成为芯片和计算机创新的基石。处理器性能刷新,软硬件协同效率提升,芯片应用越来越广泛,匹配领域也不断扩大,种种迹象表明,现在已经走在了RISC-V生态繁荣的前夜,相信未来会有越来越多的软硬件开发者加入这个生态。

本文参考文献链接

https://baike.baidu.com/item/RISC-V/22606314?fr=aladdin

https://mp.weixin.qq.com/s/xrwPaxlvKlGmKdeJPKwmmg