目录

1.概述

2.Header Type0

2.1 HeaderType字段

2.2 Class寄存器

2.3 Cache Line Size 寄存器

2.4 Subsystem ID 和 Subsystem Vendor ID 寄存器

2.5 Capabilities Pointer 寄存器

2.6 Interrupt Line 寄存器

2.7 Interrupt Pin 寄存器

2.8 Base Address Register 0~5寄存器

2.9 Command 寄存器

2.10 Status 寄存器

2.11 Latency Timer 寄存器

3.Header Type1

3.1 Secondary Status 寄存器

3.2 Secondary Latency Timer 寄存器

3.3 I/O Limit 和 I/O Base 寄存器

3.4 Memory Limit 和 Memory Base 寄存器

3.5 Prefetchable Memory Limit 和 Prefetchable Memory Base 寄存器

3.6 I/O Base Upper 16 Bits and I/O Limit Upper 16寄存器

3.7 Bridge Control Register

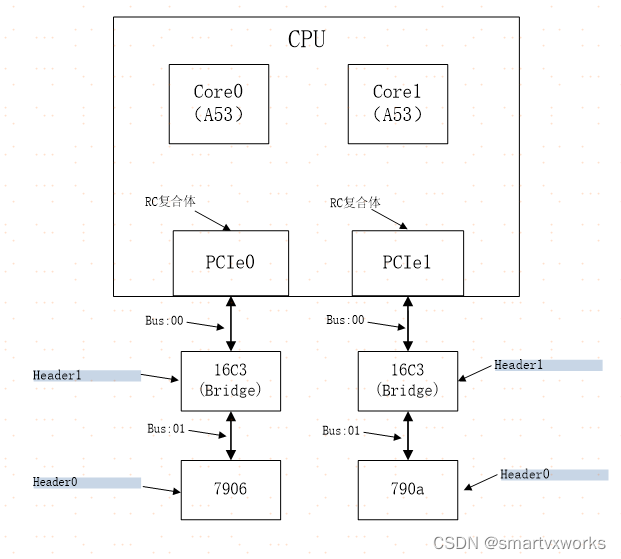

1.概述

每个PCIE设备都有自己的独立的一段配置空间,该部分空间是这个设备的,系统会给这个设备分配一段内存空间,CPU访问这段内存空间即访问对此设备的配置空间。设备在出厂时,配置空间是有默认初始值的。

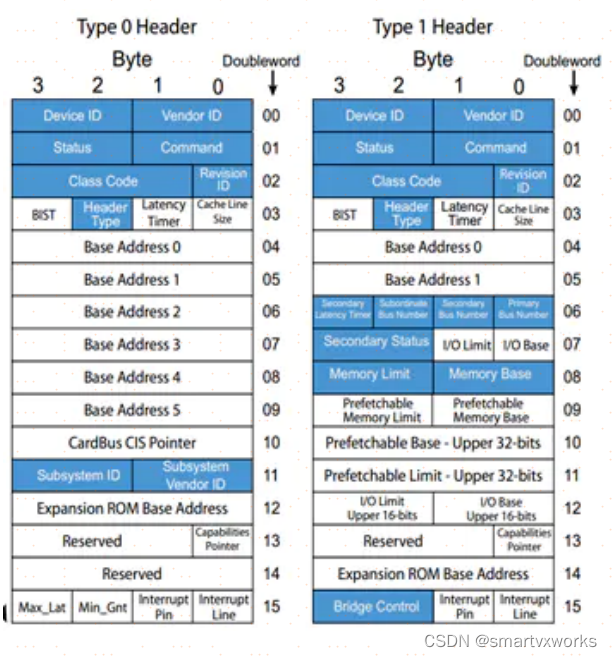

PCIe配置空间两种类型的Header Type(Type0和Type1),Type0和Type1,这是因为PCIe设备分为Bridge和Agent两种类型,Agent的配置空间类型称为Type 0类型,Bridge的配置空间类型称为Type1类型。

PCIe软件在枚举时会依次读取每台设备中功能0的厂商ID,当返回一个不为全F的值时表明设备存在,然后读取头(Header)寄存器中的头类型(Head Type)字段,确定是桥或端点设备或其它类型,以及单功能/多功能设备。

2.Header Type0

- DeviceID+VendorID:芯片厂商固化在芯片内部,只读,比如我们的产品

- PCIe转PCI总线的桥片:0xabcd16c3;

- WIFI Master chip:0x790614c3;

- WIFI Slave chip:0x790a14c3。

- Revision ID 和 Class Code 寄存器

这两个寄存器只读。其中 Revision ID 寄存器记载 PCI 设备的版本号。该寄存器可以被 认为是 Device ID 寄存器的扩展。

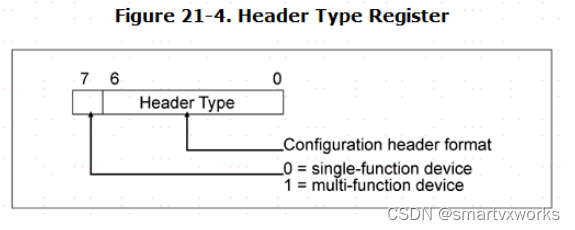

2.1 HeaderType字段

- 通过此字段可以判断Device是Bridge设备还是Agent设备。

第7位为1表示当前 PCI 设备是多功能设备,为0表示为单功能设备。

第6~0位表示当前配置空间的类型,为0表示该设备使用 PCI Agent 设备的配置空间,普 通 PCI 设备都使用这种配置头;为1表示使用 PCI 桥的配置空间,PCI 桥使用这种配置 头;为2表示使用 Cardbus 桥片的配置空间,Card Bus 桥片在这里暂时不介绍。

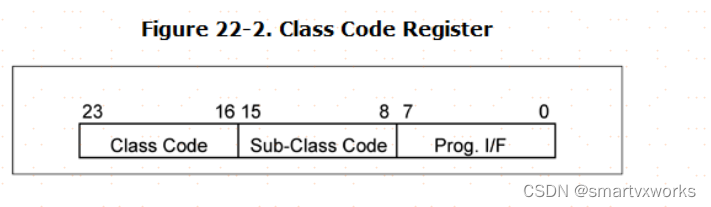

2.2 Class寄存器

这个寄存器属于PCI兼容寄存器,要求强制实现。如下图,它是个24bits的只读存储器, 分为3个区域:基类、子类和编程接口。用于确定该功能的基本功能和功能更为明确的 子类,以及在某些情况下的寄存器专用编程接口。

高字节用于定义该功能的基类;

中间字节用于定义基类中的子类;

低字节用于定义编程接口。

下表列出了当前新定义的基类代码:

下表列出了当前新定义的基类代码:

当操作系统试图与类驱动程序一起工作的功能时,类代码寄存器很有用。操作系统能找 出一个具有基类代码和子类代码的功能,驱动程序就能与该功能一起工作。类驱动程序 比制造商提供的仅与某个特定功能一起工作的驱动程序更具灵活性。编程接口字节:为准确识别寄存器组的布局提供了最终的尺度。

2.3 Cache Line Size 寄存器

该寄存器记录CPU使用的 Cache 行长度。在 PCI 总线中和 Cache 相关的总线事务,如 存储器写并无效和 Cache 多行读等总线事务需要使用这个寄存器。值得注意的是,该寄 存器由系统软件设置,但是在 PCI 设备的运行过程中,只有其硬件逻辑才会使用该寄存 器,比如 PCI 设备的硬件逻辑需要得知处理器系统 Cache 行的大小,才能进行存储器写 并无效总线事务,单行读和多行读总线事务。

如果 PCI 设备不支持与 Cache 相关的总线事务,系统软件可以不设置该寄存器,此时该 寄存器为初始值0x00。对于 PCIe 设备,该寄存器的值无意义,因为 PCIe 设备在进行数 据传送时,在其报文中含有一次数据传送的大小,PCIe 总线控制器可以使用这个“大小”, 判断数据区域与 Cache 行的对应关系。

2.4 Subsystem ID 和 Subsystem Vendor ID 寄存器

这两个寄存器和Device ID和Vendor ID类似,也是记录PCI设备的生产厂商和设备名 称。 但是这两个寄存器和Device ID与Vendor ID 寄存器略有不同。例如Xilinx公司在 FGPA 中集成了一个PCIe总线接口的 IP 核,即 LogiCORE。用户可以使用LogiCORE 设 计各种各样基于PCIe 总线的设备,但是这些设备的 Device ID 都是0x10EE,而Vendor ID 为0x0007[3]。这里即可使用Subsystem ID和Subsystem Vendor ID 寄存器来区分这 些 设备。

2.5 Capabilities Pointer 寄存器

在 PCI 设备中,该寄存器是可选的,但是在 PCI-X 和 PCIe 设备中必须支持这个寄存 器,Capabilities Pointer 寄存器存放 Capabilities 寄存器组的基地址,PCI 设备使用 Capabilities 寄存器组存放一些与 PCI 设备相关的扩展配置信息。

2.6 Interrupt Line 寄存器

这个寄存器是系统软件对PCI设备进行配置时写入的,该寄存器记录当前PCI 设备使 用的中断向量号,设备驱动程序可以通过这个寄存器,判断当前 PCI 设备使用处理器系 统中的哪个中断向量号,并将驱动程序的中断服务例程注册到操作系统中。

2.7 Interrupt Pin 寄存器

这个寄存器保存 PCI 设备使用的中断引脚,PCI 总线提供了四个中断引脚 INTA#、 INTB#、INTC#和 INTD#。Interrupt Pin 寄存器为1时表示使用 INTA#引脚向中断控制器 提交中断请求,为2表示使用 INTB#,为3表示使用 INTC#,为4表示使用 INTD#。

如果 PCI 设备只有一个子设备时,该设备只能使用 INTA#;如果有多个子设备时,可以使 用 INTB~D#信号。如果 PCI 设备不使用这些中断引脚,向处理器提交中断请求时,该寄存 器的值必须为0。

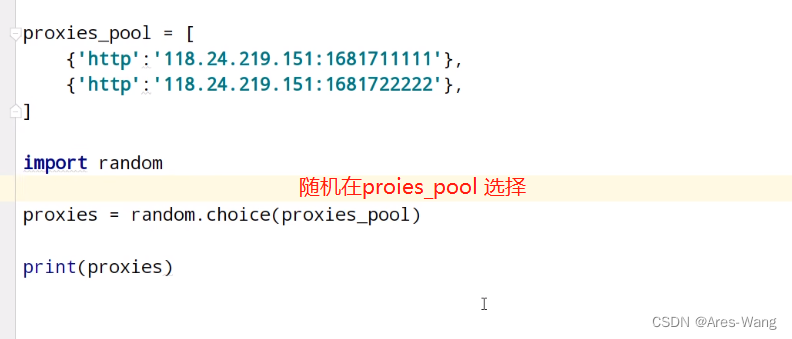

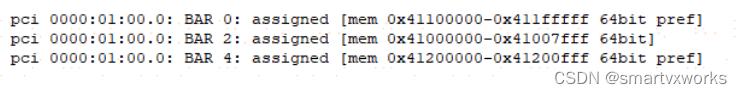

2.8 Base Address Register 0~5寄存器

该组寄存器简称为 BAR 寄存器,BAR 寄存器保存 PCI 设备使用的地址空间的基地址, 该基地址保存的是该设备在PCI总线域中的地址。其中每一个设备最多可以有6个基 址空间,但多数设备不会使用这么多组地址空间。

在 PCI 设备复位之后,该寄存器将存放 PCI 设备需要使用的基址空间大小,这段空间是 I/O 空间还是存储器空间,如果是存储器空间该空间是否可预取。

获得 PCI 设备使用的 BAR 空间的长度,其方法是向 BAR 寄存器写入0xFFFF-FFFF,之后 再读取该寄存器。

处理器访问 PCI 设备的 BAR 空间时,需要使用 BAR 寄存器提供的基地址。值得注意的 是,处理器使用存储器域的地址,而 BAR 寄存器存放 PCI 总线域的地址。因此处理器系 统并不能直接使用“BAR 寄存器+偏移”的方式访问 PCI 设备的寄存器空间,而需要将 PCI 总线域的地址转换为存储器域的地址。

在 Linux 系统中,ioremap 函数的输入参数为存储器域的物理地址,而不能 使用 PCI 总 线域的物理地址。

而在 pci_dev->resource[bar].start 参数中保存的地址已经经过 PCI 总线域到存储器域 的地址转换,因此在编写 Linux 系统的设备驱动程序时,需要使用 pci_dev->resource[bar].start 参数中的物理地址,然后再经过 ioremap 函数将物理地址 转换为“存储器域”的虚拟地址。

WIFI chip 7906 BAR空间:

2.9 Command 寄存器

该寄存器为 PCI 设备的命令寄存器,该寄存器在初始化时,其值为0,此时这个 PCI 设备 除了能够接收配置请求总线事务之外,不能接收任何存储器或者 I/O 请求。系统软件需 要合理设置该寄存器之后,才能访问该设备的存储器或者 I/O 空间。在 Linux 系统中, 设备驱动程序调用 pci_enable_device 函数,使能该寄存器的 I/O 和 Memory Space 位 之后,才能访问该设备的存储器或者 I/O 地址空间。

2.10 Status 寄存器

该寄存器的绝大多数位都是只读位,保存 PCI 设备的状态。

2.11 Latency Timer 寄存器

在 PCI 总线中,多个设备共享同一条总线带宽。该寄存器用来控制 PCI 设备占用 PCI 总线的时间,当 PCI 设备获得总线使用权,并使能 Frame#信号后,Latency Timer 寄存器 将递减,当该寄存器归零后,该设备将使用超时机制停止[6]对当前总线的使用。

如果当前总线事务为 Memeory Write and Invalidate 时,需要保证对一个完整 Cache行 的操作结束后才能停止当前总线事务。对于多数 PCI 设备而言,该寄存器的值为32或 者64,以保证一次突发传送的基本单位为一个 Cache 行。

PCIe 设备不需要使用该寄存器,该寄存器的值必须为0。因为 PCIe 总线的仲裁方法与 PCI 总线不同,使用的连接方法也与 PCI 总线不同。

3.Header Type1

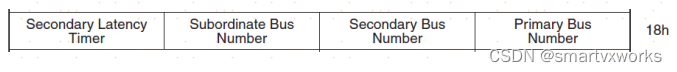

- Subordinate Bus Number、Secondary Bus Number 和 Primary Bus Number 寄存器

- Primary Bus Number:代表朝向RC方向的PCI 总线号。

- Secondary Bus Number:代表下游链路的PCI 总线号。

- Subordinate Bus Number:代表了下游端口上最高(大)的总线号。当没有接桥的时候,二级总线号和从属总线号是一样的值。

3.1 Secondary Status 寄存器

该寄存器的含义与 PCI Agent 配置空间的 Status 寄存器的含义相近,PCI 桥的 Secondary Status 寄存器记录 Secondary Bus 的状态,而不是 PCI 桥作为 PCI 设备时使用的状态。

3.2 Secondary Latency Timer 寄存器

该寄存器的含义与 PCI Agent 配置空间的 Latency Timer 寄存器的含义相近,PCI 桥的Secondary Latency Timer 寄存器管理 Secondary Bus 的超时机制,即 PCI 桥发向下游的总线事务;在 PCI 桥配置空间中还存在一个 Latency Timer 寄存器,该寄存器管理 PCI 桥发向上游的总线事务。

3.3 I/O Limit 和 I/O Base 寄存器

在 PCI 桥下设备的IO资源基地址和大小。

3.4 Memory Limit 和 Memory Base 寄存器

在 PCI 桥下设备的mem资源基地址和大小。

3.5 Prefetchable Memory Limit 和 Prefetchable Memory Base 寄存器

在 PCI 桥管理的 PCI 子树中有许多 PCI 设备,如果这些 PCI 设备支持预读,则需要从PCI 桥的可预读空间中获取地址空间。PCI 桥的这两个寄存器存放这些 PCI 设备使用的,可预取存储器空间的基地址和大小。

如果 PCI 桥不支持预读,则其下支持预读的 PCI 设备需要从 Memory Base 寄存器为基地址的存储器空间中获取地址空间。如果 PCI 桥支持预读,其下的 PCI 设备需要根据情况,决定使用可预读空间,还是不可预读空间。PCI 总线建议 PCI 设备支持预读,但是支持预读的PCI 设备并不多见。

3.6 I/O Base Upper 16 Bits and I/O Limit Upper 16寄存器

如果 PCI 桥仅支持16位的 I/O 端口,这组寄存器只读,且其值为0。如果 PCI 桥支持32位 I/O 端口,这组寄存器可以提供 I/O 端口的高16位地址。

3.7 Bridge Control Register

该寄存器用来管理 PCI 桥的 Secondary Bus,其主要位的描述如下。Secondary Bus Reset 位,第6位,可读写。当该位为1时,将使用下游总线提供的 RST#-信号复位与 PCI 桥的下游总线连接的 PCI 设备。通常情况下与 PCI 桥下游总线连接的PCI 设备,其复位信号需要与 PCI 桥提供的 RST#信号连接,而不能与 HOST 主桥提供的RST#信号连接。Primary Discard Timer 位,第8位,可读写。PCI 桥支持 Delayed 传送方式,当 PCI桥的 Primary 总线上的主设备使用 Delayed 方式进行数据传递时,PCI 桥使用 Retry 周期结束 Primary 总线的 Non-Posted 数据请求,并将这个 Non-Posted 数据请求转换为Delayed 数据请求,之后主设备需要择时重试相同的 Non-Posted 数据请求。当该位为1时,表示在 Primary Bus 上的主设备需要在2 ^10 个时钟周期之内重试这个数据请求,为0 ^15时,表示主设备需要在2 个时钟周期之内重试这个数据请求,否则 PCI 桥将丢弃 Delayed数据请求。

Secondary Discard Timer 位,第9位,可读写。当该位为1时,表示在 Secondary Bus 上的主设备需要在2 10 个时钟周期之内重试这个数据请求,为0时,表示主设备需要在2^15个时钟周期之内重试这个数据请求,如果主设备在规定的时间内没有进行重试时,PCI桥将丢弃 Delayed 数据请求。具体可参考PCI-to-PCI Bridge Architecture Specification Revision 1.2。

GC1610_AX3000 PCIe Header 拓扑: