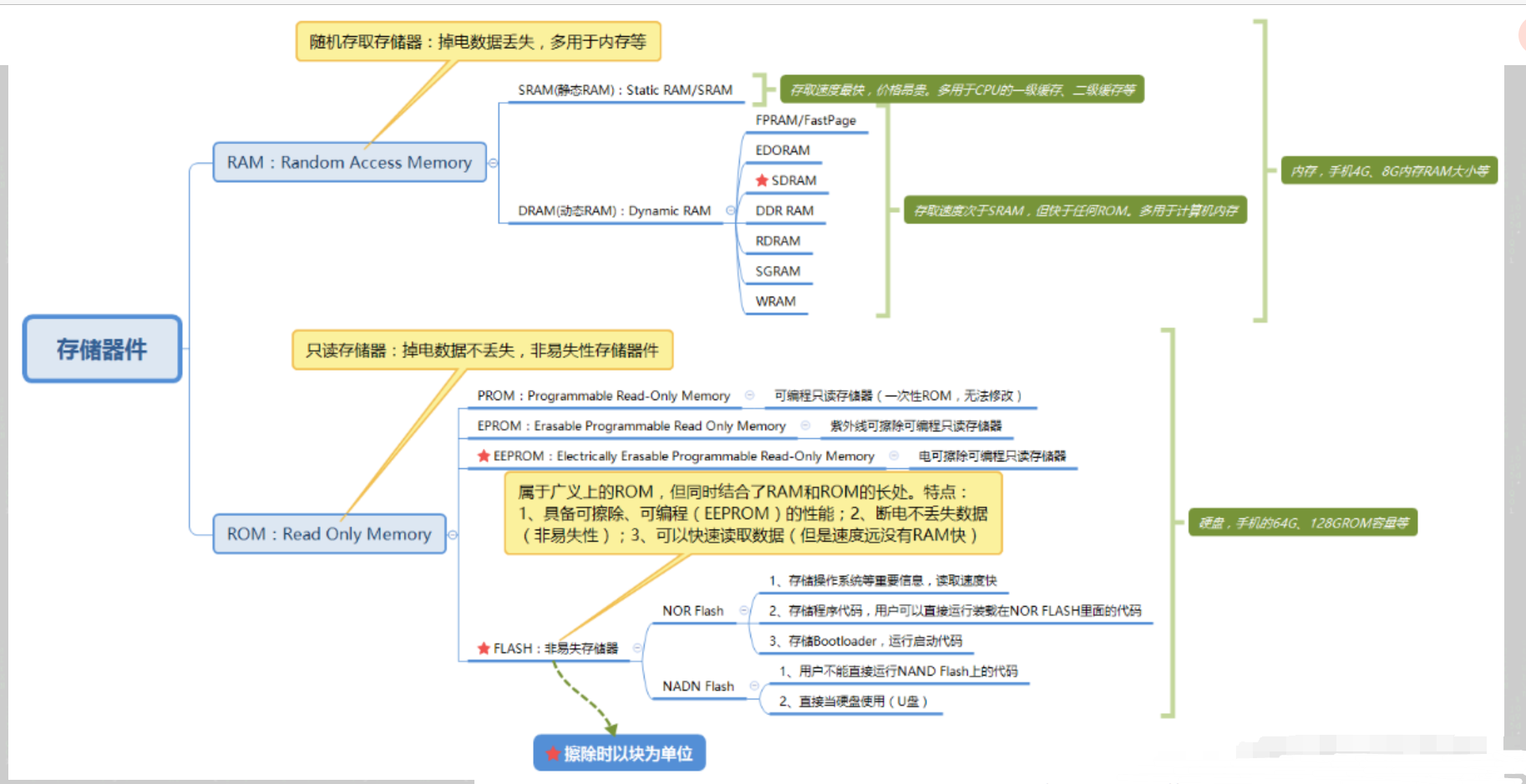

1、NandFlash的型号与命名

注:本文以S5PV210芯片和K9F2G08芯片做分析

(1)Nand的型号命名都有含义,拿K9F2G08来示例分析一下:K9F表示是三星公司的NandFlash系列。2G表示Nand的大小是2Gbit(256MB)。08表示Nand是8位的(8位就是数据线有8根)

(2)Nand命名中可以看出:厂家、系列型号、容量大小、数据位数。

2、NandFlash的结构框图

2.1、控制电路的总体描述:

整个NandFlash芯片由控制电路和存储颗粒组成,控制电路主要是和Soc进行对接,负责和Soc进行通信。NandFlash需要复杂的时序进行操作,需要接收Soc发送的命令,和Soc间进行传递数据,这些都是控制电路的功能。在上图中,右上角写有:2048M + 64M Bit的框图就是代表的存储介质,其余都是控制电路。

2.2、数据线:

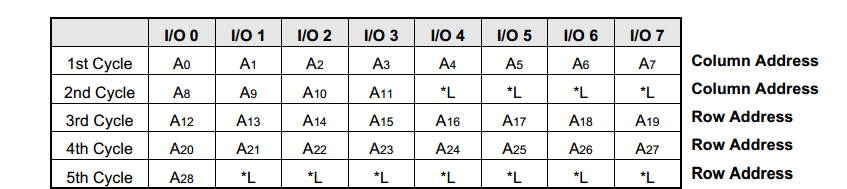

数据线就是用来传送数据的,对应于图中左下角(I/O 0 ——I/O 7),总共有8根地址线,所以这是8位的NandFlash,此外还有16bit的NandFlash。有几根地址线,一次传输的数据就是几位,但是数据线上传输的不仅仅是数据,还包括命令、地址。

2.3、寻址方式:

访问数据都是要先通过地址进行定位,在上图中可以看到有12根列地址线(A0-A11)和17根行地址线(A12-A28),总共29根地址线。数据线是8位,一次只能发送8bit,所以地址需要多个周期发送,上图显示的是5cycle发送,此外还有4cycle的。常说的几个cycle的NandFlash,就是指地址是几个周期发送完成。

3、NandFlash的存储介质:

3.1、页和块:

存储介质是矩阵式排列的,依靠行列进行寻址。页(page)、块(block)都是表示容量的单位,其中将上图中长方体横着切一刀就是一个页,一页的大小是(2K + 64)Byte,一个块等于64个页,整个设备(device)的存储容量等于2048个块。

3.2、寻址方式:

NandFlash是块设备,即读写以page为单位,擦除以block为单位,是不能读取单个字节的,哪怕只需要读取一个字节,也需要将该字节所在的page整个读出。但是需要注意,地址却是可以精确到字节的,所以读写NandFlash时要注意地址要以page地址对齐,擦除时要以block地址对齐,否则可能会出错。

3.3、带内数据和带外数据

上图中可以看到,page = (2K + 64)byte。2K是存储有效数据的,叫带内数据,也就是我们平时所说的容量;64字节是带外数据,是用来存储一些额外信息的,比如:坏块标志、ECC数据等。之所以会需要64字节的带外数据,是因为存储到NandFlash的数据是可能出错的,ECC数据就是读写的时候用来校验的,并且NandFlash随着使用时间的增多是会产生坏块,必须要标记坏块,在操作的时候避开坏块。64字节是用来存储一些冗余信息,保证数据的安全性。

4、NandFlash的常见操作和流程分析

4.1、Nand的命令码

这里的命令码是针对此款芯片的,不同的芯片命令码会有所不同,但是理解的方式是一样的。Soc想要和NandFlash间进行信息的交互,就要通过发送不同的命令码来控制NandFlash,命令码是由NandFlash提供的,命令码就相当于Soc和NandFlash之间的交互协议。比如read操作,需要在第一个周期发送00h,第二个周期发送30h;Block Erase(块擦除)需要第一个周期发送60h,第二个周期发送D0h。我们要进行相应的操作时,就按照上图,发送相应的命令码。命令码也是通过数据线发送的。

4.2、擦除操作:

上图就是擦除的流程图,此图要结合上面的命令码,其中60h和D0h刚好对应上擦除操作的命令码。

1.向NandFlash发送命令码60h;

2.通过多个周期发送地址(块对齐,擦除以块为单位);

3.发送命令码D0h;

4.读取NandFlash的状态寄存器

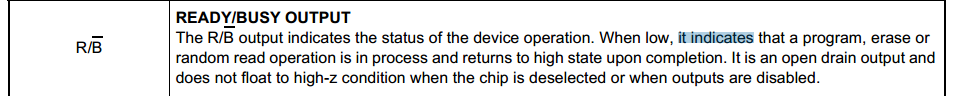

5.判断当前是否擦除完成,也就是查看状态寄存器的某些特殊位:I/O的第六位或者R/B位是否为1,如果是则再查看I/O的第一位是否为0。如果是则擦除完成,如果不是则擦除失败。

注:上面是R/B的描述,对应于状态寄存器的某一位。

4.3、坏块检测:

NandFlash是不能直接用的,因为NandFlash的稳定性不是特别好,容易有坏块,所以在使用之前要先进行坏块检测,提前标记好坏块,上图就是坏块检测的流程图:

1.首先将整个NandFlash进行擦除,这一步在上图中没有体现出来,相当于预处理。

2.将块地址设为0,即从第一个块开始检测。校验读出来的值是否是FFh(16位的NandFlash是FFFFh),如果是FFh则代表数据正确。如果不是FFh则表示数据不正确,这个块是坏块,需要创建坏块记录表或者在坏块记录表中记录此块为坏块。

3.如果不是最后一个块,增加块地址,重复以上操作,再读出数据进行校验,直到整个块校验完成。

4.已经校验完最后一个块,即整个坏块检测完成。

备注:擦除后的NandFlash,每个位的值都应该为1.

4.4、页写操作:

页是一次读写的最小单位,写的操作也是严格按照命令码来的。

1.发送80h;

2.多周期写地址(注意地址要页对齐);

3.写数据;

4.发送10h;

5.读取NandFlash的状态寄存器;

6.判断此次写操作是否成功:先查看I/O的第六位或者R/B位是否为1,如果是则再查看I/O的第一位是否为0。如果是则写成功,如果不是则写失败。

7.虚线框里是验证写进去的数据是否正确,如果有ECC校验码则不必进行后面的步骤。虚线框里的功能就是将刚才写进去的数据再读出来进行对比,看写进去的数据是否正确。

8.一般写数据时会产生ECC检验码,用来数据读出时进行校验数据是否出错。现在Soc的NandFlash控制有硬件ECC,就是在写数据时,开启硬件ECC功能,会由硬件产生ECC校验码,写入数据时,将ECC写到带外数据区即可。

4.5、页读操作:

页读操作相对简单,主要就是按照命令码发送命令去读取数据,然后进行ECC校验。

1.发送00h;

2.多周期写地址(页地址);

3.发送30h;

4.通过数据线读数据;

5.将读出来的数据进行校验,生成ECC校验码,和带外数据区的ECC校验码进行比较,看读出来的数据是否已经出错。带外数据区的ECC是写数据的时候生成的,用来和读出数据产生的ECC进行比对。

5、补充:为什么读NandFlash进行操作时,总要不停的去读状态寄存器?

首先要明白NandFlash是一个物理器件,不是理想化的模型。NandFlash根据命令完成操作时需要时间的,必须等到上一次操作完成才能进行下一次操作。不管是擦除、读写、检测坏块,归根到底要么是读出存储的数据要么是改变存储的数据。当读写NandFlash时,数据不会直接从地址处传输到数据线上,而是会先放到缓存区,再将缓存区的数据写入NandFlash或者将缓存区的数据通过数据线发送出去,这也是为什么需要读NandFlash的状态,来判断操作是否完成。

6、S5PV210的NandFlash控制器

6.1、结构框图

(1)最左边是系统总线,第二个是AHB时钟总线。NandFlash控制器是连接在AHB时钟总线上,然后再连接到系统总线上,其中就设计要给NandFlash控制器配置时钟频率;

(2)SFR代表的是特殊功能寄存器,操作NandFlash控制器就是去读写那些寄存器;

(3)ECC Gen:这是硬件ECC单元,负责ECC产生和校验的工作。NandFlash容易产生坏块,所以需要数据校验的机制,但是ECC是比较复杂的,如果用软件去ECC校验,那编写NandFlash控制器的代码就很复杂,于是Soc的生成厂商就把ECC功能做成硬件单元,降低使用NandFlash控制的难度,我们在编写初始化NandFlash控制器的代码时,只需要在操作操作相应寄存器把ECC功能配置好。

(4)Control & State Machine:控制和状态模块。我们通过NandFlash控制器和NandFlash控制器进行通信,Control模块负责给NandFlash发送命令,State Machine模块负责检测NandFlash的状态。NandFlash是物理器件,完成NandFlash控制发送的命令是需要时间的,NandFlash控制器在向NandFlash发送命令时,需要先检测NandFlash是否是空闲状态,如果NandFlash还在处理上一条命令,则现在不应该再发送新的命令。

(4)NAND FLASH Interface:NandFlash控制器的物理接口部分,就是在Soc和NandFlash芯片的硬件连接部分。I/O线总共有8根,说明NandFlash是并行接口,一次最多传送8bit数据,其余是控制信号线,具体查阅数据手册。

6.1、特殊功能寄存器

>上面是NandFlash控制器寄存器列表的部分截图,可以看到只有前面几个寄存器是控制、配置、命令、数据相关的寄存器,其余的寄存器都是和ECC功能相关。ECC功能是比较复杂的,如果不是专业从事NandFlash相关的工作一般是不太熟悉ECC的。我们NandFlash的使用者,对于ECC功能相关的寄存器就参照厂商提供的代码进行配置。

>上面是NandFlash控制器寄存器列表的部分截图,可以看到只有前面几个寄存器是控制、配置、命令、数据相关的寄存器,其余的寄存器都是和ECC功能相关。ECC功能是比较复杂的,如果不是专业从事NandFlash相关的工作一般是不太熟悉ECC的。我们NandFlash的使用者,对于ECC功能相关的寄存器就参照厂商提供的代码进行配置。