文章简介

本系列文章主要针对FPGA初学者编写,包括FPGA的模块书写、基础语法、状态机、RAM、UART、SPI、VGA、以及功能验证等。将每一个知识点作为一个章节进行讲解,旨在更快速的提升初学者在FPGA开发方面的能力,每一个章节中都有针对性的代码书写以及代码的讲解,可作为读者参考。

第十三章:RAM的使用

在FPGA中, 不得不提的是存储器, 当我们做相关项目时,经常会遇到存储数据的问题,数据量过大时,我们可以将其存储在 FPGA 芯片的外设存储器上,比如 sdram、 ddr sdram、 ddr3 sdram 等, 然而访问外设存储器相对比较麻烦,因此当数据量较小时,我们可以直接使用 FPGA 芯片内部自带的 ram 的 IP核。

Ram 是 random access memory 的简称,即随机存储器的意思, ram 可以按照所需进行随机读/写。我们可以通过调用 FPGA 内部的 IP 核生成一个 ram, 并通过编写 Verilog HDL 代码控制该 ram。

01 新建工程

打开ISE软件新建工程:File>>New Project。

先建立顶层文件,点击New Source,如图1箭头所指:

图1 新建New Source

在弹出的New Source Wizard中为模块命名以及选择存放路径,如图2所示:

图2 模块命名与路径

点击Next,最后点击Finish完成。此时在ISE界面可以看到生成的v文件,如图3所示:

图3 生成v文件

02 调用IP核

一种是通过Tools>>Core Generator调用。(第二种调用方法见文末注释)。

图4 IP核的调用

打开Core Generator的页面如图 5所示。

图5 打开 IP Core界面

点击 File>>New Project 弹出如图6所示的界面,根据图 6、 图 7 的标注进行相关的设置。

图6 器件选择

图7 语言选择

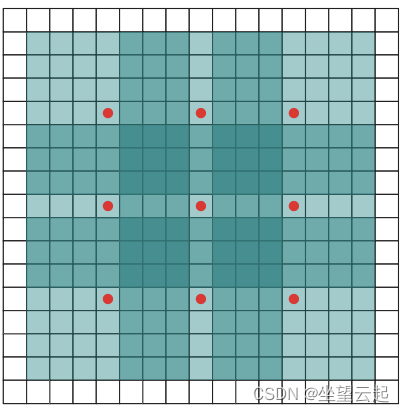

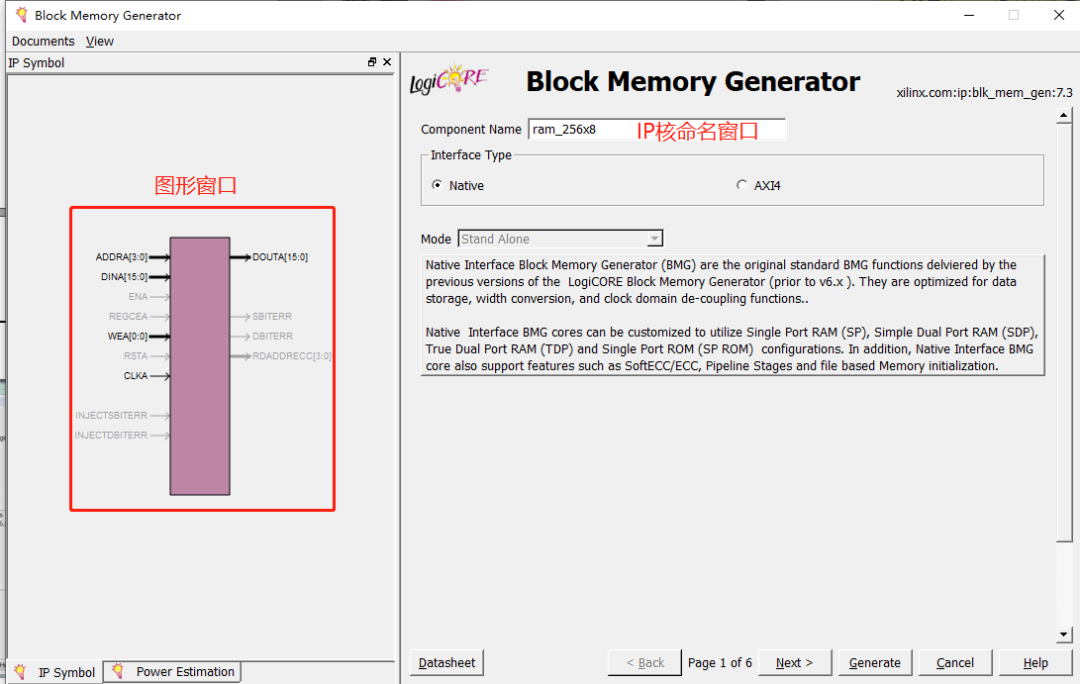

选择好了之后点击 OK 生成该 IP 核工程,可以在图 8 所示的窗口选择所需的IP 核, 在此我们选择 Memories&StorageElements>>RAMs&ROMs>>Block MemoryGenerator,鼠标左键双击该选项,弹出如图 10 所示的 ram IP 核窗口。

图8 IP核选择窗口

图9 双击选择RAM IP核

图10 RAM命名窗口

图11 RAM类型选择

在图 11 所示的窗口中选择所需的 ram 类型,在此我们选择 Simple Dual Port RAM, 该 ram 包含两个地址总线,一个写地址和一个读地址,分别控制两个地址总线可以控制该 ram 的读和写。

图12 RAM存储容量选择

根据图 12 所示来选择所需的 ram 数据的位宽和深度, 此处的数据位宽和深度都不是无限的,而是要根据芯片内部的资源来定的。

图13 RAM的其它设定

图 13 所示界面可以选择是否在 B 端(输出端) 加寄存器,加了寄存器可以使ram 输出的数据更稳定。若是需要该 ram 在被调取时被初始化,我们可以勾选图 13 标出的区域,并且加入 ram 可以识别的初始文件(coe 文件)。

图14 B端口复位的设定

若是需要对 B 端口设定复位键,可以在图 14 所示的区域勾选。

图15 调用RAM的信息

图 15 是我们调取该 IP 核的最后一步, 该界面主要总结了之间我们设定 ram,我们查看是否满足了我们的需求,若是没有满足可以退回到对应的位置重新选择,若是满足,点击 Generate 生成该 IP 核。

03 添加IP核文件到工程

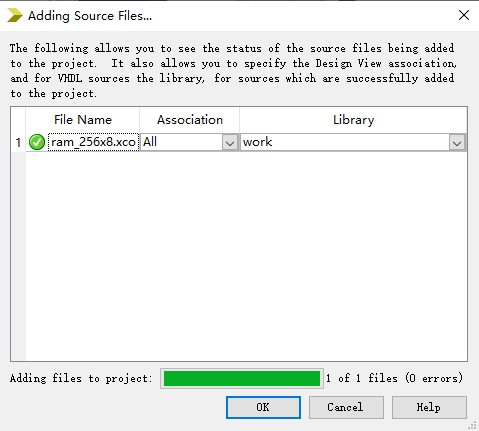

右键点击ISE中的工程名, 选择Adding Source 添加我们的IP核文件(xco),如图 16 所示。

图16 添加XCO文件到工程

之后弹出如图 17 所示的窗口,点击 OK 将该文件添加到工程。

图 17 添加文件到工程

04 编写顶层代码

接下来写出对该 ram 控制的 Verilog HDL 代码, 要求对该 ram 进行整体的读写交替进行。

代码示例1:

代码解析 1:

①第 16 行的 always 实现写使能(wr_en)的赋值, 当读的时候 wr_en 赋值0,写的时候 wr_en 为 1;

②第 24 行的 always 实现了写地址的产生;

③第 32 行的 always 实现了读地址的产生;

④第 41 行实现了该 ram IP 核的实例化。

05 编写测试代码

编写相应的测试文件, 具体如代码示例 2。

代码示例 2:

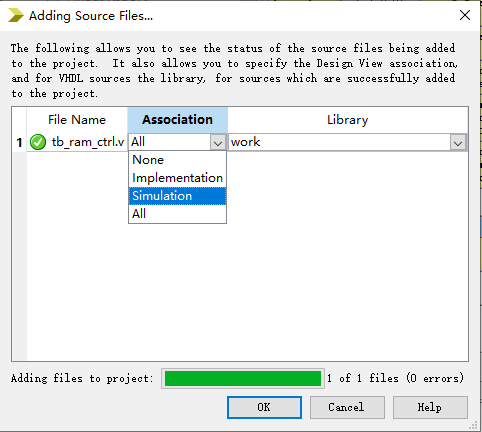

编写完测试代码后,需要将测试代码添加到工程中。

06 添加测试代码到工程

在 ISE 工程中右键工程名称添加测试文件(点击Add Source),在如图 18 所示的窗口中选择Simulation,点击OK。

图18 添加测试文件到工程

按照如图 19 所示的步骤打开 modelsim 软件进行仿真。

图19 通过 ISE 调取 modelsim 仿真软件

仿真波形如图 20 所示:

图20 仿真波形

07 注释

正文所讲调用IP核的方法过于繁琐,旨在让初学者了解IP核的调用步骤。

第二种方法与第一种本质上是一样的,但简便了许多。

点击Add Source,弹出如图 21 所示界面:

图21 选择IP核文件类型

点击Next,弹出如图22所示界面:

图22 选择RAM IP核

点击Next>>Finish完成。接下来的步骤与正文一致(图10开始),在此不在重复讲述。

![[大家的项目] 获取主机IP地址](https://img-blog.csdnimg.cn/img_convert/1dc783e0aba42b17b4dd105ea846d967.png)