1、下列错误的是 B

可编程I/O的1个banl只能设置1个电压

可编程I/O的1个bank只能设置一种电平标准

可编程I/O能够支持多种电平标准

可编程I/O支持三态输出

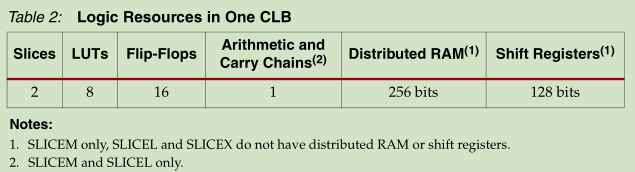

2、关于Slice说法错误的是 D

SliceM除具有存储功能外,还包括进位链、多路复用器、查找表LUT和可变长度的移位寄存器

Slice中含有多路复用器

SliceX不具有存储功能,也没有进位链

SliceL具有存储功能,也没有进位链

文档为ug384

3、FPGA仿真工具不包括 B

QuestaSim

Synplify

Modelsim

VCS

Synplify是逻辑综合工具

4、正确的是 D

FPGA是全称为复杂可编程逻辑器件

在INTEL公司生产的器件中,MAX7000属于FPGA

FPGA是基于乘积项结构的器件

基于SRAM的FPGA器件,每次上电后必须进行一次配置

FPGA全称为现场可编程逻辑器件,CPLD为复杂可编程逻辑器件;MAX7000是CPLD;GAL、CPLD之类都是基于乘积项的可编程结构,即包含有可编程与阵列和固定的或阵列的PAL(可编程阵列逻辑)器件构成。FPGA(现场可编程门阵列)是基于查找表的可编程逻辑结构。

5、关于HDL代码命名规范描述正确的是 B

可以使用破折号和连续的下划线

常量可以用小写字母

文件名应由字母、数字及下划线组成,首字符可以为数字

文件名和信号名不宜超过32个字符

不能使用破折号;C好像正确

6、DDIO可以实现两倍于工作时钟速率的信号传递,同时可以非常方便地实现时钟信号的()度相移输出

180

360

90

270

DDIO:Intel的Data Direct I/O 技术,不确定选啥

7、reg[3:0] mem[2:0] 定义的存储器为:A

3个4位寄存器

3个16位寄存器

4个3位寄存器

4个8位寄存器

8、寻址容量位16K(深度)8(位宽)的ram需要()根地址线 A

14

12

13

15

9、多bit信号跨时钟与操作正确的是 D

从低速时钟域到高速时钟域,可以不用打两拍

从低速时钟域到高速时钟域,也需要打两拍

从高速时钟域到低速时钟域,可以采用打两拍的方式

对于错误敏感的关键数据,最好用ram进行时钟域转换

单bit一般使用打拍的方式,多bit一般不用打拍的方式,一般使用fifo进行同步

10、根据以下语句,从选项中找出空括号应填入的正确答案。

reg【7:0】 B; B = 8‘bZ0;

则B = ()B

8'BZZZZ_0000

8'BZZZZ_ZZZ0

8'B0000_00Z0

8'B0000_ZZZ0

11、下列关于CPLD RAM资源说法正确的是()C

BRAM块只能构成固定宽度和深度的RAM

CPLD不能构成ROM

CPLD不能构成分布式RAM

可以将几个BRAM级联起来组成更大的RAM

CPLD是基于ROM结构的

12、关于锁存器说法正确的是:C

FPGA设计中尽量避免使用锁存器,ASIC设计中无需避免使用锁存器

FPGA与ASIC设计中无需避免使用锁存器

FPGA与ASIC设计中均尽量避免使用锁存器

FPGA设计中无需避免使用锁存器,ASIC设计中尽量避免使用锁存器

ASCI不确定

14、在边沿敏感的时序逻辑代码中使用()赋值,会导致综合前与综合后仿真结果不一样 A

阻塞

非阻塞

时序逻辑电路一般使用非阻塞语句,组合逻辑电路一般使用阻塞语句。

15、 FPGA内部的全局资源很有限,当只剩下1个全局时钟而有2个地方需要使用;一个是全局复位信号,另一个是模块的时钟信号,我们可以优先选择()占用全局资源 C

全局复位信号

管他呢,有系统工程师决定

模块的时钟信号

根据具体情况定

全局复位可以用异步复位同步释放来解决

16、INTEGER类型数据默认的位宽是多少 B

16

32

8

24

17、FPGA中不可以综合实现为RAM的资源是()B

BLOCK RAM

IO

LUT

FF

18、一个全流水的复数乘法器消耗的最小乘法器个数是()B

2

4

1

3

19、对于时钟和复位信号,正确的用法是:D

always @(negedge I_reset_n) begin...end

always @(posedge I_clock or negedge I_clock ) begin...end

always @(posedge I_clock) begin...end

always @(posedge I_clock or negedge I_reset_n) begin...end

20、关于亚稳态的说法,不正确的是 A

亚稳态持续时间成一定规律性

异步时钟域接口处触发器数量不足可导致亚稳态

指触发器无法在某个规定时间段内达到一个可确认的状态

setup time和hold time不满足可导致亚稳态

判断题

1、组合逻辑中不能用锁存器,时序逻辑中可以用锁存器 (错)

可以使用,但是应该避免使用

2、使用四个空格符缩排,可以使用TAB键 (对)

3、设计中所有的IO端口都需要进行管脚位置约束 (对)

4、逻辑模块调用,可以显示调用,也可以隐式调用,我们要求的是隐式调用 (错)

显示调用:按端口的定义顺序来调用;隐式调用:不按端口定义顺序调用

5、FPGA与DSP的区别是FPGA 适合算法规则的高速处理,DSP适合算法复杂,对处理速度要求不是很高 (对)

不定项选择

1、TTL与非门的空余输入端错误的处理方法是 AD

接高电平

通过1k欧电阻接高电平

空置

接地

通过1k欧电阻接地

TTL与门和与非门电路:对于TTL与门电路,只要电路输入端有低电平输入,输出就是低电平。只有输入端全为高电平时,输出才为高电平。对于TTL与非门而言,只要电路输入端有低电平输入,输出就为高电平,只有输入端全部为高电平时,输出才为低电平。根据其逻辑功能,当某输入端外接高电平时对其逻辑功能无影响,根据这一特点应采用以下四种方法:(1)将多余输入端接高电平,即通过限流电阻与电源相连接;(2)根据TTL门电路的输入特性可知,当外接电阻为大电阻时,其输入电压为高电平,这样可以把多余的输入端悬空,此时输入端相当于外接高电平;(3)通过大电阻(大于1kΩ)到地,这也相当于输入端外接高电平;(4)当TTL门电路的工作速度不高,信号源驱动能力较强,多余输入端也可与使用的输入端并联使用。

参考链接:https://blog.csdn.net/kevinhg/article/details/8695048

2、下列正确的是 BCD

相对于BRAM,分布式RAM的读写速度更快

分布式RAM由Slice中的LUT构成

相对于BRAM,分布式RAM对FPGA时序的影响更小

相对于BRAM,分布式RAM的更适合构成容量较小的RAM

block ram 的输出需要时钟,distributed ram在给出地址后既可输出数据。但也不确定DRAM就比BRAM更快,A选项不确定。

参考链接:https://blog.csdn.net/Reborn_Lee/article/details/80634881

https://blog.csdn.net/wordwarwordwar/article/details/103838437

3、可能产生latch的情况 CD

缺少begin...end

复位操作时,信号赋值是变量

if...else语句不完备

case语句中缺少default

4、可编程逻辑器件有哪些优点?ABCDE

可以减少产品体积,降低电源功耗

可以借助设计工具自动进行设计

设计灵活,易于修改升级

系统的器件使用数量大大减少

开发周期短

5、使用异步复位时候需要注意 ABD

异步复位信号时序不容易满足要求,需要代码设计时充分考虑

异步复位信号与时钟信号无关,需要保证复位信号干净无毛刺,以防出现误复位的情形

当释放异步复位信号时,该触发器时钟可能马上跳转,引起触发器的建立时间不够

由于异步复位与时钟无关,当释放异步复位后,由于时钟和复位信号传播的微小延时,可能会引起寄存器没有同时释放复位

C选项不确定

6、关于同步逻辑和异步逻辑正确的是 ABC

异步逻辑指逻辑电路中可能存在多个时钟信号或者不存在时钟信号,电路中一个逻辑的变化就可能引起整个电路逻辑的变化

告诉对外接口推荐使用同步逻辑

同步逻辑是指整个逻辑电路均在同一个时钟下工作,只有在时钟有效时逻辑的变化才会有效

同步逻辑优于异步逻辑

7、行为描述包括 AC

算法级

门级

系统级

RTL级

RTL级为数据流描述方式;门级和开关级属于结构化描述方式。

8、对于FPGA管脚输入信号的建立时间和保持时间约束说法正确的是 ACD

具体的约束值需要参考逻辑器件输入管脚实际测得的时钟数据的相位关系来确定

建立时间和保持时间无需约束

所有的同步输入信号都有进行Tsu约束和Th约束

约束的建立时间和保持时间小于实际测得的建立时间和保持时间,以保证一定的时序裕量容忍实际工作过程中存在的时序波动

9、CPLD和FPGA的区别 ABCD

一般情况下,CPLD的功耗比FPGA大,且集成度越高越明显

CPLD在系统断电时编程信息也不丢失

FPGA的集成度比CPLD高,具有更复杂的布线结构和逻辑实现

CPLD的编程采用E2PROM或FASTFLASH技术,无需外部存储器芯片,使用简单

参考链接:https://cloud.tencent.com/developer/news/373023

10、FPGA和CPLD的器件选型需要从哪些方面进行考虑 ABCD

存储器资源

可用IO管脚

逻辑资源

器件速度等级