目录

一、存储体系基本概念

二、主存储器的基本组成

三、SRAM和DRAM

四、只读存储器ROM

五、主存储器与CPU的连接

六、双端口RAM和多模块存储器

一、存储体系基本概念

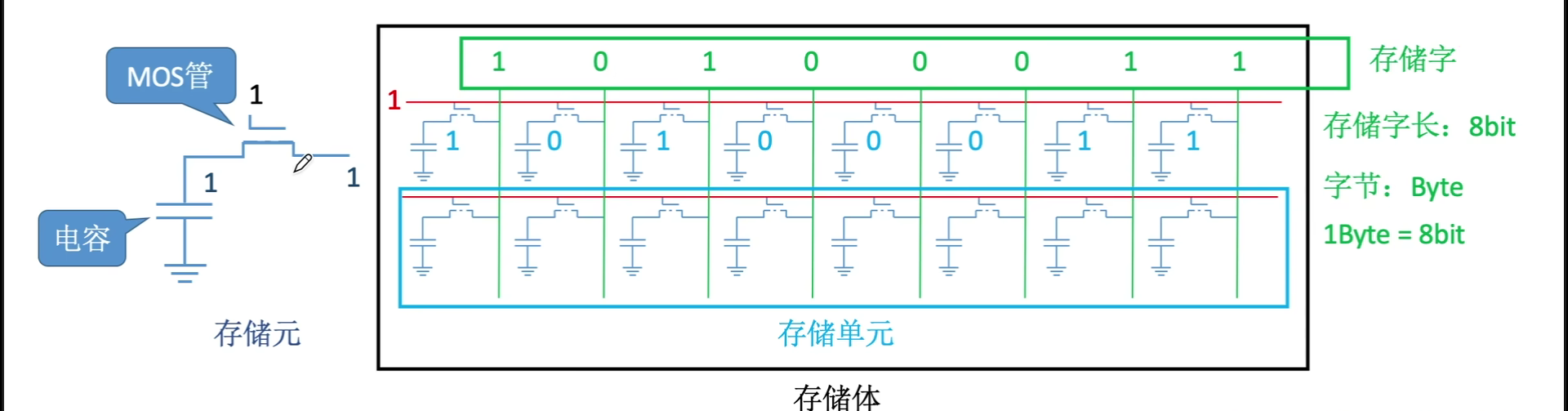

一个二进制位(bit)是构成存储器的最小单位;字节(8bit)是数据存储的基本单位。

单元地址是内存单元的唯一标识。

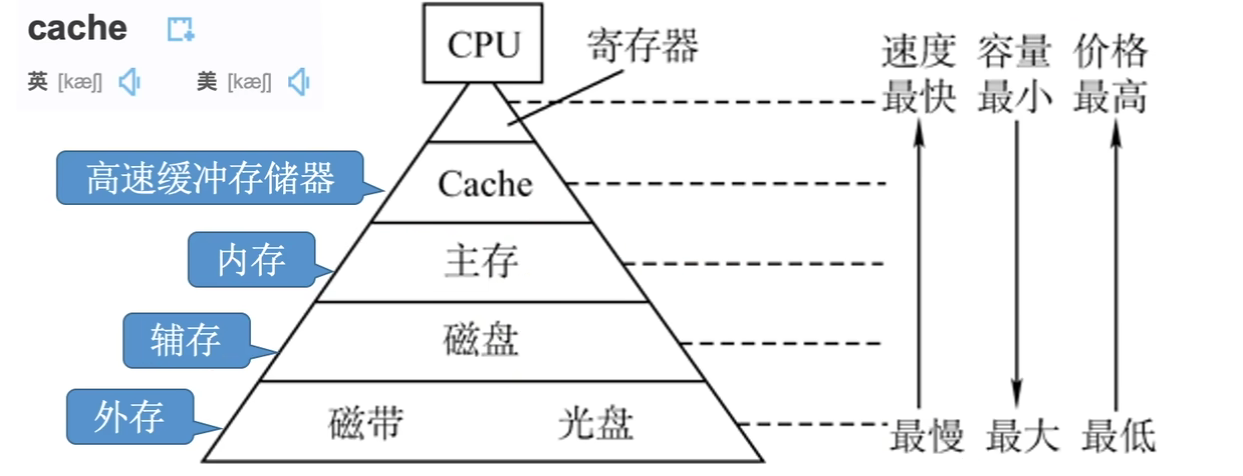

存储器的层次结构

主存——辅存:实现了虚拟存储系统,解决了主存容量不够的问题

主存——cache:解决了主存与CPU速度不匹配的问题

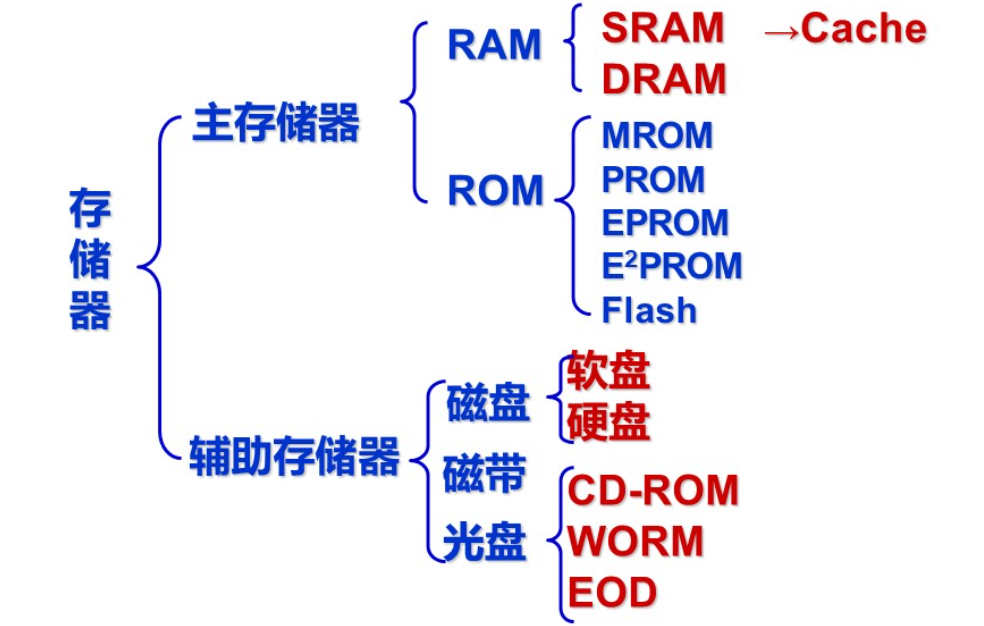

存储器的分类

按存储介质分类

半导体器件:半导体存储器(RAM、ROM,用作主存)

磁性材料:磁表面存储器(磁盘、磁带,用作辅存)

光介质:光盘存储器(用作辅存)

按存取方式分类

随机存取存储器 RAM:Random Access Memory,主存

顺序存取存储器 SAM:Sequential Addressed Storage,磁带

直接存取存储器 DAS:Direct Access Storage,磁盘、机械硬盘

相联存储器 CAM:Content Addressed Memory,按照内容检索存储位置进行读写

只读存储器 ROM:Read-Only Memory,事实上很多ROM也可以写入数据,只是比较麻烦

按信息的可保存性分类

易失性存储器:断电后,存储信息消失,如主存、Cache

非易失性存储器:断电后,存储信息保持,如光盘、磁盘

破坏性读出:信息读出后,原存储信息被破坏,如DRAM芯片,读出数据后要进行重写

非破坏性读出:信息读出后,原存储信息不被破坏,如SRAM芯片

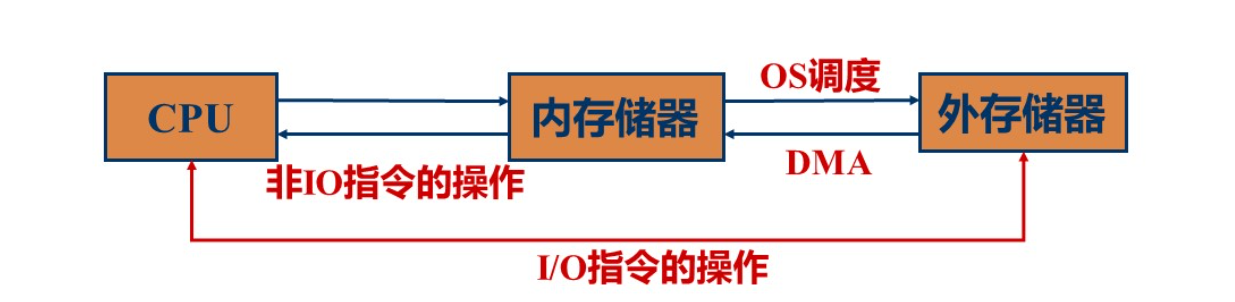

主存的地位:在现代计算机中,主存储器处于全机的中心地位。

主存的类型:要求为随机存取(RAM、ROM)

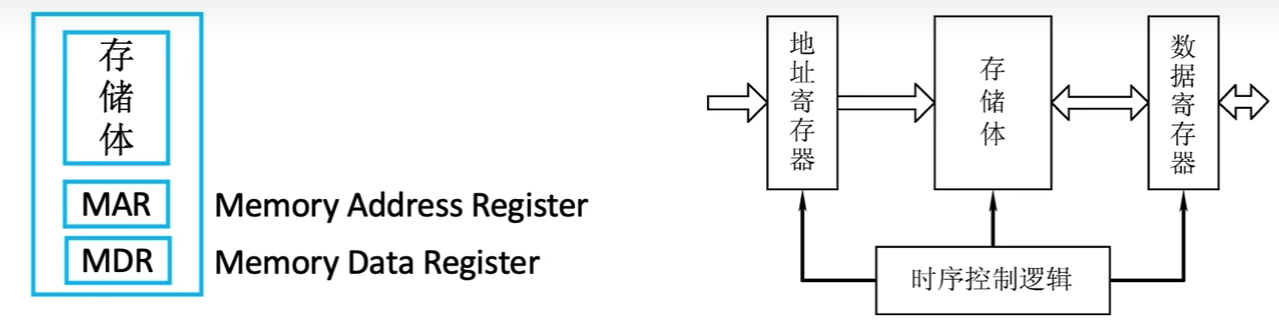

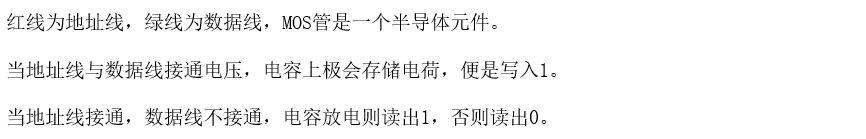

二、主存储器的基本组成

主存储器的性能指标

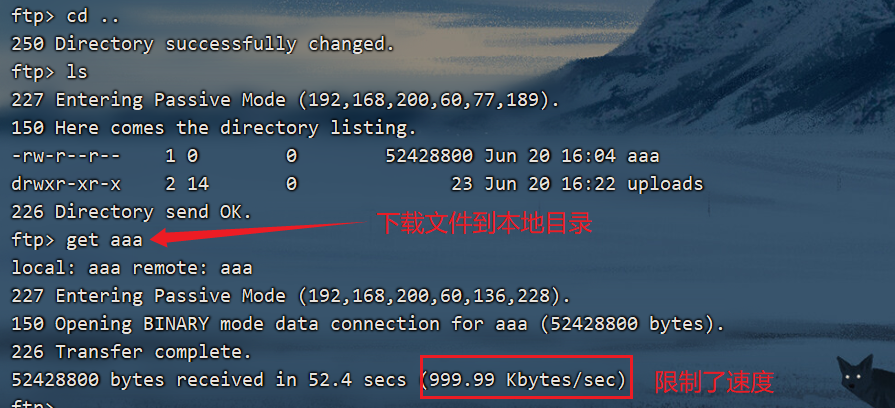

- 存取时间:从启动一次存储器操作到完成该操作所需的全部时间,单位 ns

- 存储周期:存储器进行连续两次独立的存储器操作所需的最小时间,通常为 2ms

- 存储器带宽:单位时间里存储器所能存取的最大信息量,单位 bit/s 或 B/s

存储器的性能指标不仅与存储器的存取速度有关,还与价格和耗电量有关。

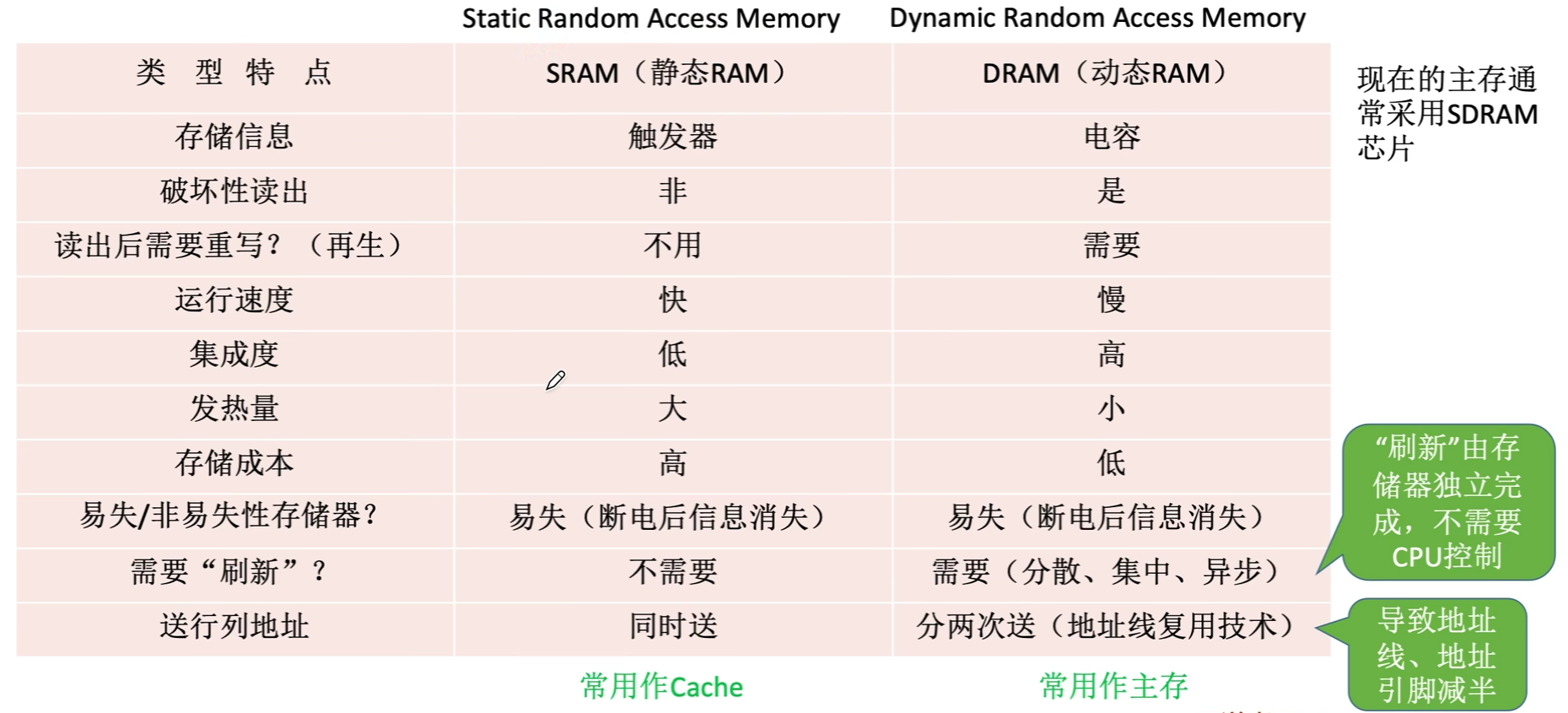

三、SRAM和DRAM

SRAM:Static Random Access Memory

DRAM:Dynamic Random Access Memory

DRAM用于主存,SRAM用于Cache

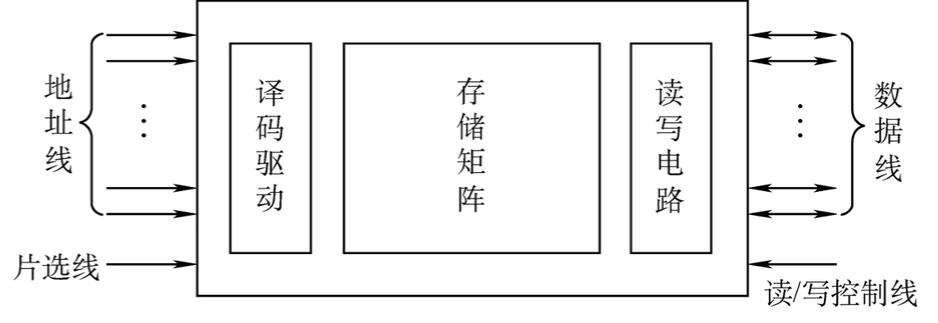

DRAM芯片:使用栅极电容存储信息

SRAM芯片:使用双稳态触发器存储信息

栅极电容与双稳态触发器

栅极电容:通过电容放电读出信息,是破坏性读出,读出后应有重写操作,也称“再生”

双稳态触发器:读出数据,触发器状态保持稳定,是非破坏性读出,无需重写

一个栅极电容读写1bit位需要1个MOS管,一个双稳态触发器读写1bit位需要6个MOS管,故栅极电容成本更低、功耗更低,即SRAM芯片成本更高

DRAM和SRAM都是易失性存储器,即断电后信息消失。

DRAM芯片需要刷新,SRAM芯片不需要刷新。

DRAM芯片采用栅极电容存储电荷,但是电荷会流失,电容内的电荷只能维持2ms,即便不断电,2ms后电荷信息也会消失,故栅极电容2ms内必须给电容充一次电,即“刷新”。

SRAM芯片采用双稳态触发器保存信息,只要不断电,触发器的状态就不会改变,故不需要“刷新”。

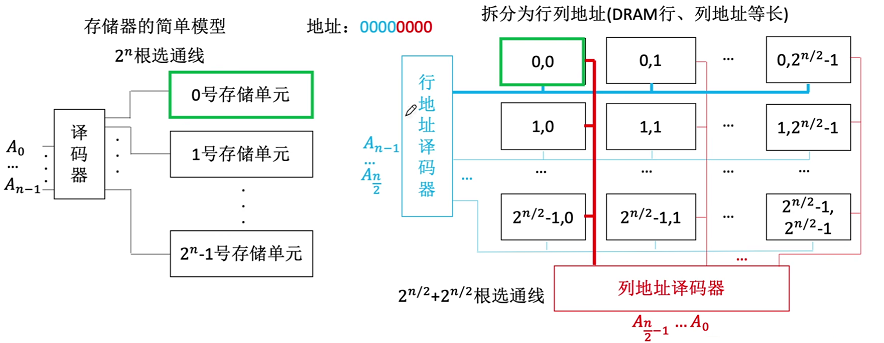

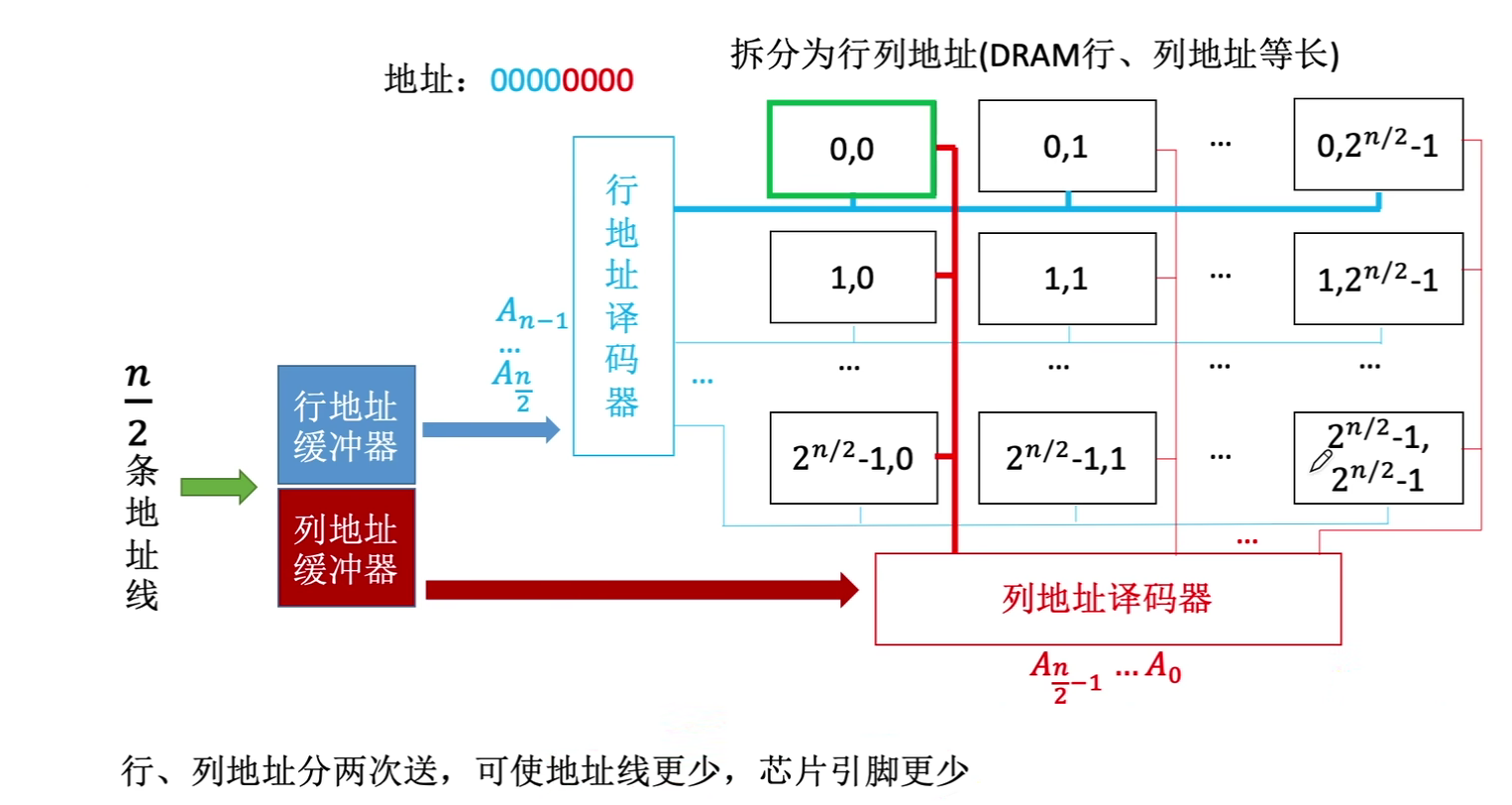

DRAM存储器的组成

DRAM存储器的地址以矩阵方式排列,分为行地址和列地址,目的是减少选通线的数量。

先传行地址,再传列地址。

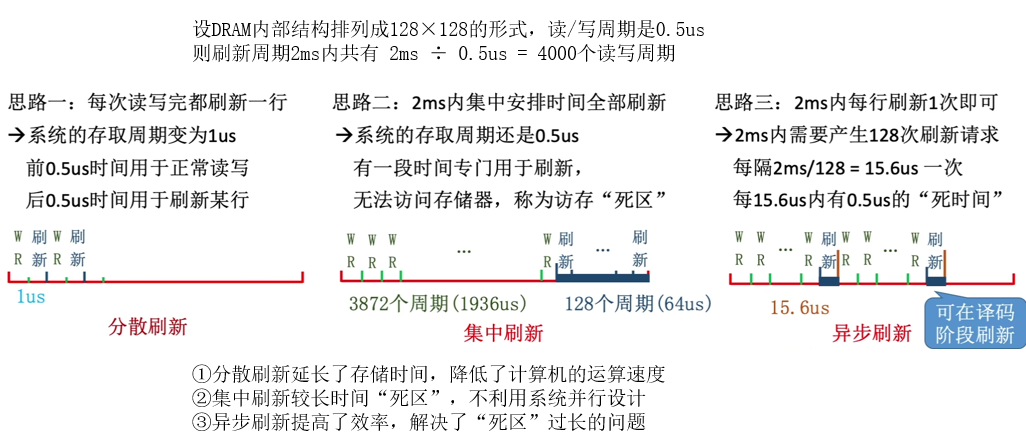

DRAM的刷新

刷新周期:一般为2ms

刷新单位:以行为单位,每次刷新一行存储单元

刷新方式:读出一行信息后重新写入,占用1个读/写周期

刷新策略

①分散式刷新:每次读写玩都刷新一次

②集中式刷新:2ms内集中安排时间全部刷新,有一段时间专门用于刷新,无法访问存储器,称为访存“死区”

③异步式刷新:2ms内每行刷新一次即可,在CPU不访问存储器阶段刷新,如译码阶段

DRAM的地址线复用技术

DRAM与SRAM对比

四、只读存储器ROM

RAM芯片:易失性,断电后数据消失

ROM芯片:非易失性,断电后数据不消失

ROM芯片类型

MROM——掩模式只读存储器:在芯片生产过程中直接写入数据,任何人不可重写(只能读出),可靠性高,灵活性差

PROM——可编程只读存储器:用户可用专门的PROM写入器写入数据,写一次后不可修改

EPROM——可擦除可编程只读存储器:用户写入信息后,可用某种方法擦除数据,可进行多次重写

UVEPROM——ultraviolet rays,紫外线照射,擦除全部信息

EEPROM——electrically,电擦除,擦除特定的字

Falsh Memory——闪存,如U盘、SD卡,可进行多次快速擦除重写,写入需要先擦除再写入,故写数据速度慢于读数据

SSD——固态硬盘:可进行多次快速擦除重写

五、主存储器与CPU的连接

传统计算机的MAR和MDR集成在主存储器上,现代计算机大多是将MAR和MDR集成在CPU上

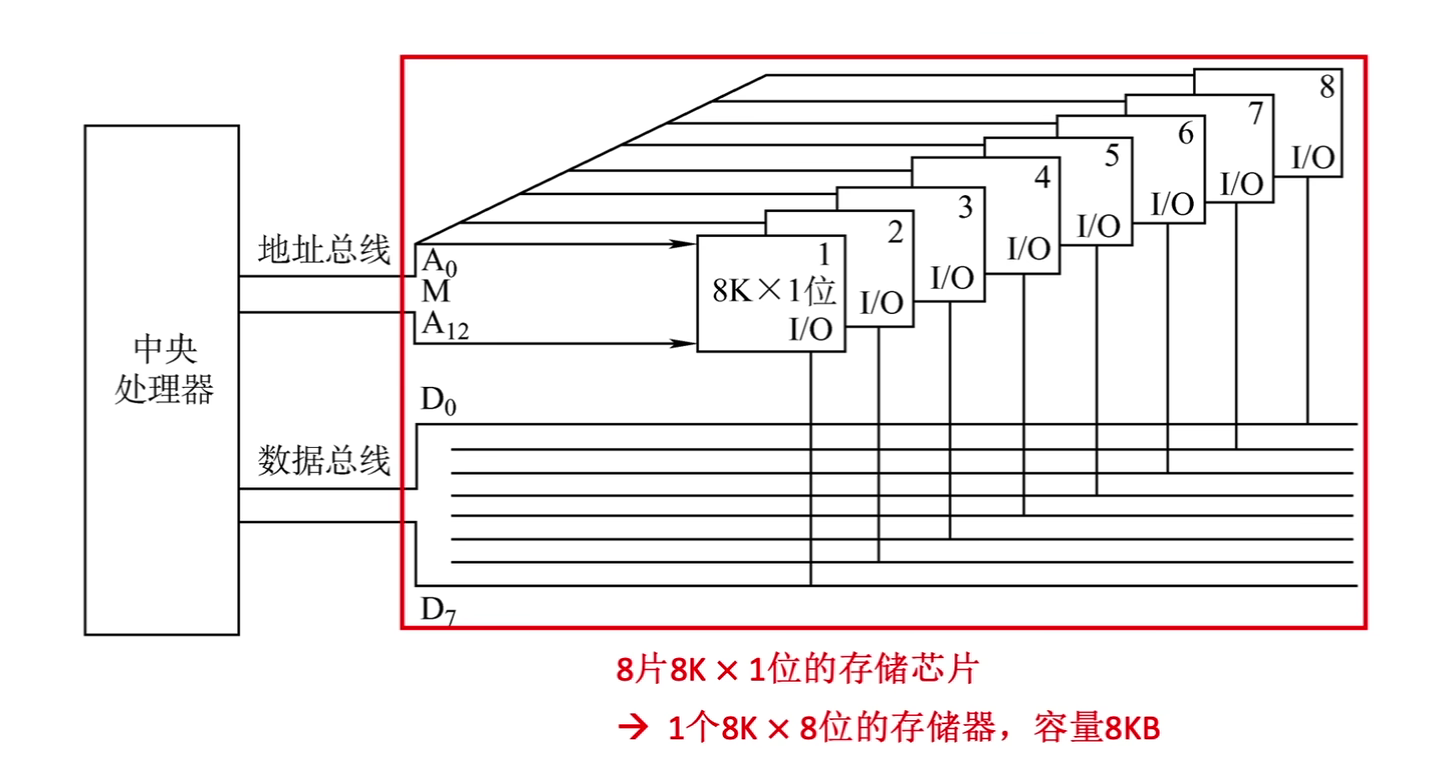

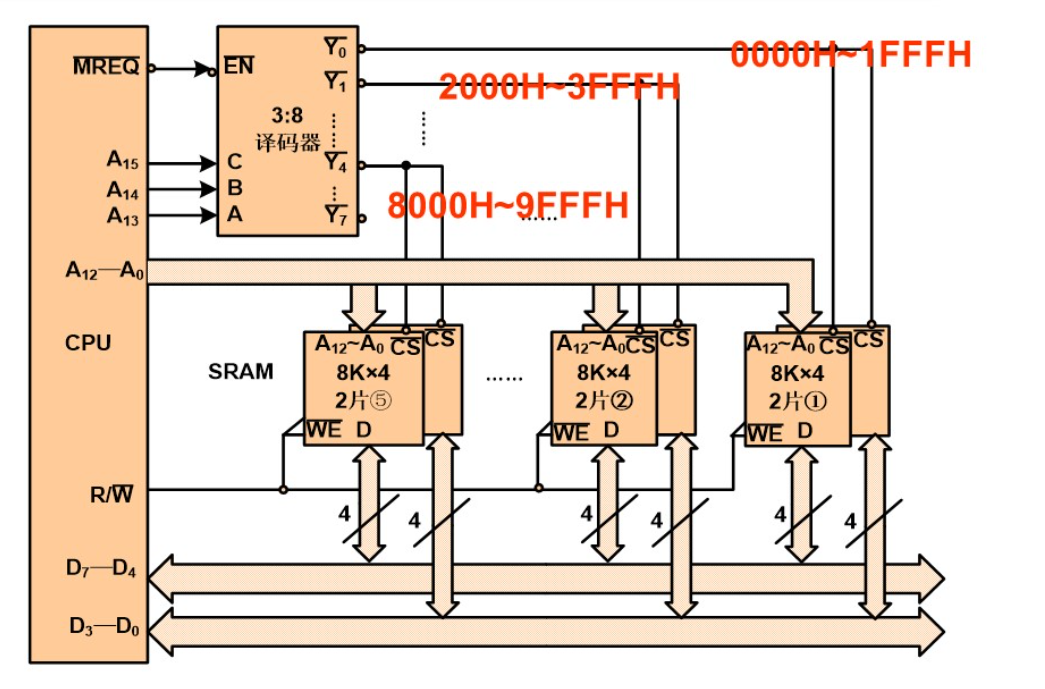

增加主存的存储字长——位扩展

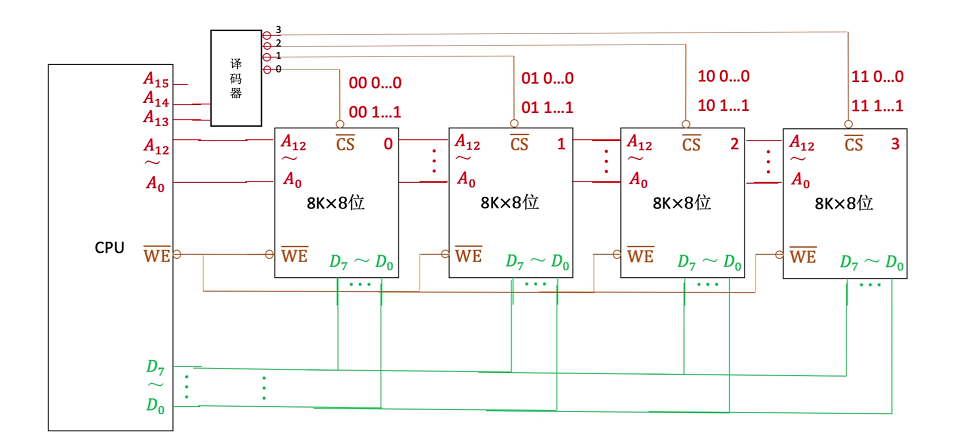

增加主存的存储字长——字扩展

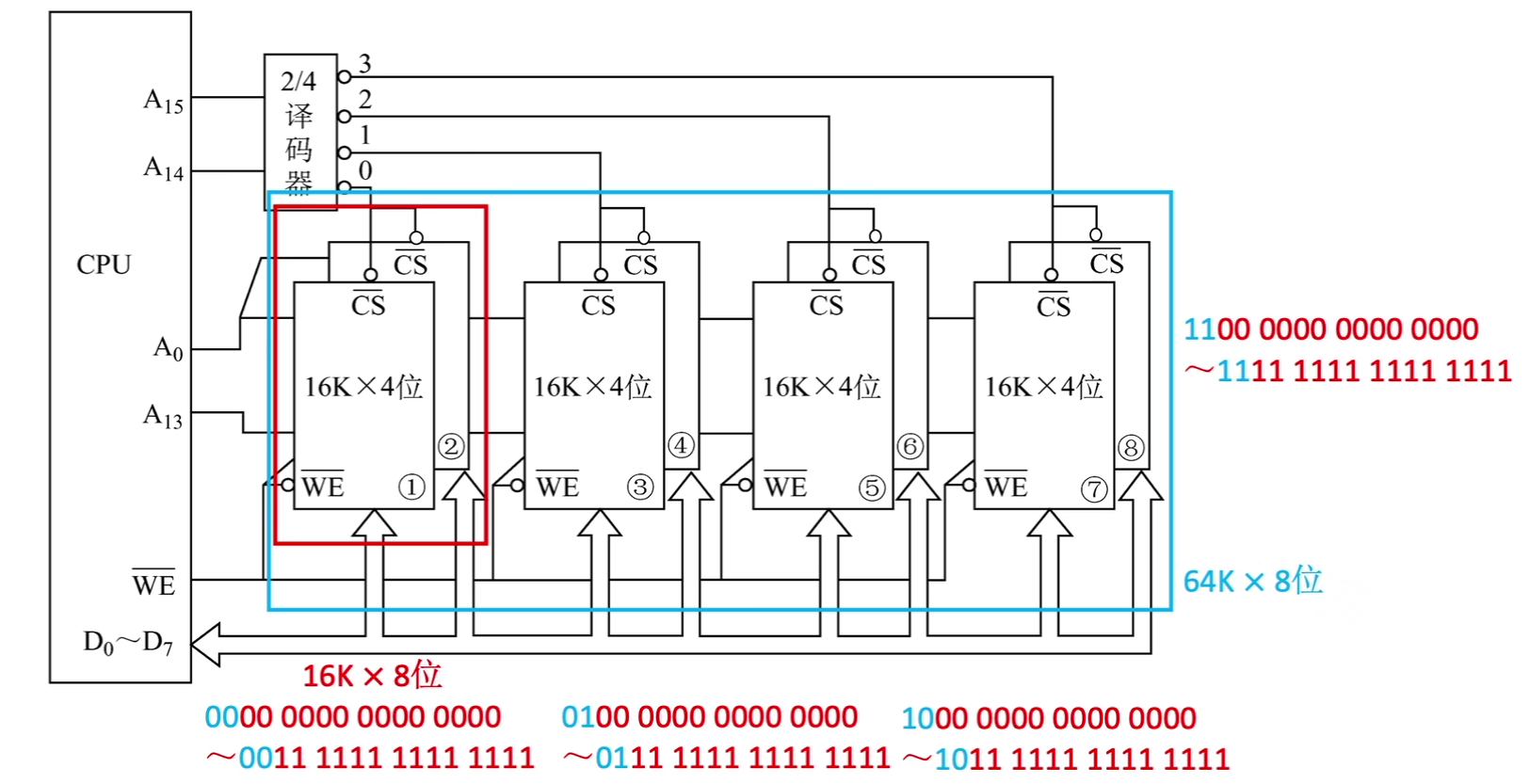

主存容量扩展——字位同时扩展

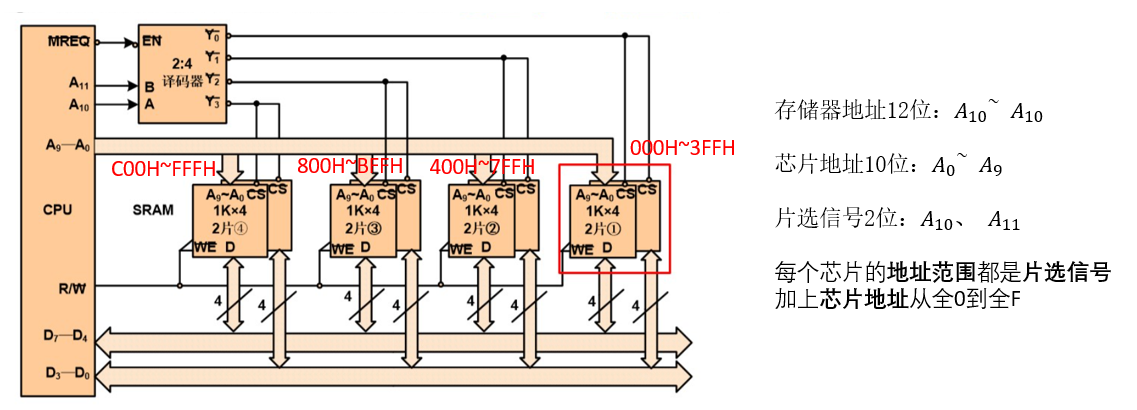

DRAM芯片地址空间范围

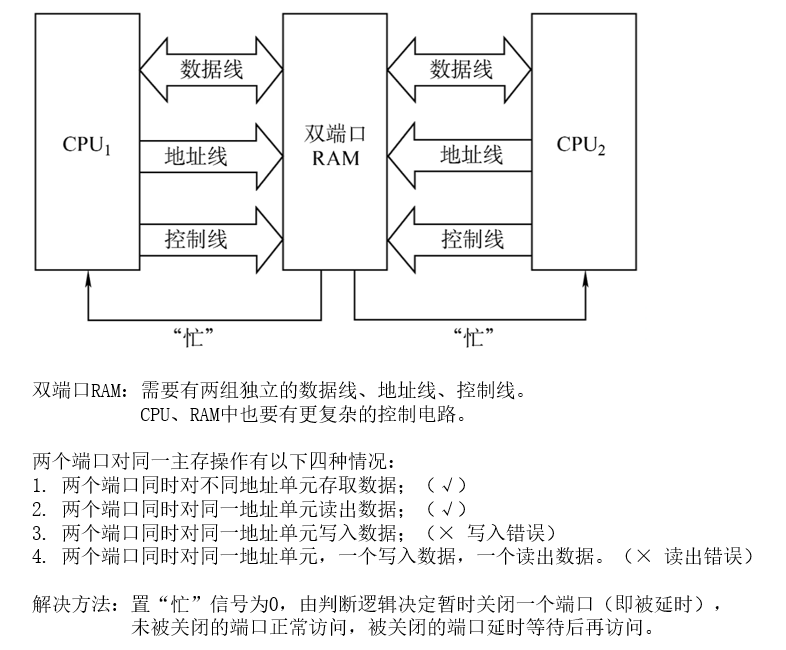

六、双端口RAM和多模块存储器

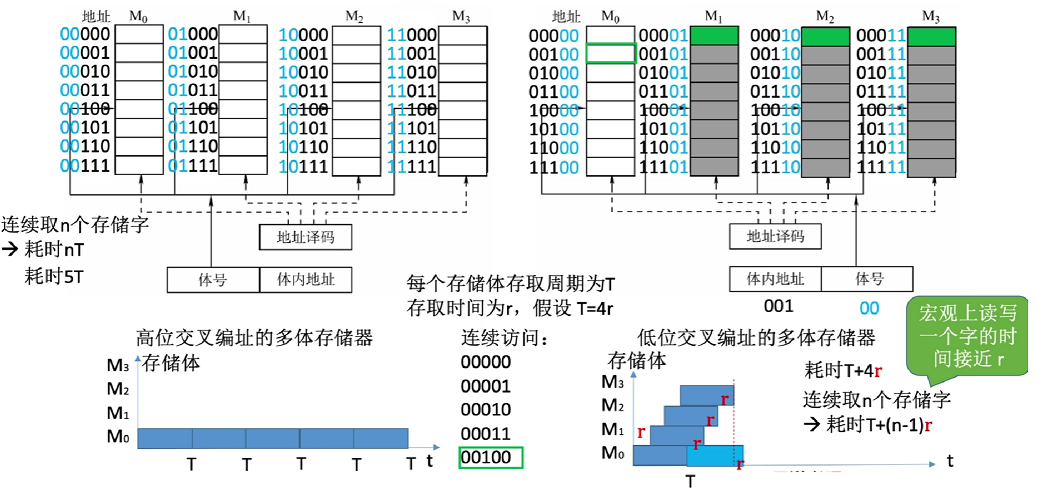

多体并行存储器

采用“流水线”的方式并行存取(宏观上并行,微观上串行)。

宏观上,一个存储周期内,m体交叉存储器可以提供的数据量是单个模块的m倍。

存取周期T,存取时间为r,为了使流水线不间断,应保证模块数 m≥T/r

存取周期 = 存取时间 + 恢复时间