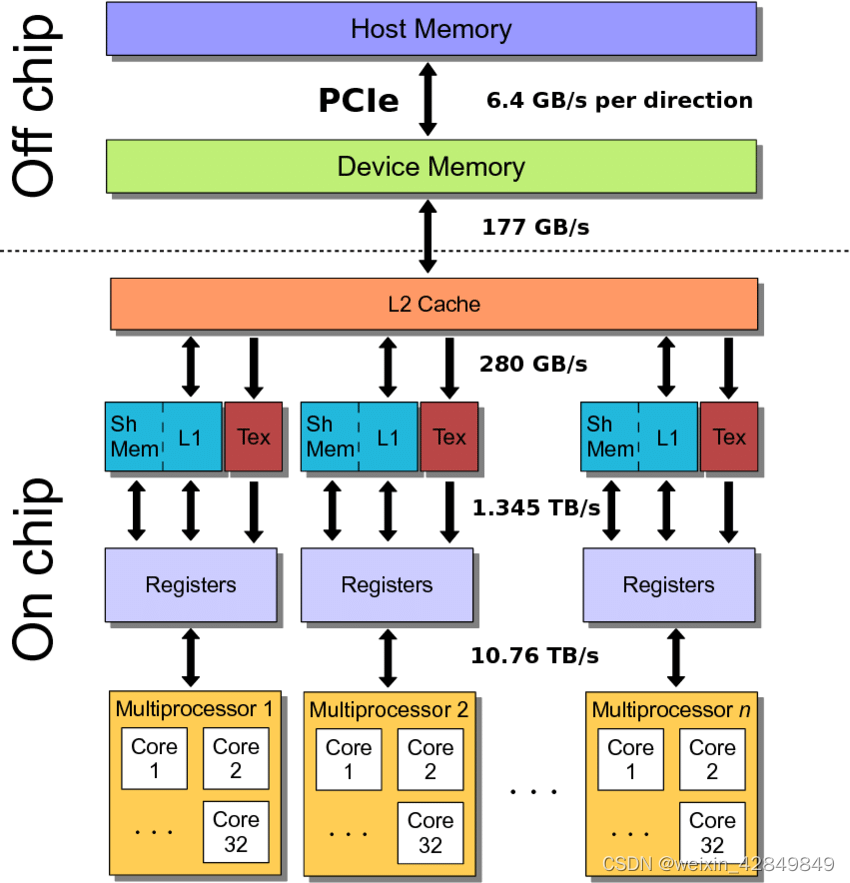

GPU内存架构示意

GPU架构示意图: 流处理器+内存

内存访问速度示意图

Kernel执行内存各部示意图

CUDA异构并行编程内存模型

对于一种并行语言、技术、或系统,可以从四个方面进行考虑

- 编程模型

- 执行模型

- 内存模型

- 硬件模型

其中内存模型包括内存资源的申请和释放,不同内存数据之间的移动,读写访问方式等。当前CPU处理器和GPU加速卡都配有多级高速缓存(CPU一般有L1D+L1T,L2,L3三级Cache缓存,GPU一般有L1,L2两级Cache),有些缓存资源对程序可见,比如GPU的共享内存(Shared Memory), 一些底层指令可以影响到数据读入和写出(Load/Store)使用缓存策略。大多数并行计算都需要处理大规模数据,其中多数可归类为内存访问密集型应用(memory-bound application),如何根据应用特点高效利用不同内存资源,使用合适读写策略,都会对整体性能产生很大影响。

本篇笔记对CPU和GPU上个内存相关资源进行分类介绍,依据CUDA开发手册资料,列出相关API函数,同时配有代码片段描述API函数使用方式和场景

系统内存(System Memory)

操作系统可直接管理的内存资源,主要指主板上配置的各类DDR内存。

系统内存使用

- malloc/free

- cudaHostAlloc/cudaHostFree

- cudaManagedMalloc

GPU卡上全局内存(Global Memory)/设备内存(Device Memory)

Constant Memroy(Device)

位于设备内存某处,Grid全局可见。只读方式访问,系统会将数据放在只读高速缓存内加速访问。

设备内存使用

- 申请和释放: cudaMalloc/cudaFree

- 申请和释放: cudaMallocAsync/cudaFreeAsync

- 数据移动: cudaMemcpy/cudaMemcpyAsync

- ZeroCopy

- UVM

GPU卡上缓存&SM流处理器上资源

L2 Cache(off-chip)

L1 Cache(on-chip,SM流处理器上)

Shared Memory(on-chip,SM流处理器上)

Registers File(on-chip,SM流处理器上)

Local Memory(Resigter Spilling)

参考资料

- Better Performance at Lower Occupancy Volkov 2010

- Better Performance at Lower Occupancy解读

- Benchmarking GPUs to Tune Dense Linear Algebra 2008

- Maximizing Unified Memory Performance in CUDA

- CUDA C Best Practices Guide: 9 Memory Optimization

- Local Memory and Register Spilling 2011