FPGA通过CPU远程升级方案

- 方案介绍

- 升级流程图

- 功能框图

- 例程实现

- AXI Quad SPI IP核的生成和配置

- Dual/Quad SPI Mode

- Legacy Mode

- Register Space (Legacy and Enhanced Non-XIPMode)

- Example Programming Sequence

- Write Enable Command Sequence

- Erase Command Sequence

- Write Data Command Sequence

- Read Data Command Sequence

- 约束文件xdc设置

- 在xdc文件中添加如下设置:

- Golden镜像设置

- Update镜像设置

- 参考文档:

方案介绍

本文介绍Xilinx提供的一种远程更新FPGA程序的方案,该方案是将FPGA外挂的FLASH芯片分为top、bottom两个部分,bottom存储golden程序,top存储update程序,golden区域通过JTAG配置原始的FPGA程序,其中包含升级的逻辑和上电跳转到update区域地址信息,CPU向FPGA发送升级程序通过升级逻辑将程序写入FLASH芯片的top区域。这样,FPGA每次上电通过跳转地址信息跳转到top区域加载update区域的程序,从而实现FPGA升级的功能。

升级流程图

这里跳转地址选择0xF50000。跳转地址是按照相关文档的例程的例子参考。

功能框图

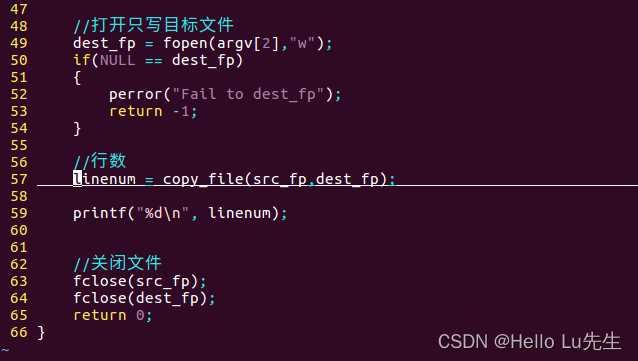

例程实现

由于Ultrascale系列FPGA的DQ0~DQ3规划到了FPGA的专用BANK0上面,而在使用BPI加载模式时, FPGA配置完成之后,BPI配置接口通常保持未使用状态,通过使用STARTUPE3原语,就可以使用这些专用引脚,所以可以将CPU写来的数据存储到flash芯片top部分,通过CPU设置FPGA从top部分加载程序,实现FPGA在线升级的功能。

AXI Quad SPI IP核的生成和配置

Dual/Quad SPI Mode

Dual SPI mode is selected when the Mode option in the Vivado IDE is set to Dual. The relevant parameters in this mode are:

• Mode

• Slave Device

• Enable STARTUPEn Primitive

Note: The STARTUPE2 primitive is applicable for 7 series devices. The STARTUPE3 primitive is applicable for UltraScale™ devices.

• Transaction Width

• No. of Slaves

• FIFO Depth

The properties associated with the FIFO are:

• The depth of the FIFO is based on the FIFO Depth option which has valid values of 16 or 256.

• The width of the FIFO is 8-bits because the page size of the SPI slave memories is always 8-bits.

• The quad SPI mode is selected when the Mode option is set to Quad. The behavior of the ports in quad SPI mode is:

• For standard mode SPI instructions, the IO0 and IO1 pins are unidirectional and function the same as in standard SPI mode.

• For dual mode SPI instructions, the IO0 and IO1 pins are unidirectional or bidirectional depending on the type of instruction and memory selected by setting the control register bits. The IO2 and IO3-bits are 3-state.

• For quad mode SPI instructions, the IO0, IO1, IO2, and IO3 pins are unidirectional or bidirectional depending on the type of memory used while transmitting the command, address, and data.

Legacy Mode

Legacy mode is selected when the Enable Performance Mode option in the Vivado Integrated Design Environment (IDE) is disabled. Legacy mode uses the AXI4-Lite interface and is fully backward compatible(向后兼容) with all the older versions of the AXI Quad SPI core in terms of functionality, register bit placement, and register access.

The AXI Quad SPI core, when configured in Dual/Quad SPI mode, this core supports additional pins for interfacing with external memory. These additional pins are used while transmitting the command, address, and data based on the control register settings and command used.

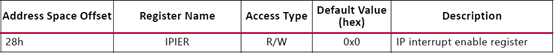

Register Space (Legacy and Enhanced Non-XIPMode)

Note: The AXI4-Lite write access register is updated by the 32-bit AXI Write Data (_wdata) signal. For a Write, both the AXI Write Address Valid (_awvalid) and AXI Write Data Valid (*_wvalid) signals should be asserted together.

Notes:

- The power-on reset data in the SPI DRR is unknown or all zeros. This register should not be considered for power-on reset conditions.

- Exists only when FIFO Depth is set to 16 or 256.

- TOW = Toggle on write. Writing a 1 to a bit position within the register causes the corresponding bit position in the register to toggle.

This table shows the set of registers applicable whether or not Enable Performance Mode is selected and Enable XIP Mode is not selected. Some AXI Quad SPI core registers should be accessed individually. These registers are configurable and accessible through either the AXI4-Lite interface or the AXI4 interface (enhanced mode). All registers are accessed as 32-bit.

Example Programming Sequence

The following steps briefly describe the erase, write and read command sequence for SPI flash.

Note: [1] The WRITE ENABLE command must be issued before every write transaction (erase/write data to the flash/register write of flash) command to the flash.

Note: [2] The following programming sequence is based on the 24-bit addressing mode of flash and assumes there is only one slave connected to the AXI QUAD SPI core.

Write Enable Command Sequence

- Disable the master transaction by asserting the master inhibit bit of SPICR (60h), and reset the RX and TX FIFOs through SPICR.

- Issue the write enable command by writing 0x06 into SPIDTR.

- Issue chip select by writing 0x00 to SPISSR(70h).

- Enable master transaction by deasserting the SPICR master inhibit bit.

- Deassert chip select by writing 0x01 to SPISSR.

- Disable master transaction by asserting the SPICR master inhibit bit.

Erase Command Sequence

- Reset RX and TX FIFOs through SPICR.

- Issue sector erase command into SPIDTR to erase any specific sector followed by the flash sector address or issue the bulk erase command to erase the entire flash followed by the flash base address.

- Issue chip select by writing 0x00 to SPISSR.

- Enable master transaction by deasserting the SPICR master inhibit bit.

- Deassert chip select by writing 0x01 to SPISSR.

- Disable master transaction by asserting the SPICR master inhibit bit.

Write Data Command Sequence

- Reset RX and TX FIFOs through SPICR.

- Issue the write data command into SPIDTR, to write data into any specific sector

followed by the flash sector address. - Fill SPIDTR with the data to be written to flash; the maximum data size depends upon the configured QSPI FIFO size.

- Issue chip select by writing 0x00 to SPISSR.

- Enable master transaction by deasserting the SPICR master inhibit bit.

- Deassert chip select by writing 0x01 to SPISSR.

- Disable master transaction by asserting the SPICR master inhibit bit.

Read Data Command Sequence

- Reset RX and TX FIFOs through SPICR.

- Issue the read data command into SPIDTR to read data from any specific sector followed by the flash sector address.

- Fill SPIDTR with the dummy data to read required data from the flash.

- Issue chip select by writing 0x00 to SPISSR(70h).

- Enable master transaction by deasserting the SPICR master inhibit bit.

- Deassert chip select by writing 0x01 to SPISSR.

- Disable master transaction by asserting SPICR master inhibit bit.

- Read SPIDRR, to get the Read data that is received from the SPI bus.

- Refer to the respective SPI slave (flash) data sheet to know which commands to issue.

- Write/Read commands vary with respect to the mode (Standard/Dual/Quad) used.

约束文件xdc设置

在xdc文件中添加如下设置:

set_property BITSTREAM.CONFIG.CONFIGRATE 33 [current_design]

set_property BITSTREAM.CONFIG.SPI_32BIT_ADDR YES [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property BITSTREAM.CONFIG.SPI_FALL_EDGE YES [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.TIMER_CFG 0x8000000 [current_design]

Golden镜像设置

set_property BITSTREAM.CONFIG.NEXT_CONFIG_ADDR 0x00F50000 [current_design]

set_property BITSTREAM.CONFIG.NEXT_CONFIG_REBOOT ENABLE [current_design]

Update镜像设置

set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

其中set_property BITSTREAM.CONFIG.TIMER_CFG这一项设置是使能FPGA在上电配置过程中的看门狗计时器,具体的数值没有找到相关参考文档,还希望能够私信探讨。

参考文档:

Xapp1257、pg153、ug908、ug570.

目前方案已经经过平台验证,刚开始写博文,如有问题欢迎私信指正。