MOS管结构以及工作原理

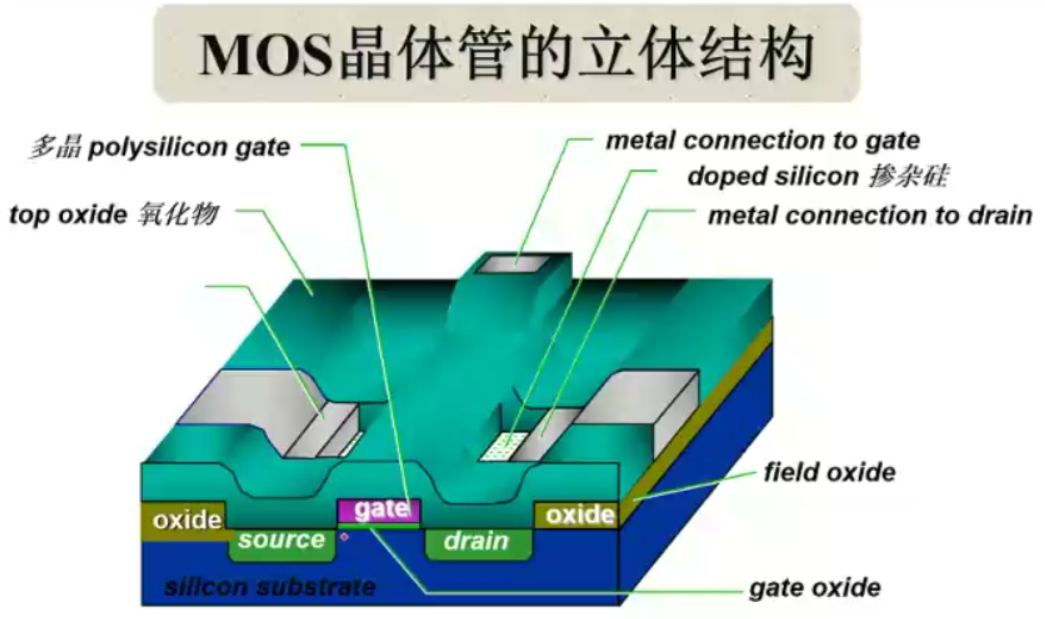

MOS管结构图

MOS管是金属(metal)—氧化物(oxide)—半导体(semiconductor)场效应晶体管,或者称是金属—绝缘体(insulator)—半导体。MOS管的source和drain是可以对调的,他们都是在P型backgate中形成的N型区。在多数情况下,这个两个区是一样的,即使两端对调也不会影响器件的性能。这样的器件被认为是对称的。

MOS FET工作原理

MOS 场效应管也被称为MOS FET, 既Metal Oxide Semiconductor Field Effect Transistor(金属氧化物半导体场效应管)的缩写。它一般有耗尽型和增强型两种。这里以增强型MOS为例分析。

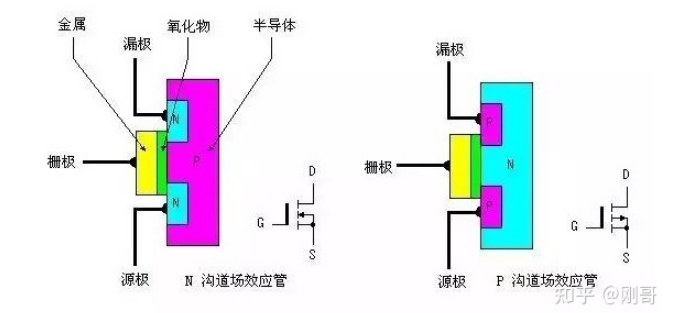

场效应管是由源极,漏极,栅极组成,由于衬底的掺杂不同可分为N沟道和P沟道场效应管。(沟道:顾名思义就是在衬底上挖两个可填充沟道,填充N型或者P型半导体)

将漏极接到电源正极,源极接到电源负极。

对于场效应管,在栅极没有电压时,源极和漏极之间相当于两个背靠背的二极管,不会有电流流过,此时场效应管处与截止状态。

如上面右图所示,当在栅极加上电压时,当电压小于一个阈值VGS(th)时,栅极和衬底P之间会由于电场的作用,将P型半导体中的空穴推开,此时N型半导体的源极和漏极的负电子被吸引出来而涌向栅极,但由于氧化膜的阻挡,使得电子聚集在两个N沟道之间的P型半导体中。

随着栅极电压的增大,栅极附近的电子浓度会增加。当超过一个阈值VGS(th)时,在源极和漏极之间的N型半导体会形成一个电子沟道。同时此时由于漏极加有正电压,就可以形成漏极到源极的电流,MOS管导通。

我们也可以想像为两个N型半导体之间为一条沟,栅极电压的建立相当于为它们之间搭了一座桥梁,该桥的大小由栅压的大小决定。这也是为什么说MOS管是电压控制性晶体管的原因。

我们可以将MOS管想象成一个阀门,栅极就像开关可以控制水流是否可以通过。

CMOS FET工作原理

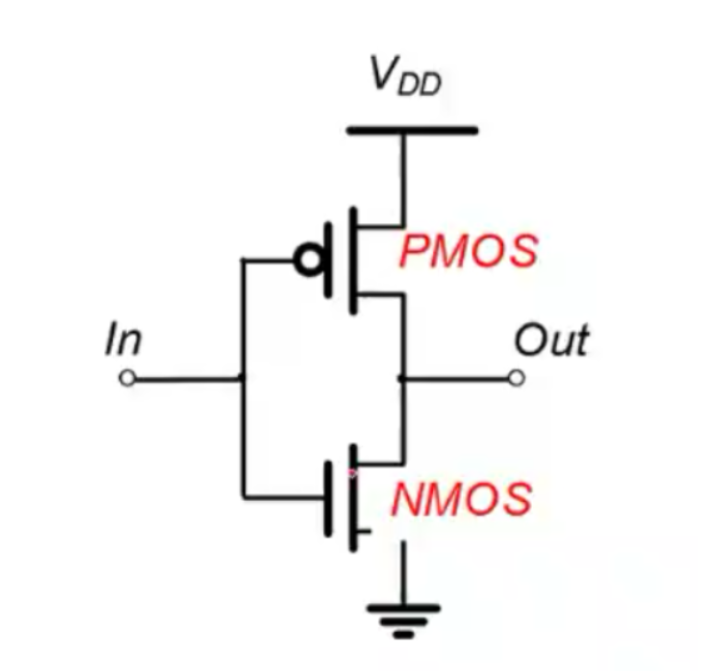

CMOS管的英文全称叫做:Complementary Mental Oxide Semiconductor Field Effect Transmetor(互补型金属氧化物半导体场效应管)由N沟道-MOS-场效应管和P沟道-MOS-场效应管构成,具体电路图如下:

- 当输入端为低电平时,P沟道MOS场效应管导通,输出端与电源正极接通,输出高电平。

- 当输入端为高电平时,N沟道MOS场效应管导通,输出端与电源地接通,输出低电平。

通过上述的逻辑特性,因此,CMOS管也可以称为反相器。

在电路里面将输出端通过电压的高点判断为1和0,就实现了通过一个逻辑控制。然后将所有的逻辑通过不同的逻辑规则组合就可以实现不同的逻辑功能。

MOS管导通原理

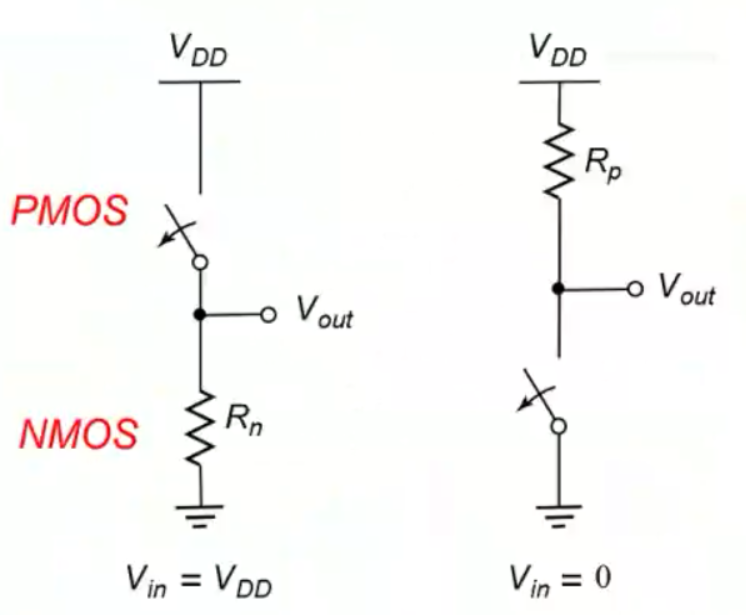

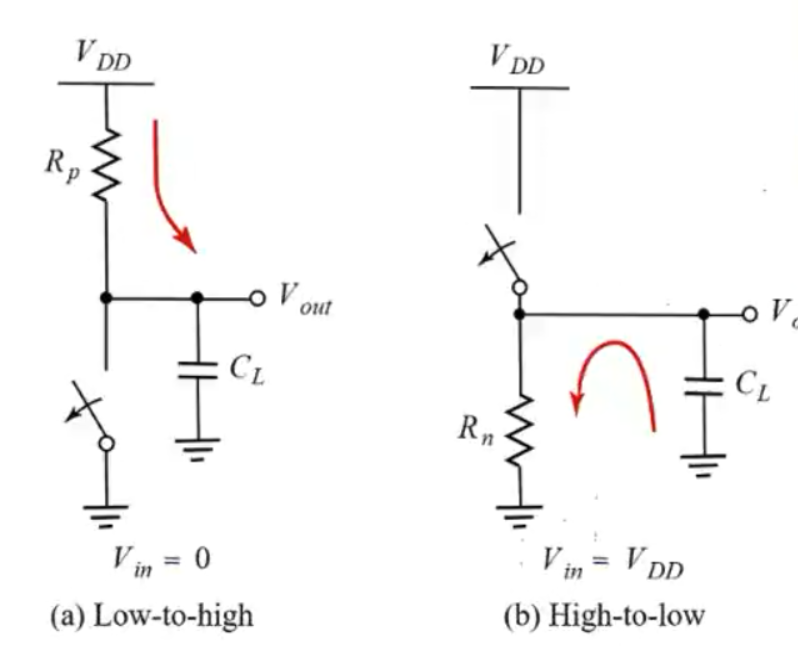

根据上述特性,可以将PMOS管和NMOS管导通时想象成开关,当导通时开关闭合等效成一个电阻,截止时开关断开。

电平变化时,可以等效理解成电容充放电的过程。

输入由高电平变低电平时,P管导通,Vout电平输出由低变高,相当于对CL充电,电压逐渐升高,并稳定在VDD附近。

输入由高电平变低电平时,N管导通,Vout电平输出由高变低,相当于对CL放电,电压逐渐减小,并稳定在GND附近。

逻辑综合和物理版图

逻辑综合技术:HDL转换为Netlist (门级网标)。

物理版图设计:Netlist转化为GDSII(可用于生成的版图文件)。

反相器

反相器的结构图如下所示,是由N沟道-MOS-场效应管和P沟道-MOS-场效应管构成。

反相器版图

下图是反相器的物理版图,主要由PMOS管,NMOS管,衬底组成。NMOS的衬底接低电平,P型半导体,PMOS的衬底接高电平,N型半导体。

为了正常工作,CMOS芯片必须保证工作是衬底和管子形成的PN结反偏,因此P管需要接电源VDD, N管接低GND。

对于版图上某一列的方框,一般都是接触孔,是为了将源极和漏极通过金属引线连接到上一层甚至更高层进行互联的孔,所以只有在PMOS管和NMOS管的源极和漏极才有可能会打孔,而在有源区,一般是看不到多晶硅形成的栅极打孔的。

在识别管子的时候要去找MOS管的栅,而P管和N管一般都是共用同一个栅,所以就看竖着穿过P区和N区的长条状结构就是栅。有几个这样的长条就是有几个输入。如下图所示,图中褐色的贯穿PNMOS的长条结构即为栅极。

识别源极和漏极的方法如下,对于P管和N管源极是不同的。但很容易区分接电源和接地的一端。一般而言,对于PMOS,接电源的一端是源极;而对于NMOS管,接地的一端是源极。对于一个MOS管而言,一侧是源极,那么另一侧就是漏极。

PMOS管比NMOS管宽不同原因

因为PMOS是空穴导电,NMOS管是电少子导电。电子的迁移率约是空穴的2倍。

反相器VTC曲线

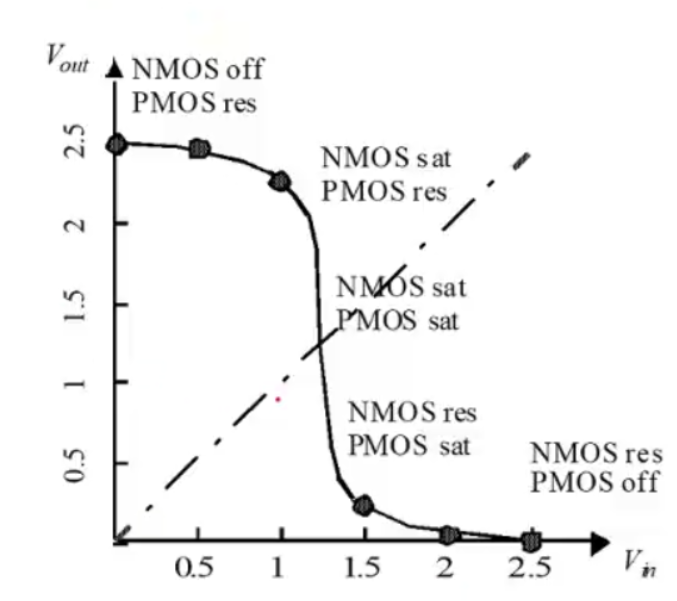

结合MOS管的导通原理,可以知道,PMOS和NMOS管在导通时,都”等效”有电容充放电的时间,下图反映了在不同电压值时的MOS管的导通情况。

从图上可知,当输入电压大概小于0.5V时,P管导通,N管截止,输出电压为高电平。当输入电压大概大于1.5V时,N管导通,P管截止,输出电压为低电平。

当输入电压在0.5-1.5V之间时,P管和N管会处于导通和截止的临界状态,可以当做两个管子都是微导通状态。这个阶段在电路设计时是不希望看到的,所以理论上来说该部分的斜率(绝对值)越大越好。

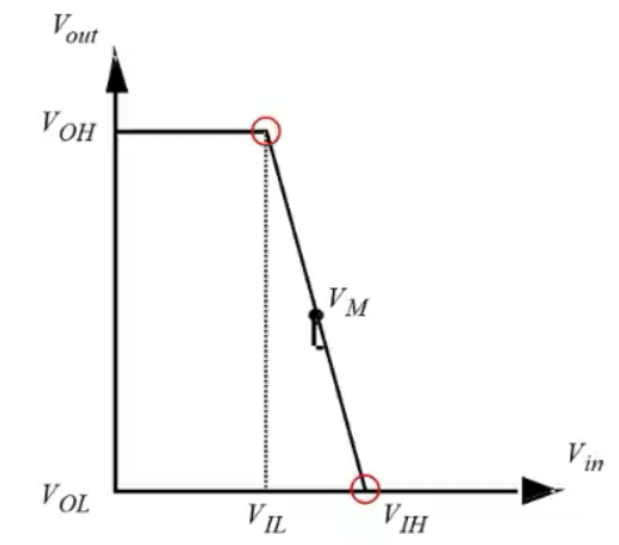

VTC曲线的近似模型如下图所示:

VTC的形状基本上与高于阈值的操作相同。VTC陡峭部分的斜率取决于反向器的亚阈值斜率。

其中涉及到的的四个重要参数:

VIH:输入电压由高到低变化时,输出电压开始上升且传输特性曲线斜率为-1的点,仍能维持输出为逻辑 “0” 的最小输入电压。

VIL:输入电压由低到高变化时,输出电压开始下降且传输特性曲线斜率为-1的点,仍能维持输出为逻辑 “1” 的最大输入电压。

VOH:定义为最小合格高电平,维持输出为逻辑“1”的最小输出电压。

VOL:定义为最大合格低电平,维持输出为逻辑“0”的最大输出电压。

CMOS集成电路内部规定Vol = 0V,Voh = Vdd。

高低电平的噪声容限

输入为高电平的噪声容限:VNH=VOH-VIH

输入为低电平的噪声容限:VNH=VIL-VOL

反相器的亚稳态

当反相器输入电压(Vil+Vih)/2接近于0.5Vdd,CMOS反相器的阈值电压也接近于0.5Vdd,这样输出不确定会是高电平还是低电平,输出呈亚稳态。

反相器的动态特性

Transition Time(转换时间):

- 上升时间tr:从10%Vdd上升到90%Vdd的时间。

- 下降时间tf:从90%Vdd下降到10%dd的时间。

- 上升时间和下降时间统称为Transition Time,也有定义为20%到80%。

Propagation Delay(传播延时):

在输入信号变化到 50%Vdd到输出信号变化到50%Vdd之间的时间。

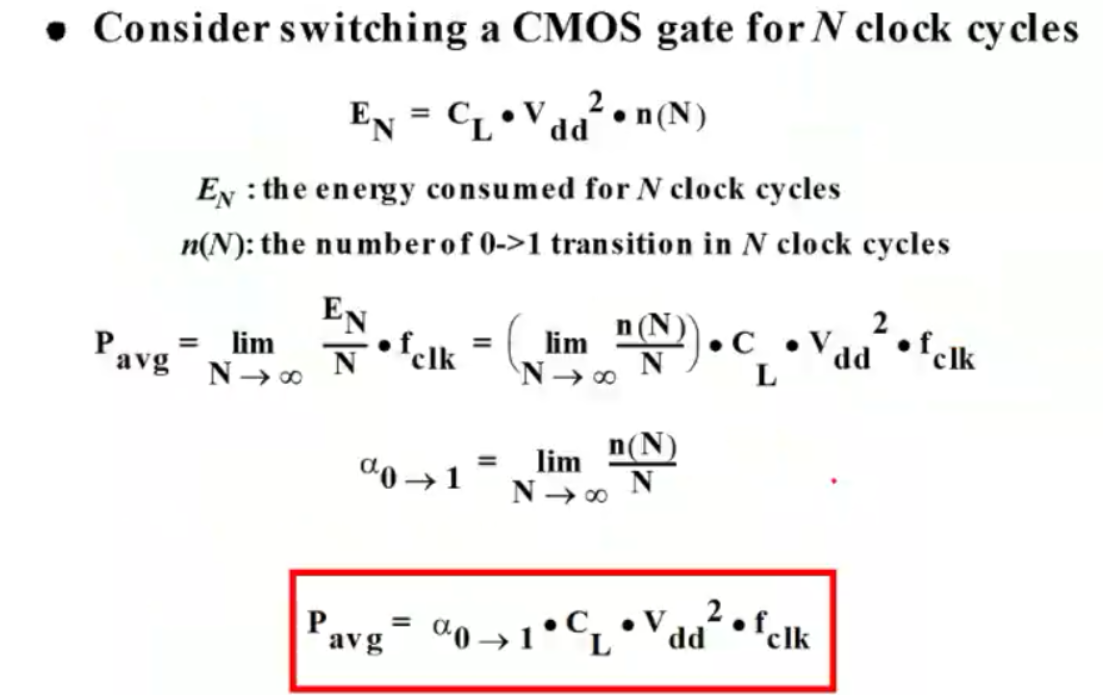

动态功耗(Dynamic Power Consumption)

反相器从一种稳定状态突然变到另一种稳定状态的过程中,将产生附加的功耗,即动态功耗。CMOS电路主要有动态功耗和静态功耗组成,动态功耗又分为开关功耗、短路功耗(内部功耗)两部分。

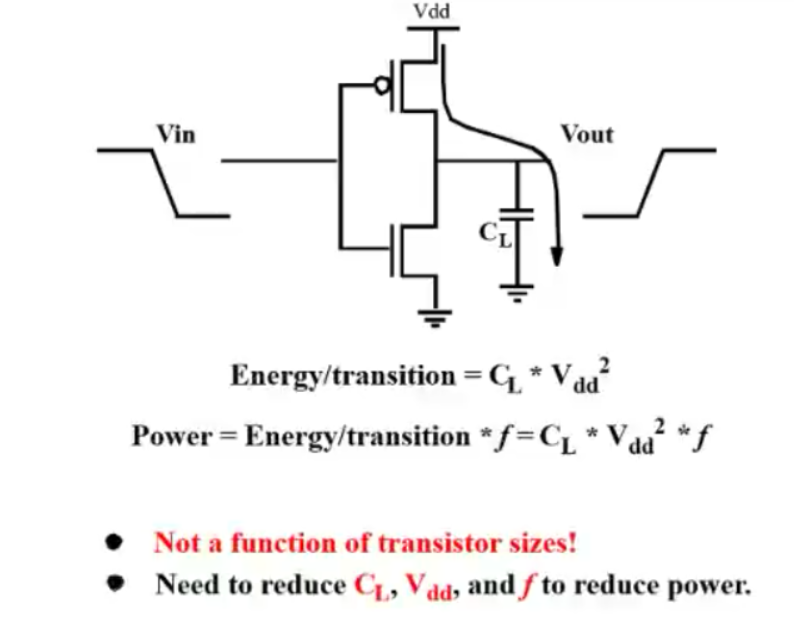

动态功耗包括:负载电容充放电所消耗的功率Pc和PMOS、NMOS同时导通所消耗的瞬时导通功耗PT。在工作频率较高的情况下,CMOS反相器的动态功耗要比静态功耗大得多,静态功耗可以忽略不计。

总功耗为P=PT+Pc。

负载电容充放电功耗Pc(开关功耗)

开关功是指电路在开关过程中对输出节点的负载电容充放电所消耗的功耗。

对于CMOS电路来说,提高工作电压可提高性能但同时功耗增加,温度升高时功耗增加。

从上述的负载电容充放电功耗的公式中可知,Pc的功耗变化与负载电容、工作电压、以及工作频率有关。

考虑到实际电路不一定在相应的工作频率下的每个周期都进行变化反转,因此可以将上述式子转换,求出平均的动态功耗。相比上式平均动态功耗的式子多乘了一个翻转率。(在N个周期中反转了n次,即翻转率为n/N)

减小开关功耗的方法

从上述公式以及相关推导过程可看出,若想实现电路的低功耗设计,应该从以下几个方面入手:

- 减小供电电压。

- 减小物理电容(N、PMOS管沟道缩小,布局布线进行调整优化)。

- 减小无必要的反转。

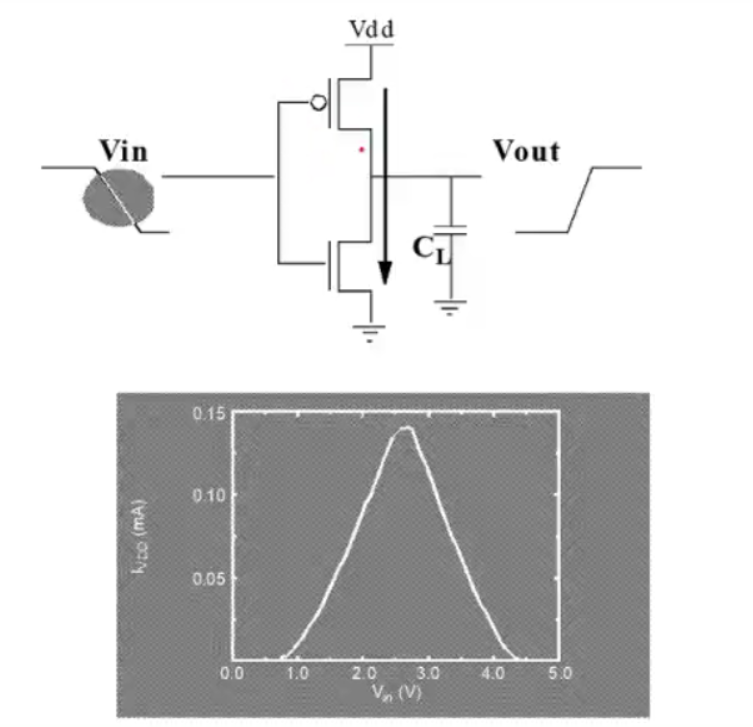

导通功耗PT(短路功耗)

短路功耗是指由于输入电压波形并不是理想的阶跃输入信号,有一定的上升时间和下降时间,在输入波形上升下降的过程中,在某个电压输入范围内,NMOS和PMOS管都导通,开关导通瞬间的电源和地之间形成短路,从而造成的功耗。

P T = V D D I T A V P_T=V_{DD}I_{TAV} PT=VDDITAV

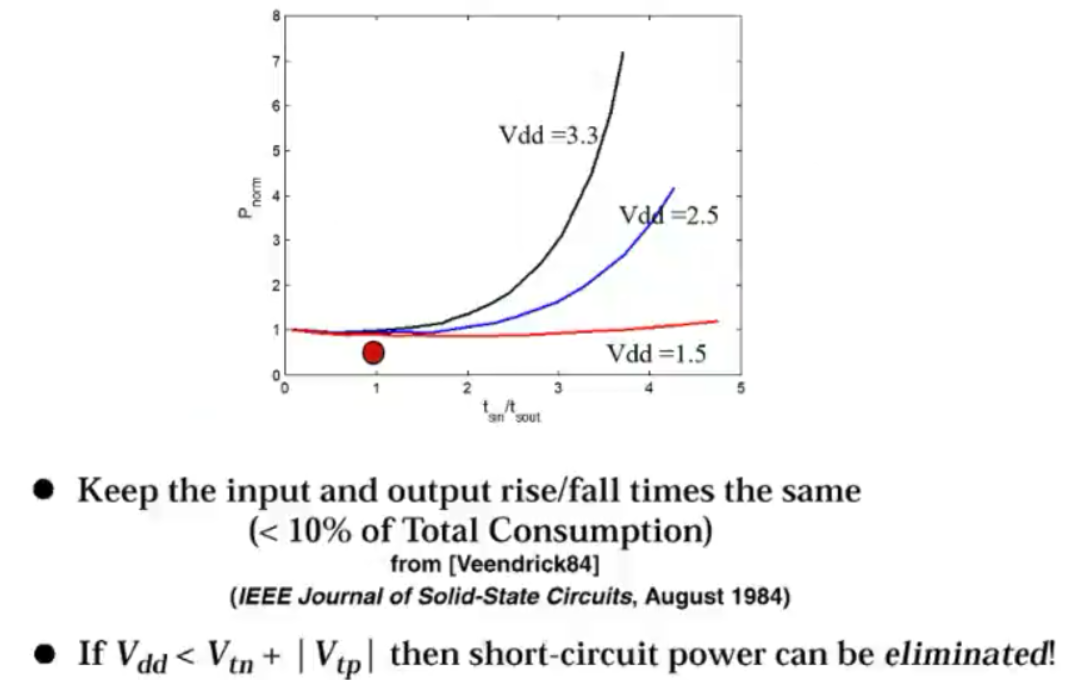

减小短路功耗方法

下图是在保持输入输出的上升下降时间相同做的功耗对比,从实验结果可看出,当其余条件一致时,工作电压越低,电路功耗越小。

因此,减小短路功耗的方法可以通过减小Vdd,也即工作电压实现。

静态功耗

在CMOS电路中,静态功耗主要是漏电流引起的功耗。对于常规cmos电路,在稳态时不存在直流导通电流,理想情况下静态功耗为0,但是由于泄露电流的存在,使得cmos电路的静态功耗并不为0。CMOS泄露电流主要包括:反偏PN结电流和MOS管的亚阈值电流。

P p e a k = V D D ∗ I p e a k P_{peak}\ = \ V_{DD}\ *\ I_{peak} Ppeak = VDD ∗ Ipeak

Ipeak为泄露电流,减少静态功耗的方法就是减小VDD和Ipeak。

其他组合逻辑CMOS电路

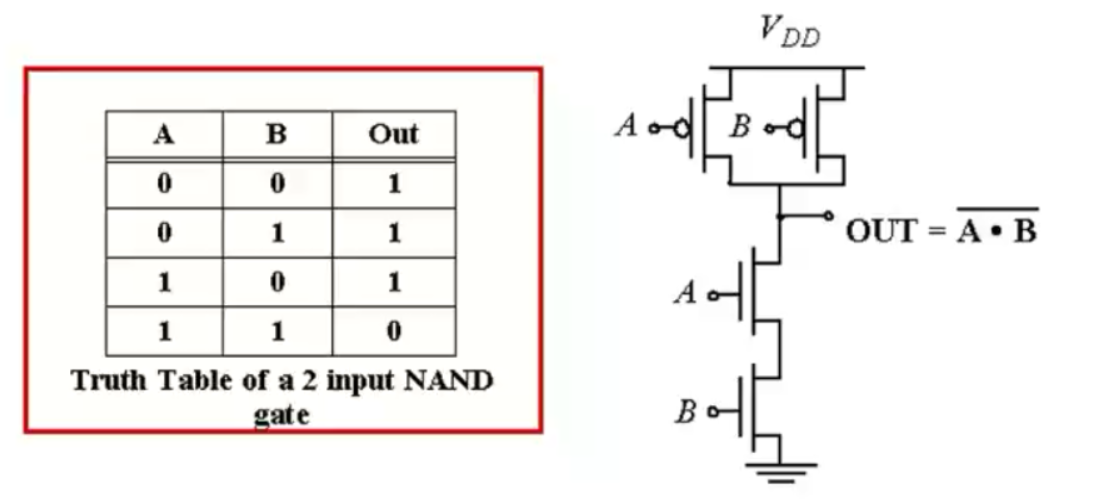

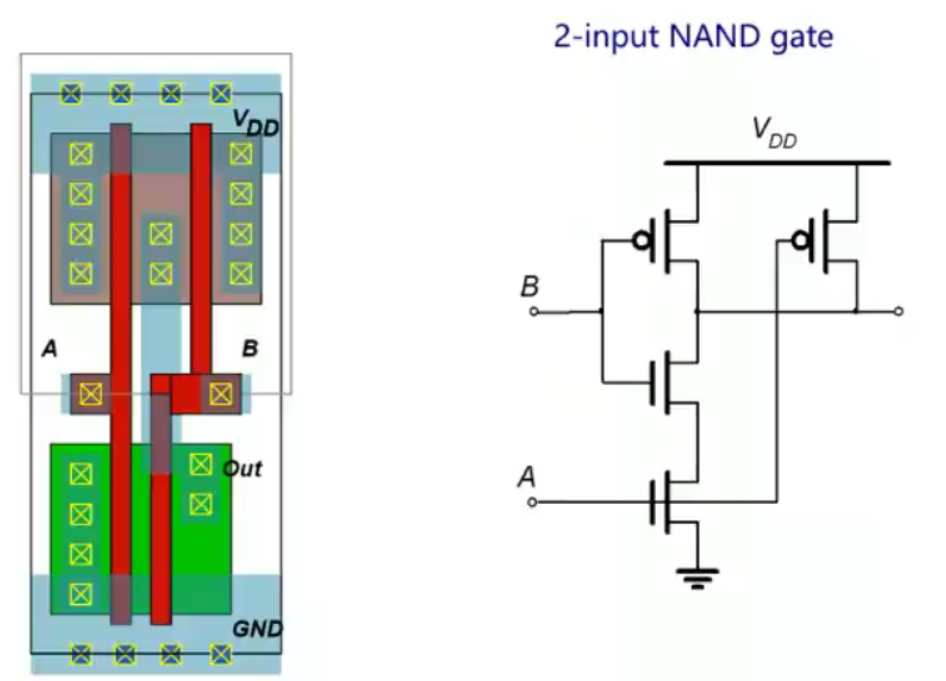

与非门

实现思路:观察逻辑真值表,只有在AB同时为1是输出结果才为0,所以也就只有AB两个CMOS管同时导通N管才能实现该逻辑功能,并且根据CMOS的对称结构,即可确定与非门的CMOS电路图。

版图结构如下:

或非门

实现原理类似与非门。

reference

- 结构原理图解

- 一文讲明白MOS管工作原理

- 数字电路基础知识——反相器的相关知识(噪声容限、VTC、转换时间、速度的影响因素、传播延时等)