xilinx高速收发器学习记录

说明:本文摘自 V3学院 尤老师的培训班笔记,仅用于个人学习,不用于任何商业用途。

满足个人在公交车上或者其他需要不得不等待的时间段内学习的需要。

-

高速收发器的QUAD,如果级联以共享时钟,往上和往下不能超过2级。也就是说,共享时钟的时候,最多是5个QUAD使用一个gtrefclk。

为什么只能驱动5个,因为时钟的驱动能力有限。

每个quad是4个收发对,5个quad就是20个收发对。GTP的带宽为5G.

GT0-GT3可以使用同一个gtrefclk,也可以自定义选择使用不同的gtrefclk。(一个QUAD有两个gtrefclk参考时钟)

======================

-

Gtrefclk进来必须要进一个IBUFDS_GTE.即一个差分转单端的buf

HROW是全局时钟放在水平方向还是垂直方向的节点,ODIV2是输出给用户逻辑用的,可以分选二分频或者不分频或者直接拉低降低功耗。

======================

-

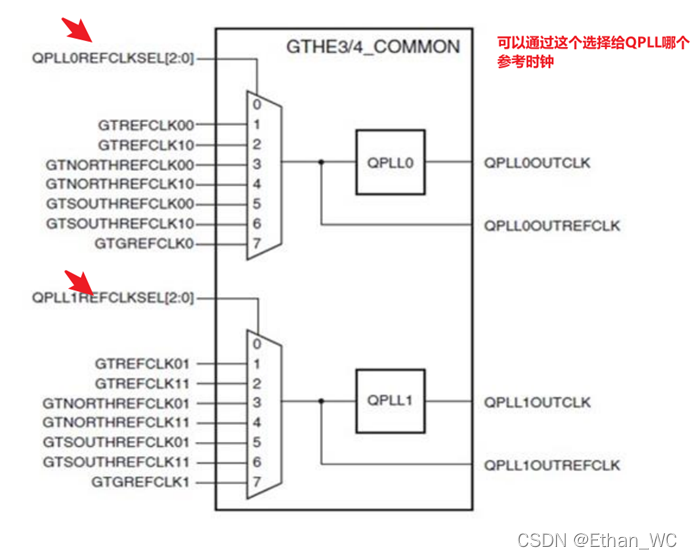

GTE输出的时钟可以接GT-COMMON(共享时钟资源)。GT-COMMON是在Reference Clock Distribution中。

可以通过在common原语上选择给QPLL哪个时钟,实现四个收发对用不同的参考时钟。

====================== -

高速收发器的结构

1)TX

FPGA Parallel 的接口就是逻辑的并行数据,比如AXI的接口。

用户的并行数据实际是64bit, PCS中会插入两bit数据让他变成66bit.(做64b/66b编码),但是PCS parallel clock 和PMA parallel clock之间的交互,它并不会一次将66位取走,比如他一次取走32位,两次才会取走64位。多余的两位就取不走了,怎么办?

每一次多两位,等到16个周期之后,就满32位了,此时TX Sync Gearbox缓存了32位了,就会告诉用户端,让他停一拍,此时TX Sync Gearbox就把积累的32位传递给PMA parallel clock这边了。TX-PCS中有bist数据(pattern generator, pcie beacon, sata oob),可以发送出去,再接收端接受,从而测试物理连接是否正常。

TX-PMA中有预加重和后加重,且PMA都是串行数据。

TX Serial Clock 是串行时钟,是端口串行速率的一半,原因是上升沿和下降沿都发送数据。

====

2)Rx

Rx-PMA中有CDR(时钟恢复模块),依赖refclk,从数据中将时钟恢复出来。

Rx-PCS中有checke模块,检查TX发过来的bist数据是否正确(如果有),验证物理层是否工作正确。

====

为了便于理解,PMA的功能可以简单描述为:

1)串并转换(图中的SIPO和PISO);

2)模拟部分;

由此可以反推出来,PCS中的功能,都是并行的数字电路处理。

理论上说GTX的最小必要单元就是PMA,其主要原因就是核心的模拟部分。而PCS理论上可以全部由FPGA普通逻辑来实现。当然作为硬核提供的PCS功能更多、性能更好、使用更方便。

====================== -

高速收发器的速度

GTP < GPX < GTH < GTZ < GTY < GTM

不同芯片上使用的高速收发器也不同,而且同样是GTX,不同系列芯片上的速率也可能不同。比如7系列的FPGA,GTP最高可以达到6.6Gb/s,GTX最高12.5Gb/s,GTH最高13.1Gb/s,GTZ最高28.05Gb/s

可参考:GTX/GTH/GTY/GTP/GTZ/GTM有什么区别? - 知乎 (zhihu.com)

======================