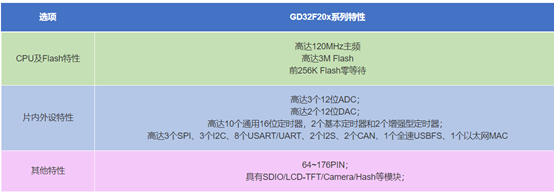

cortex-m3和cortex-m4处理器的一般信息

处理器类型

ARM Cortex-M为32位RISC处理器,具有以下特征:

1.32位寄存器

2.32位内部数据通路

3.32位总线接口

当然,除了32位数据,Cortex-M处理器(以及其他任何ARM处理器)还可以高效地处理8位和16位数据。Cortex-M3/M4处理器还支持涉及64位数据的多种运算。

Cortex-M3/M4处理器都具有三级流水线(取指、译码、执行),它们都基于哈佛总线架构,取指令和数据访问可以同时执行。

ARM Cortex-M处理器的存储器系统使用32位寻址,地址空间最大位4GB。存储器映射是一致的,这就意味着尽管总线接口多个,4GB存储空间却只有一个。存储器空间包括程序代码、数据、外设以及处理器内的调试支持部件。许多嵌入式系统需要的存储器不超过1MB,32位的寻址能力可以确保将来升级和拓展的可能

与其他任何ARM处理器相同,Cortex-M处理器基于一种加载-存储架构。若处理的是存储器中的数据,就需要将其从存储器加载到寄存器组中的寄存器里。在处理器处理完成后,若有必要,还要写回存储器。

处理器架构

对于ARM处理器,架构一般指两个方面:

架构。指令集架构(ISA)、编程模型以及调试方法

微架构。接口信号、指令执行时序以及流水线阶段等实现相关的细节,微架构为处理器设计相关的。

从理论上来说。在开发Cortex-M产品的软件时,开发人员无须了解微架构的任何信息。不过,在有些情况下,知道一些微架构的细节可能会有帮助,尤其是在优化软件或C编译器以获得最佳性能时。

指令集

Cortex-M处理器使用的指令集名为Thumb(其中包括16位Thumb指令和更新的32位Thumb指令),Cortex-M3/M4处理器用到了Thumb-2技术,它允许16位和32位指令混合使用,以获取更加的代码密度和效率。

ARM7TDMI等经典的ARM处理器具有两种操作状态:32位的ARM状态和16位的Thumb状态。在ARM状态,内核能够以很高的性能执行所有支持的指令;而对于Thumb状态,指令是16位的,这样可以获得更好的代码密度,不过Thumb指令不具有ARM指令的所有功能,要完成特定操作,需要更多的指令。

要同时得到两者的优势,许多经典ARM处理器的应用程序混合使用了ARM和Thumb代码。不过并不理想,它会带来状态切换间的开销,两种状态的分离还增加了软件变异过程的复杂度。

随着Thumb-2技术的引入,Thumb指令被扩展为16位和32位两种解码方式。现在,无须再两个不同状态间切换就可以满足所有需求。事实上,Cortex-M处理器根本不支持32位的ARM指令,甚至中断处理都可以完全在Thumb状态中实现。利用Thumb-2技术与经典的ARM处理器相比,Cortex-M处理器具有诸多优势。例如:

无状态切换开销,节省执行时间和指令空间

无须指定源文件中的ARM状态或Thumb状态,开发软件也相对容易

在获得最佳的代码密度和效率的同时,还能很容易达到高性能

利用Thumb-2技术,与ARM7TDMI等经典处理器相比,Thumb指令集已经得到了很大的拓展。

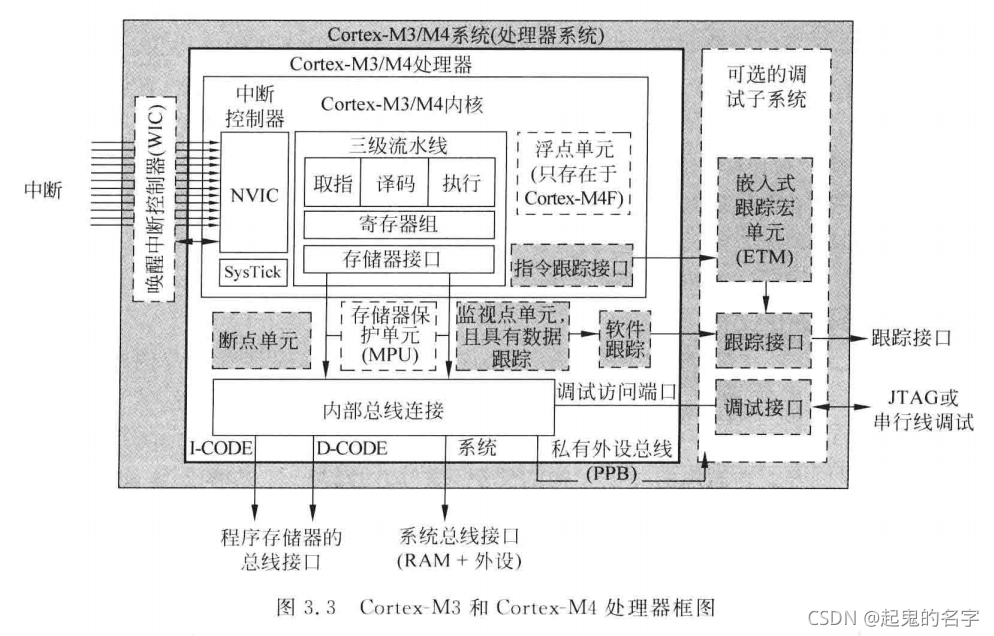

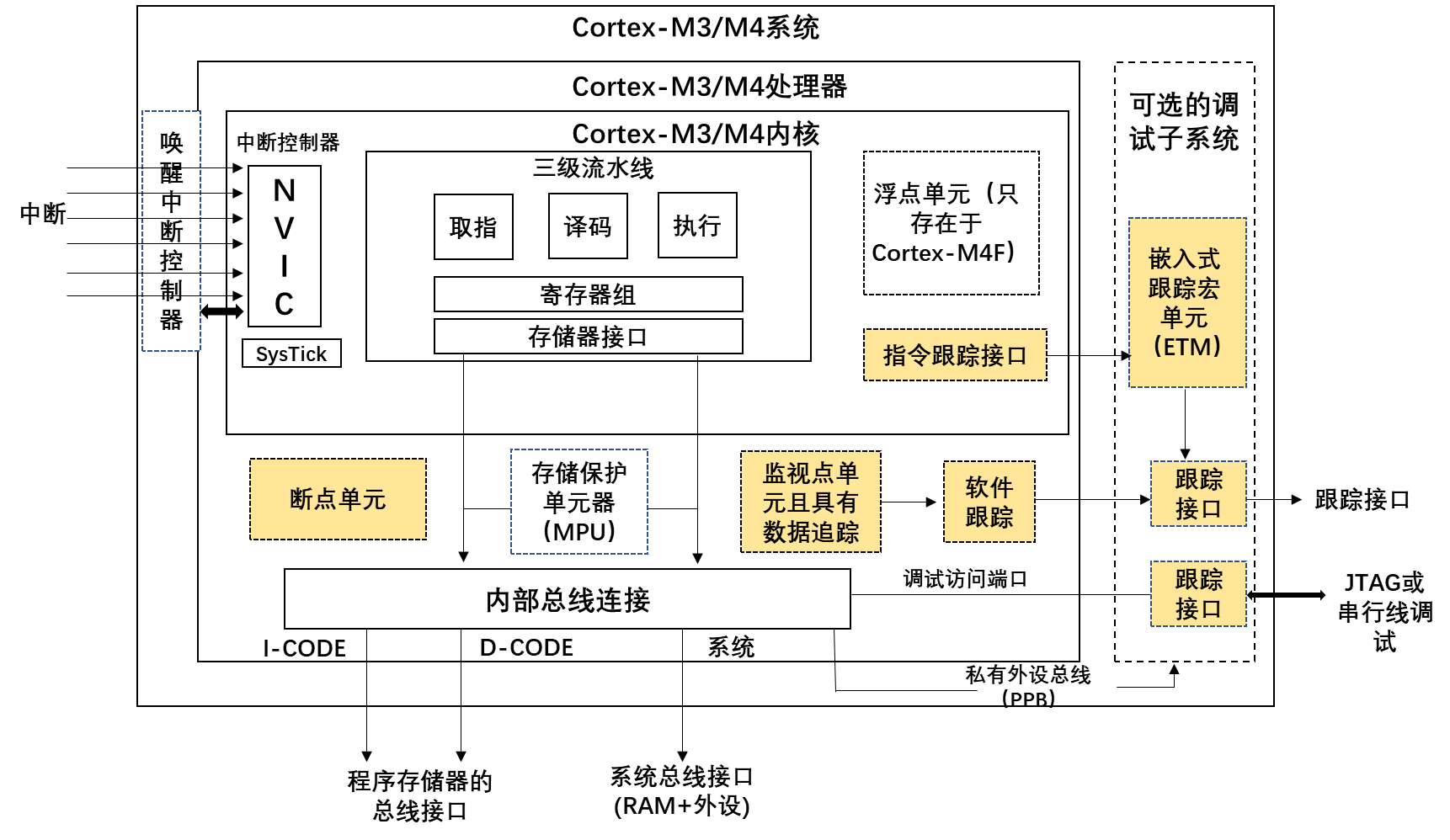

模块框图

图 Cortex-M3/M4处理器框图

存储器系统

Cortex-M3/M4处理器本身并不包含存储器,但他们具有通用的片上总线接口,因此,微控制器供应商可以将他们自己的存储器系统添加到系统中。一般来说,微控制器供应商需要将下面的部件添加到存储器系统中:

程序存储器,一般是Flash。

数据存储器,一般是SRAM。

外设。

Cortex-M处理器的总线接口为32位宽,其基于高级微控制器总线架构(AMBA)标准。Cortex-M3/M4处理器主要使用的总线接口协议为AHB Lite,它用于程序存储器和系统总线接口。AHB Lite协议为流水线结构的总线协议,可以在低硬件成本下实现高运行频率。

中断和异常支持

Cortex-M3/M4处理器中存在一个名为NVIC的中断控制器,它是可编程的且其寄存器经过了存储器映射。NVIC的地址固定,而且NVIC的编程模型对于所有的Cortex-M处理器都是一致的。

除了外设和其他外部输入的中断外i,NVIC还支持多个系统异常,其中,包括不可屏蔽中断(NMI)和处理器内部的其他异常源。