VGA显示器是如何显示图像的?我们的FPGA和MCU要怎样配置才能让VGA显示器正确显示?经常有朋友这样问,网上相关的介绍也不少,我这里从FPGA或MCU的LCD控制器的角度来讨论这个问题。 我们先来看看显示器显示一个图像需要哪些信号(此图来自LCD显示模组的规格书)

从图可以看出,LCD显示图像需要Hsync,Vsync, D[n:0],CLK,DE,而且这些信号要满足上述时序关系,

我们再来看VGA显示器的输入信号(此图来自VESA Monitor Timing Specifications )

从上图可以看出,这里只有3个信号Hsync,Vsync,Video 和LCD需要的信号比较,Hsync,Vsync,是共同都有的,Video和D[n:0]其实是同一个信号,就是视频信号,显示器要显示的内容,LCD是数字输入的,所以用Data[n:0]来描述了,简写D[n:0],n表示每个像素的灰度,灰度 = 2的n次方,通常取值是8或6;但是还少了DE和CLK信号。

这里我们来描述VGA显示是如何得到DE和CLK信号的,这也是本文要描述的重点。Hsync和Vsyn是我们要分析的根本,一个同步信号通常有这几个参数,频率,极性,同步头的宽度。

频率:这个不用说了;

极性:有正极性和负极性,信号中高电平时间长,低电平时间短就是负极性,反之就是正极性,前图的LCD信号图中的Hsync就是负极性,VGA显示器输入信号图中的Hsync是正极性;

同步头宽度:有些也叫同步时间,就是描述同步信号中较短的电平的时间,通常单位是CLK,可以用时间单位描述;

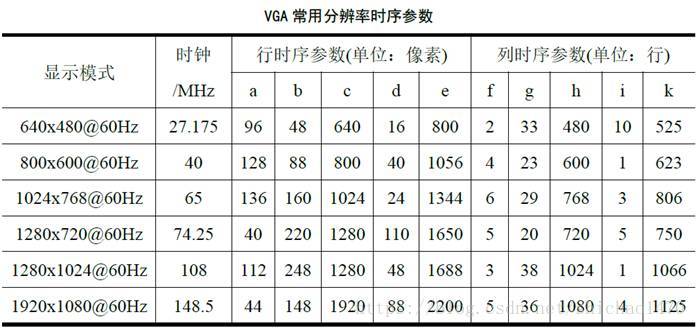

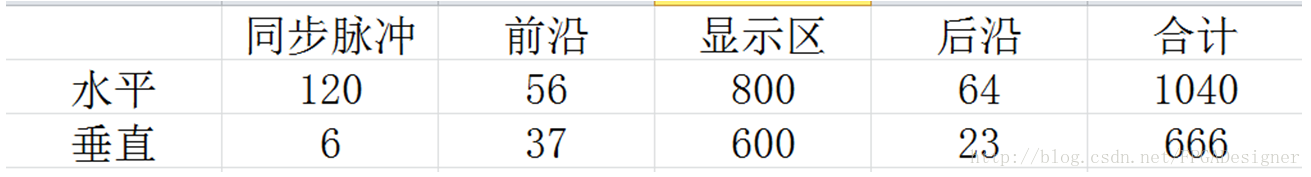

识别分辨率是得到CLK和DE的关键,VESA标准中每个不同的分辨率(包含刷新频率)Hsync,Vsync的频率和极性是不同的,VGA显示器就是根据这个来确定输入图像的分辨率的。一旦分辨率确定,一切都定了,你就可以查VESA标准得知VGA输入信号图中的全部参数。LCD中的DE就是DataEnable,对应VGA图中Active Video,DE总是高电平有效,也有些LCD描述的是Blank,Blank就是DE的取反。接下来就是CLK了,CLK = Hsync * Htotal。所有的VGA显示器内部都有一个PLL,就是起这个作用的,应为信号源来自Hsync,所以Hsync必须稳定。这里出现了Htotal,就VESA中的 Hor Total Time。下面贴出一个1024*768@60Hz的 全部信息

VGA显示器的原里说完了,我们来看看LCD控制器有哪些信号(下图来自STM32规格书)

是不是看到VGA信号的LCD控制器的关系了;

下图是verilog配置的VGA控制器,和MCU的LCD控制器是很相似的。

好了,所有的描述完毕,不知道我描述清楚了没有,也可以加入QQ群来讨论这些问题 显示之窗 450660

————————————————

版权声明:本文为CSDN博主「qg_zhu」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qg_zhu/article/details/45867541