功能

1、处理指令:完成取指令、分析指令和执行指令的操作,即程序的顺序控制

2、执行操作:条指令的功能往往由若干操作信号的组合来实现。CPU管理并产生由内存 取出的每条指令的操作信号,把各种操作信号送往相应的部件,从而控制这些部件按指 令的要求进行动作。

3、控制时间:对各种操作加以时间上的控制。时间控制要为每条指令按时间顺序提供应有 的控制信号。

4、处理数据:对数据进行算术和逻辑运算。

5、中断处理:对计算机运行过程中出现的异常情况和特殊请求进行处理。

工作过程

- 取指令

- 指令译码

- 指令执行

- 后续工作

基本结构

寄存器组

通用寄存器:可由CPU通过程序访问,在指令中可为这组寄存器分配各自的编号,可编程访问指定编号的寄存器。

暂存器:用来暂存产生的中间过程数据,以避免破坏通用寄存器的内容。

指令寄存器IR:用来存放正在执行的指令,它的输出包括操作码信息、地址信息等,是产生微命令的主要逻辑依据。

程序计数器:指示指令在存储器中的存放位置。

程序状态寄存器:记录现行程序的运行状态和指示程序的工作方式

地址寄存器:CPU访问主存时,先要找到存储单元,因此设置地址寄存器来存放被访问单元的地址。从内存中读时,先将有效地址送入MAR。

数据缓冲寄存器:存放CPU与主存之间交换的数据。无论是从主存读出的数据,还是写入主存的数据,都要经过MBR。

运算器

完成数据的输入,对输入的数据进行加工,输出运算结果。

由输入逻辑;ALU;输出逻辑构成。

控制器

1)程序计数器。用于指出下一条指令在主存中的存放地址。CPU根据PC的内容去主存中取指令。

2) 指令寄存器。用于保存当前正在执行的那条指令。

3) 指令译码器。仅对操作码字段进行译码,向控制器提供特定的操作信号。

4) 时序产生器。用于产生各种时序信号,它们都由统一时钟(CLOCK)分频得到。

5) 操作控制器。根据IR的内容(指令)、PSW的内容(状态信息)及时序信号,产生控制整个计算机系统所需的各种控制信号,其结构有组合逻辑型和存储逻辑型两种。

CPU内部的数据通路结构

- 单组内总线、分立寄存器结构

特点:可同时向ALU提供两个操作数;采用单向内总线 - 单组内总线、集成寄存器结构

特点:单口RAM不能同时向ALU提供两个操作数;用锁存器(暂存器)暂存操作数;采用双向内总线。 - 多组内总线结构

特点:用双口RAM(两地址端、两数据端)作通用寄存器组,可同时提供数据;用多路选择器作输入逻辑,不需暂存操作数;ALU增加乘、除功能,用乘商寄存器存放乘数、乘积或商。

CUP设计

拟定指令系统:格式、寻址方式、指令类型设置

确定总体结构:寄存器、ALU、数据通路设置

安排时序:画流程图

拟定指令流程和微命令序列:操作时间表

形成逻辑控制:组合逻辑还是微程序

控制器

组合逻辑控制器

基本思想

综合化简产生微命令的条件,形成逻辑式,用组合逻辑电路实现;执行指令时,由组合逻辑电路在相应时间发

出所需微命令,控制有关操作。

控制器组成

微命令发生器:产生全机所需的各种微命令

指令计数器PC:指示指令在M中的位置。

指令寄存器IR:存放现行指令。

状态寄存器PSW:指示程序运行方式,反映程序运行结果。

工作过程

- 取指令

- 取数:按寻址方式,或从寄存器取数,或从存储器取数。

- 执行:按操作码对数据进行运算处理。

优缺点及应用

产生微命令的速度较快。

设计不规整,设计效率较低;

不易修改、扩展指令系统功能。

用于高速计算机,或小规模计算机。

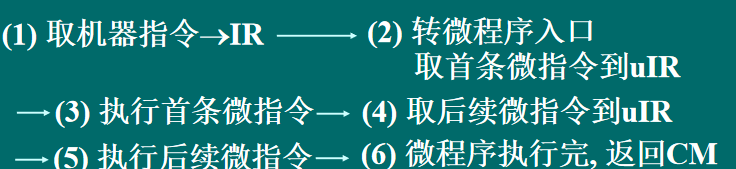

微程序控制器原理

基本思想

- 若干微命令编制成一条微指令,控制实现一步操作;

- 若干微指令组成一段微程序,解释执行一条机器指令;

- 微程序事先存放在控制存储器中,执行机器指令时再取出。

控制器组成

控制存储器CM:存放微程序

微指令寄存器uIR:存放现行微指令。

微地址形成电路:提供两类微地址。

工作过程

优缺点及应用

设计规整,设计效率高;

易于修改、扩展指令系统功能;

结构规整、简洁,可靠性高,性价比高。

速度慢,执行效率不高。

用于速度要求不高、功能较复杂的机器中。

组合逻辑控制器的时序系统

依靠不同的时间标志,让CPU分步工作,通常采用工作周期、时钟周期和工作脉冲三级时序。

工作周期

- 取指周期FT:从M取出指令并译码,修改PC。

- 源周期ST:按寻址方式形成源地址,从M取出源操作数,暂存于C。

- 目的周期DT:按寻址方式形成目的地址,或从M取出目的操作数,暂存于D。

- 执行周期ET:按操作码完成相应操作(传送、运算、取转移地址送入PC、返回地址压栈保存);后续指令地址送入MAR。

- 中断周期IT:IT指CPU响应中断请求后,到执行中断服务程序前的时间。关中断、保存断点和PSW、转服务程序入口。

- DMA周期DMAT:DMAT指CPU响应DMA请求后,到完成一次数据传送的时间。DMA控制器接管总线权,控制数据直传。

时钟周期(节拍)

时钟周期的时间:1微妙,完成一步操作。

一次从M读出,并经数据通路传送的操作;或一次数据通路传送操作;或一次向M写入的操作,

时钟周期数:一个工作周期中的时钟数可变。

工作脉冲

每个时钟周期结束时设置一个脉冲。

试说明机器指令与微指令的关系

(1) 一条机器指令对应一段微程序,这段微程序是由若干条微指令序列组成的。因此,一条机器指令的功能是由若

干条微指令组成的序列来实现的。简言之,一条机器指令所完成 的操作划分成若干条微指令来完成,由微指令进行

解释和执行。

(2) 从指令与微指令、程序与微程序、地址与微地址的一一对应关系来看,前者与内存储器 有关,后者与控制存储

器有关。

(3) 每一个 CPU 周期对应一条微指令

微指令编码有哪三种方式,微指令格式有哪几种,微程序控制器有哪些特点?

微指令编码方式有直接表示法、编码表示法、混合表示法。微指令的格式大体分成两类:水平型微指令和垂直

型微指令。水平型微指令分为全水平型微指令、字段编码的水平型微指令、直接和编码相混合的微指令。微程序控

制器具有规整性、可维护性和灵活性的优点,可实现复杂指令的操作控制,使得在计算机中可以较方便地增加和修

改指令,甚至可以实现其他计算机的指令。

(1)直接表示法。微操作码中的每一位表示一种微操作,这种方法简单,但微指令字长较长,编码效率较低。

(2)编码表示法。将微操作码分段编码,将相容性微操作放在不同的段中,而将相斥性微操作放在同一段中。每段包

含若干位,用不同的码点表示不同的微操作。这种方法微指令字长较短,编码效率高,但执行速度较慢,且需要增

加译码器。

(3)混合表示法。结合前两种方法,将一些速度要求高,或者与其他微操作都相容的微操作用直接表示法表示,而将

其他微操作以编码表示法表示。

MMU

是 Memory Management Unit 的缩写,中文名是内存管理单元,它是中央处理器(CPU) 中用来管理虚拟存储器、物理存储器的控制线路,同时也负责虚拟地址映射为物理地址,以及提供硬件机制的内存访问授权。