1.SATA接口简介

2.SATA的电路仿真

1.SATA接口简介

SATA是Serial ATA的缩写,即串行ATA。这是一种完全不同于并行ATA的新型硬盘接口类型,因采用串行方式传输数据而得名。SATA总线使用嵌人式时钟信号,具备了更强的纠错能力,与以往相比其最大的区别在干能对传输指令(不仅仅是数据)进行检查,如果发现错误会自动矫正,这在很大程度上提高了数据传输的可靠性。串行接口还具有结构简单、支持热插拔的优点。

与并行ATA相比,SATA具有比较大的优势。首先,Serial ATA以连续串行的方式传送数据,可以在较少的位宽下使用较高的工作频率来提高数据传输的带宽。Serial ATA一次只会传送1位数据,这样能减少SATA接口的针脚数目,使连接电缆数目变少,效率也会更高。实际上,Serial ATA仅用4支针脚就能完成所有的工作,分别用于连接电缆、连接地线、发送数据和接收数据,同时这样的架构还能降低系统能耗和减小系统复杂性。其次,Serial ATA的起点高、发展潜力更大。SerialATA1.0定义的数据传输率可达150MB/s。这比目前最快的并行ATA(即ATA/133)所能达到(133MB/s)的最高数据传输率还高,而已经发布的SerialATA2.0的数据传输率已达到300MB/s,最终SerialATA3.0将实现600MB/s的最高数据传输率。

日趋复杂的PCB布局布线设计对保证高速信号(如SATA)的正常工作至关重要。由于第一代和第二代SATA的速度分别高达1.5Gbps和3.0Gbps,因此铜箔蚀刻线布局的微小改动都会对电路性能造成很大的影响。SATA信号的上升时间约为100ps,如此快的上升时间。再加上有限的电信号传输速度,所以即使很短的走线也必须当成传输线来对待,因为这些走线上有很大部分的上升(或下降)电压。高频效应处理不好,将会导致PCB无法工作或者工作起来时好时坏。为保证采用FR4 PCB的SATA设计正常工作,必须遵守下面列出的FR4 PCB 布局布线规则。这些规则可分为两大类:设计使用差分信号和避免阻抗不匹配。

(1).高速差分信号设计规则

A.SATA是高速差分信号,一个SATA连接包含一个发送信号对和一个接收信号对,这些差分信号的走线长度差别应小于5mil。使差分对的走线长度保持一致非常重要,不匹配的走线长度会减小信令之间的差值,增加误码率,而且还会产生共模噪声,从而增加EMI辐射。差分信号线对应该在电路板表层并排走线(微带线),如果差分信号线对必须在不同的层走线,那么过孔两侧的走线长度必须保持一致。

B.差分信号线对的走线不能太靠近,建议走线间距是走线相对于参考平面高度的6~10倍(最好是10倍)。

C.为减少EMI,差分对的走线间距不要超过150mil。

D.SATA差分对的差分阻抗必须为100Ω。

E.为减少串扰,同一层其他信号与差分信号线对之间的间距至少为走线相对于参考平面高度的10~15倍。在千兆位传输速度的差分信号上不要使用测试点。

(2).避免阻抗不匹配的设计规则

A.注意避免不正确的走线宽度和走线相对于参考平面的高度,走线宽度和走线相对于参考平面的高度决定走线阻抗。

B.保持完整的参考平面。在高速信号走线两侧,走线相对于参考平面高度10倍距离范围内,参考平面不应被切断或有挖空的区域。

C.采用宽度过窄以致无法可靠蚀刻的走线,经常会导致走线的宽度或高度发生变化。从而产生问题。最小的走线宽度和走线相对于参考平面的高度应为4mil。

D.采用0402封装的10nF电容,尽量减小走线宽度与电容焊盘宽度的差别。

E.尽可能在同一层走线,如果一定要改变走线层,则必须保证走线层改变后仍有合适的回流路径。

2.SATA电路的仿真

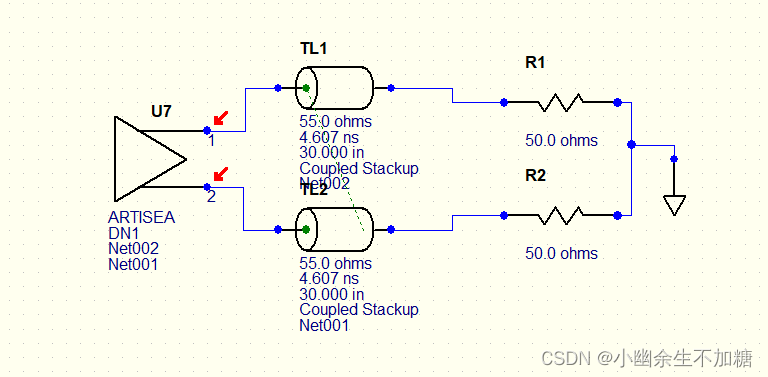

打开传输原理电路图1_SATA_hiloss_eye1 p5.ffs.如图所示:

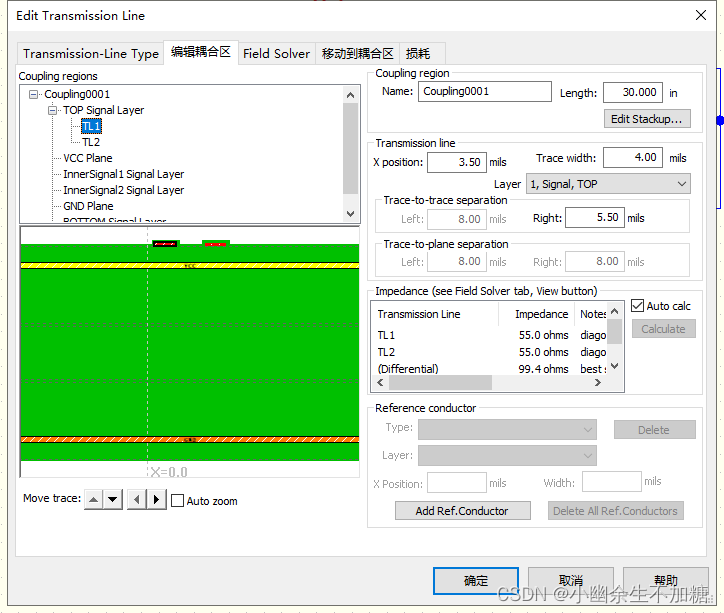

双击TL1,打开对话框,在传输线设置对话框中确认以下项目:

(1)线长为30in;

(2)每对线的线宽是4mil;

(3)线间距为5.5mil,设置如图所示:

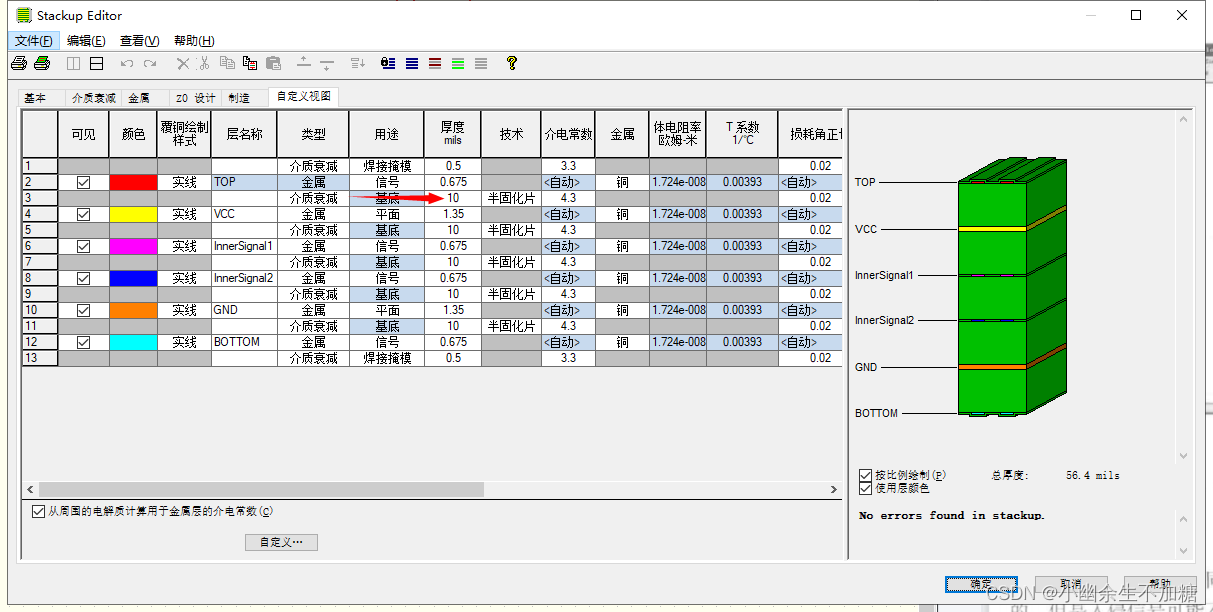

(4)单击“Edit Stackup…”,按钮确认。

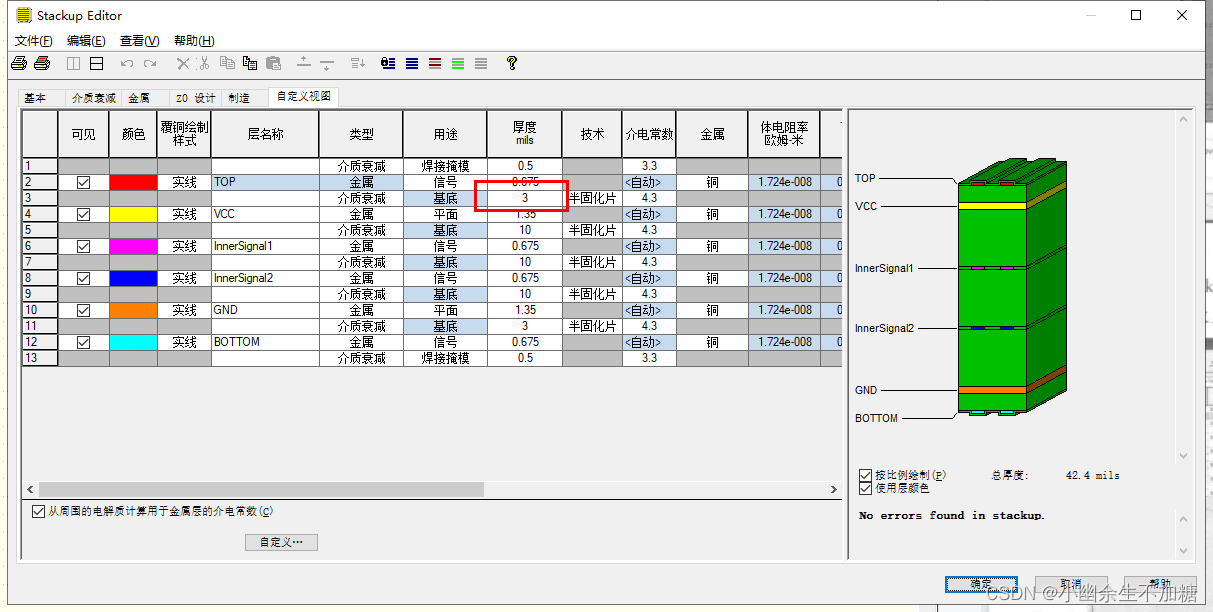

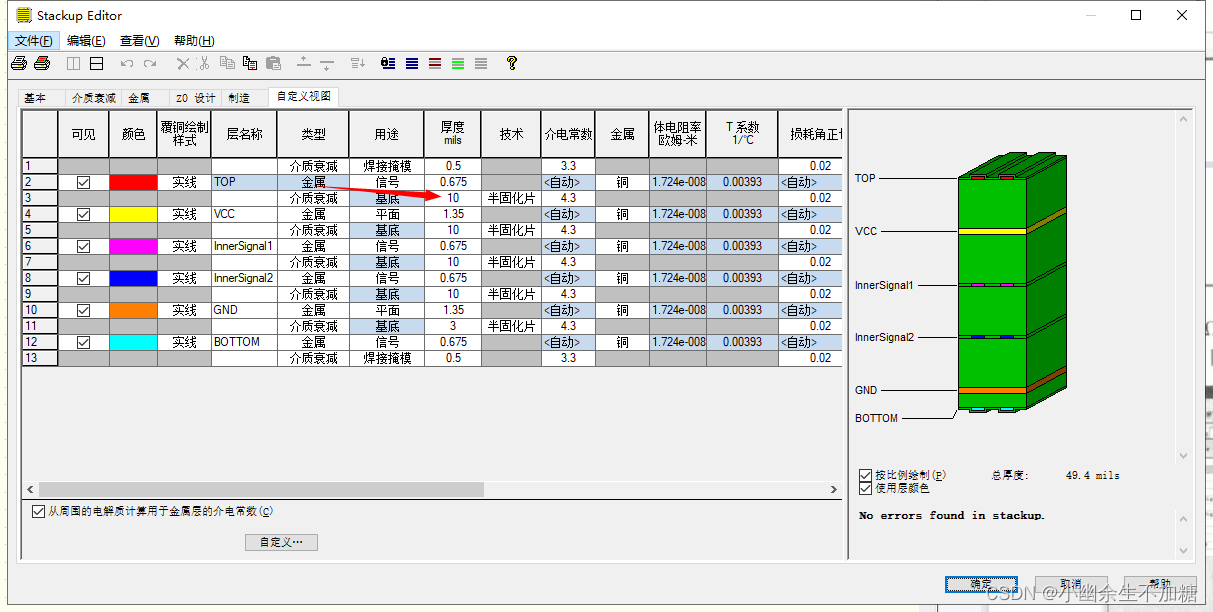

(5)第三层的厚度设置为3mil,如图所示:

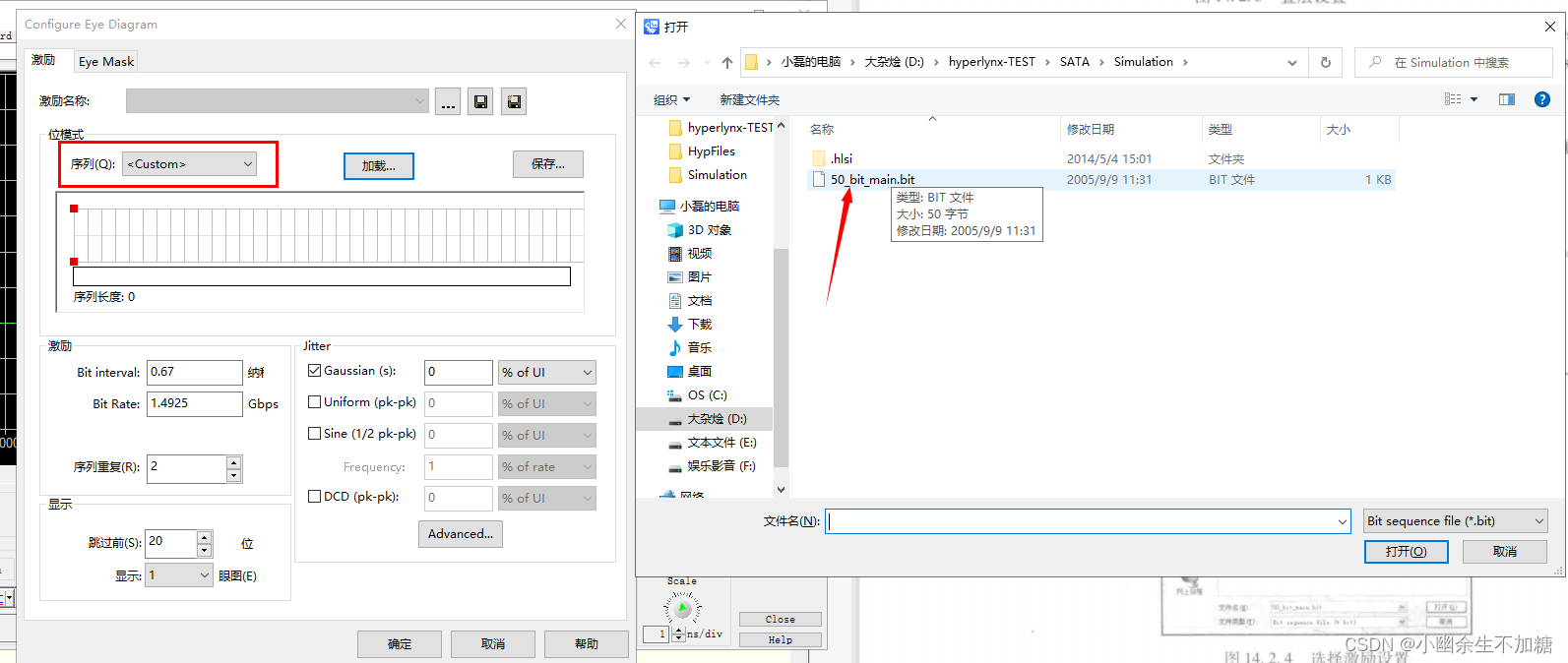

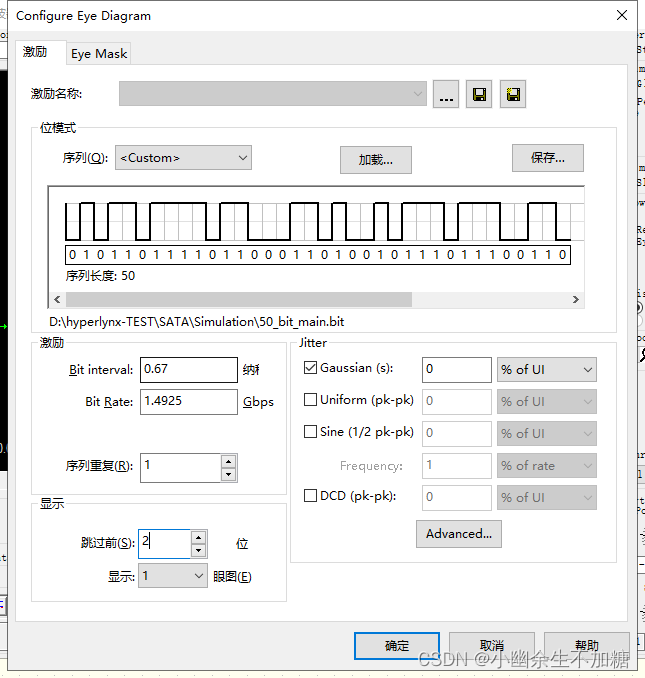

确保损耗仿真不被选中,单击 Simulate SI-Run Interactive Simulation in Oscilloscope然后选择眼图仿真模式,再单击“Configure”按钮,在Bit patten中选择Custom,单击“Load”按钮,打开如图所示对话框:

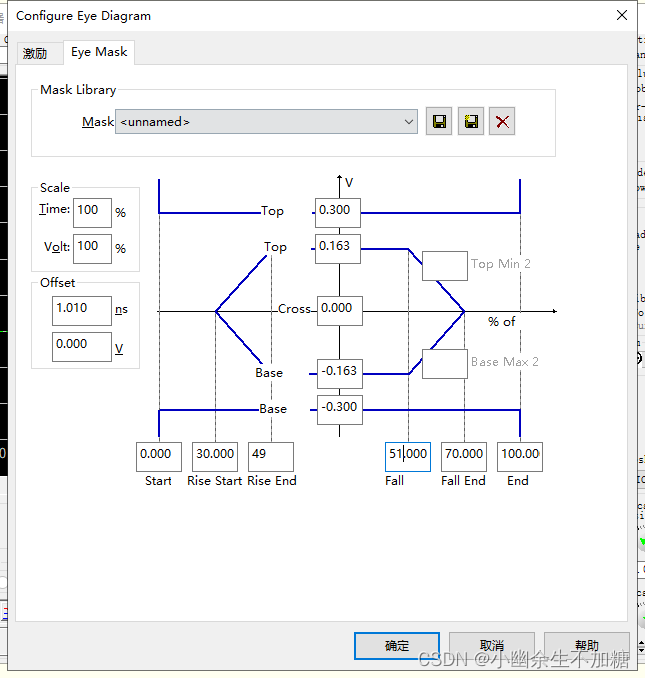

确认Bit interval设置为0.67ns,Sequence repetitions设置为1Skip first 2 bits,显示 1 eye(s),没有抖动。打开“Eye Mask”选项卡,选择SATA1_RX眼罩,眼图仿直参数设置如图所示:

仿真眼图模板参数:

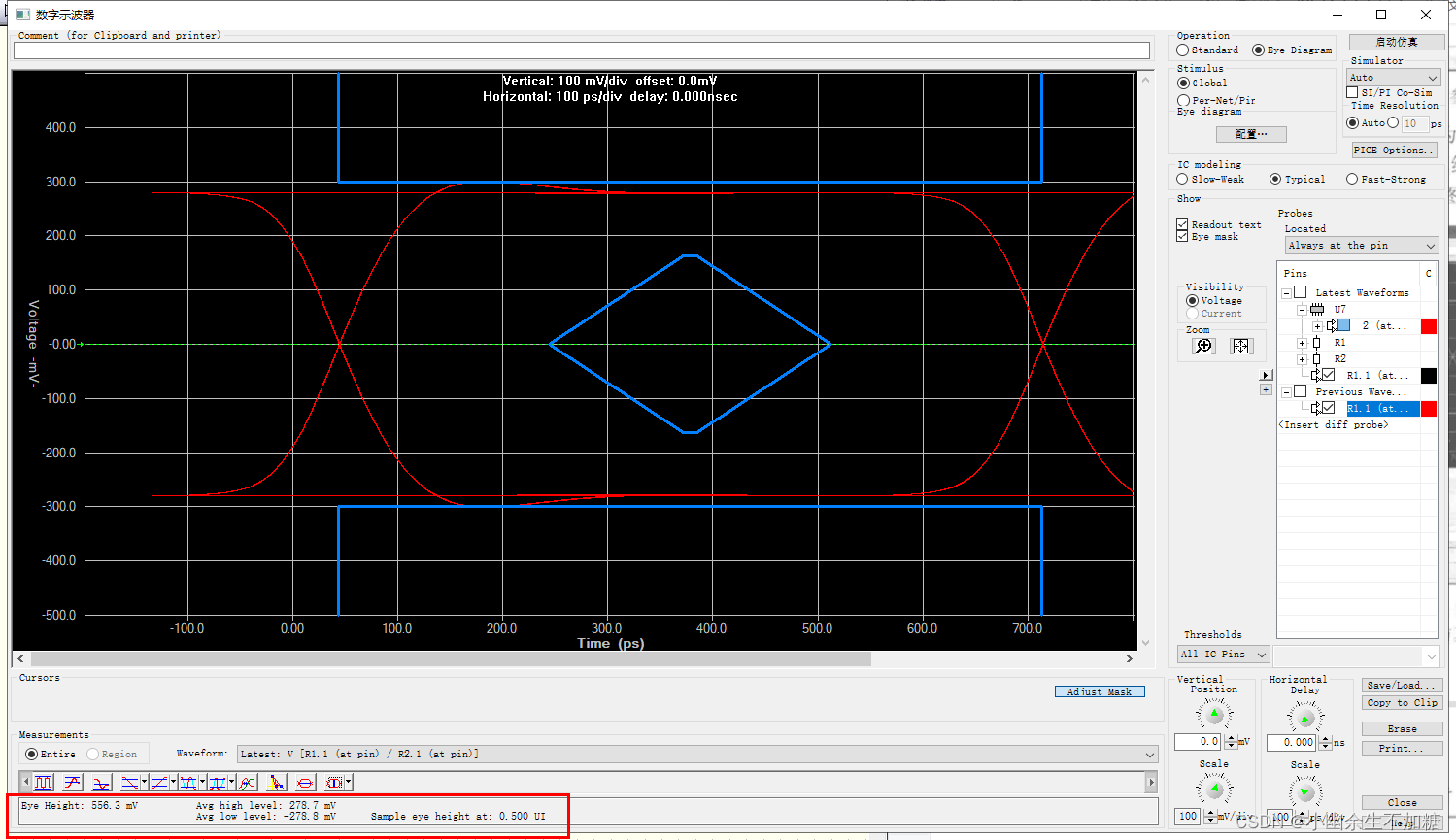

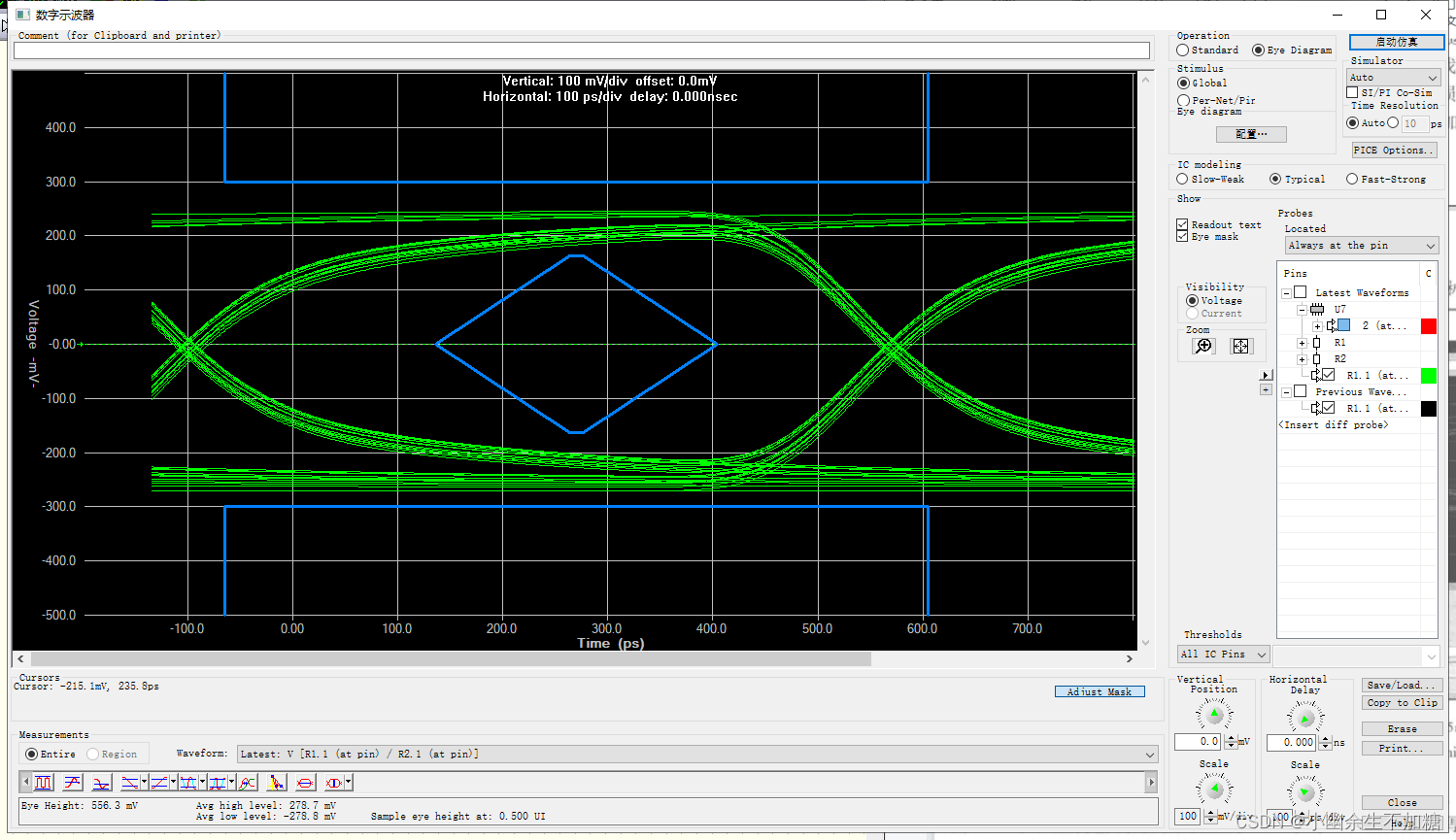

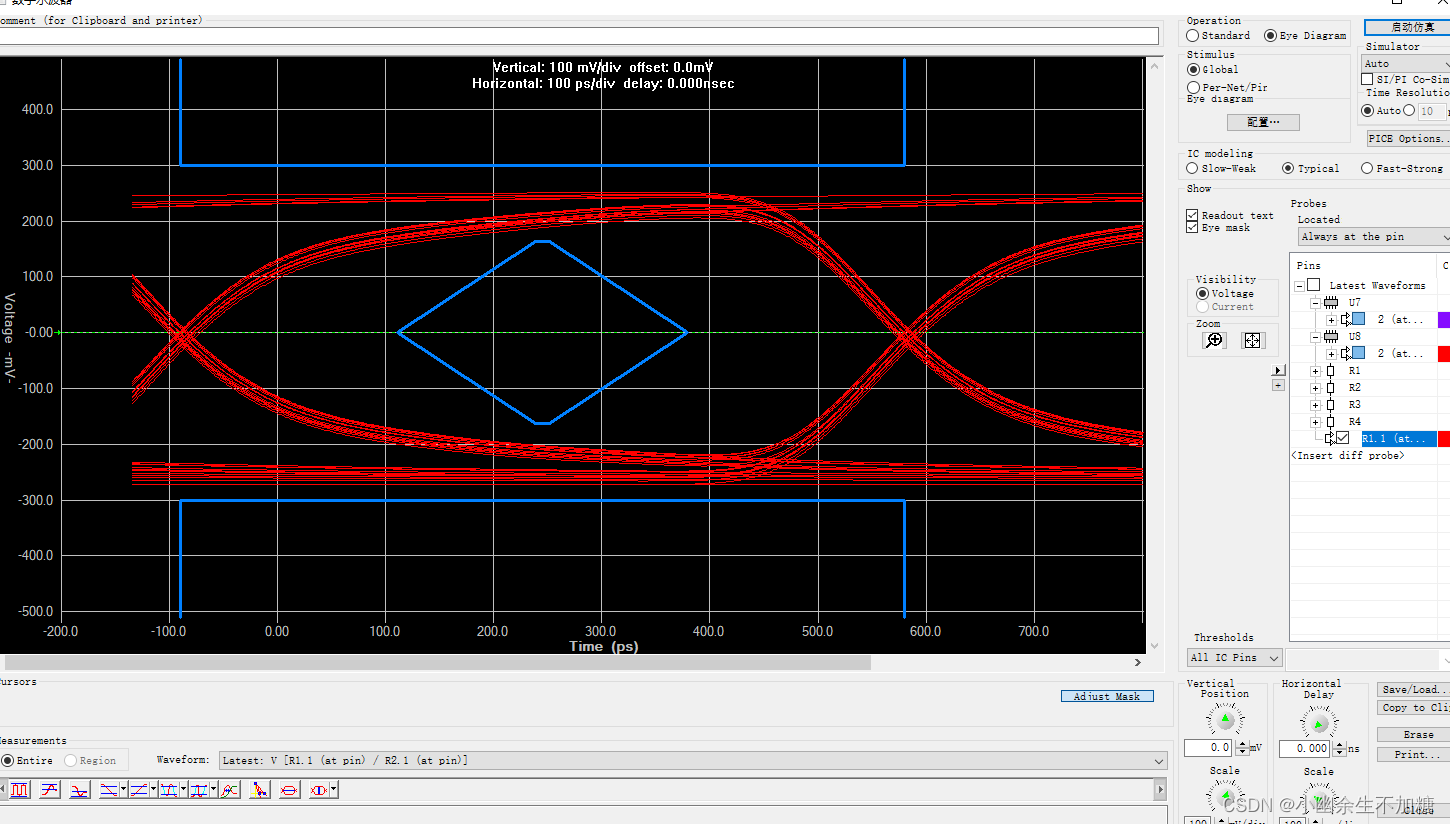

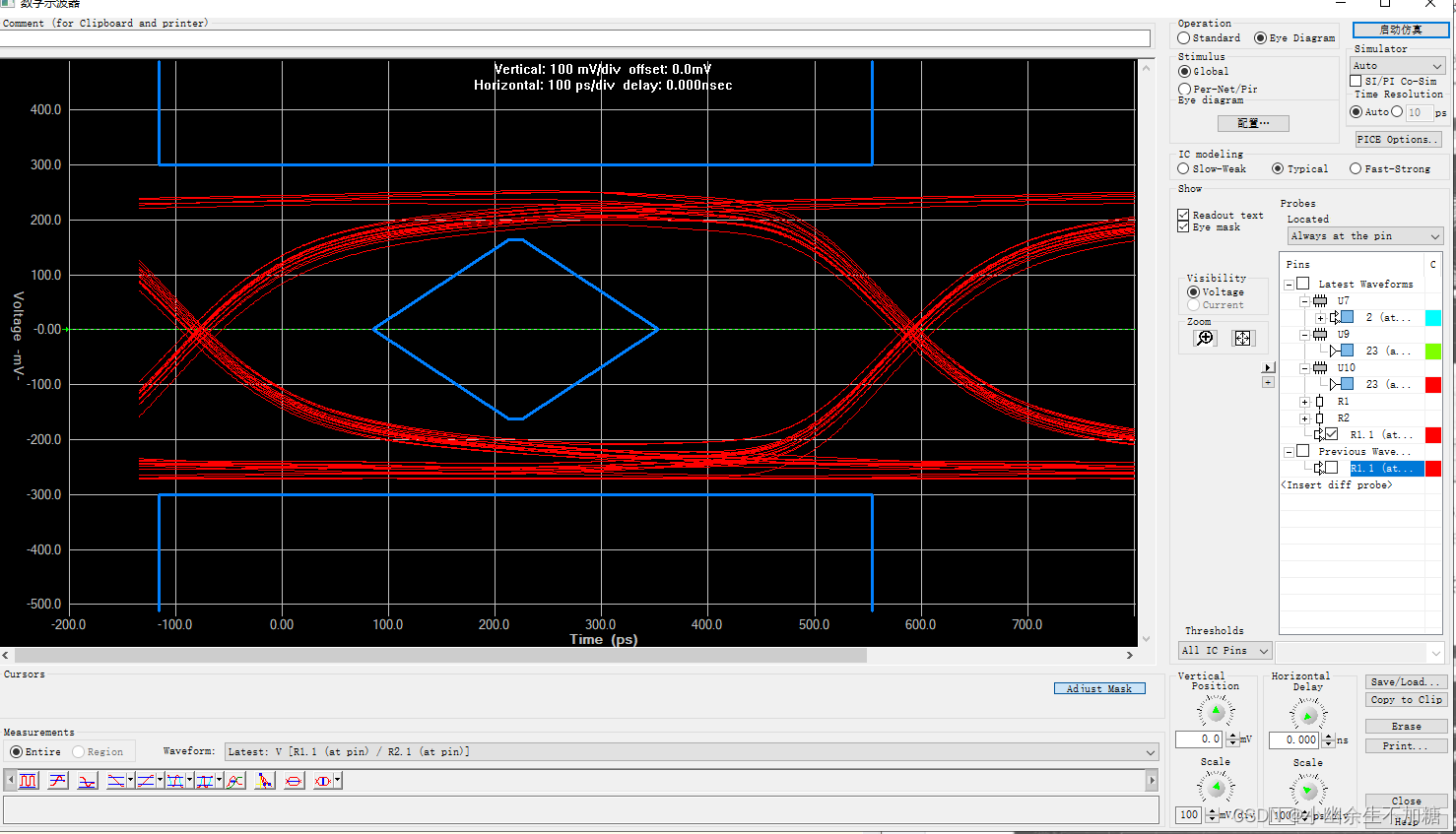

在示波器中确认Eye Mask被选中,设置垂直位置为0mV,标尺为100mV/div,设置水平标尺为100ps/div,单击“Start Simulation”查看仿真结果。单击“Adjust mask”调整眼置,使其置干示波器中心。理想情况的无损仿直眼图如图所示:

结果显示,实际的信号对应眼膜中央的部分留有很大的余量;对于眼膜要求的最低电压也满足要求,留有一定余地,而对于眼膜的最高电压,实际信号已经超过眼膜的临界限度。

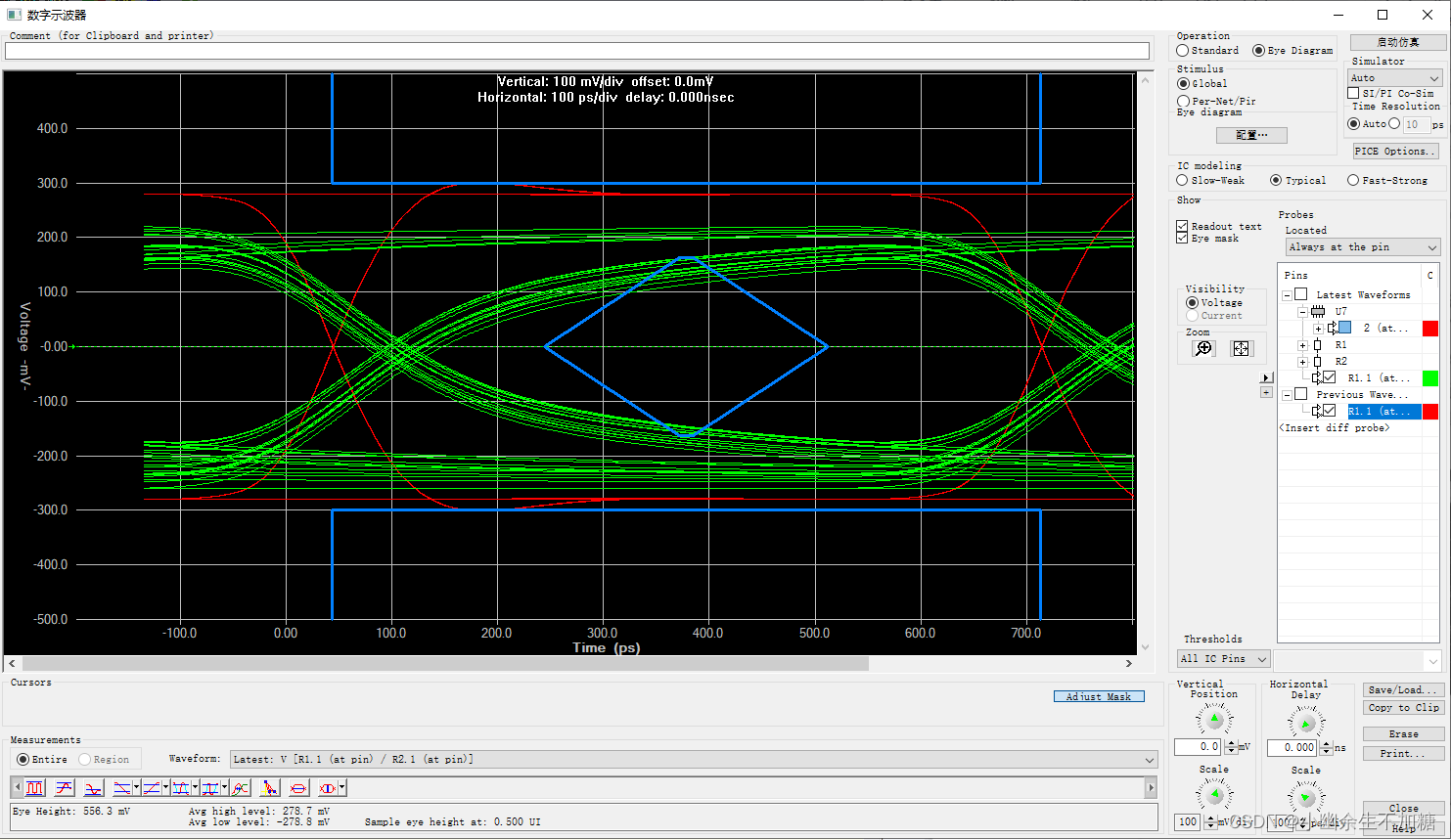

返回到电路原理图界面,选中损耗仿真,再次进行仿真,得到的有损仿真模式下的眼图如图所示:

得到的仿真结果如上图所示,这次的结果就不大符合眼膜的规格了,清楚地显示了在有损仿真模式下的信号损失衰减情况,明显没有满足眼膜的规格要求。

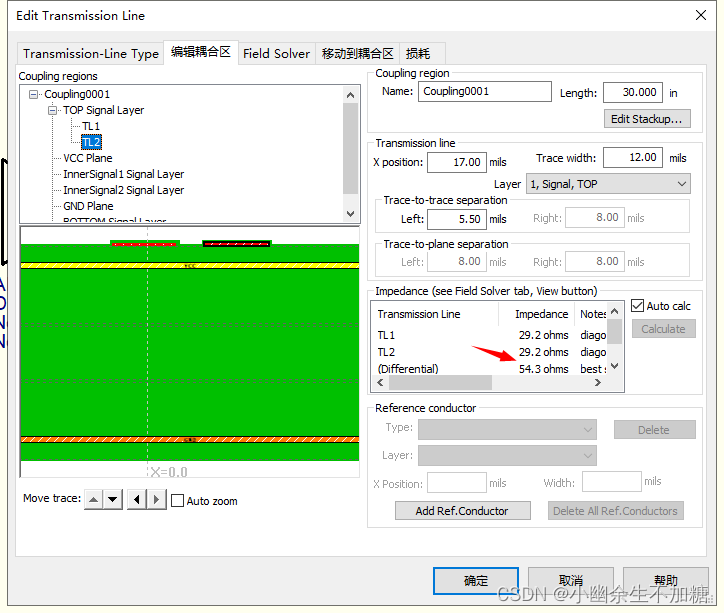

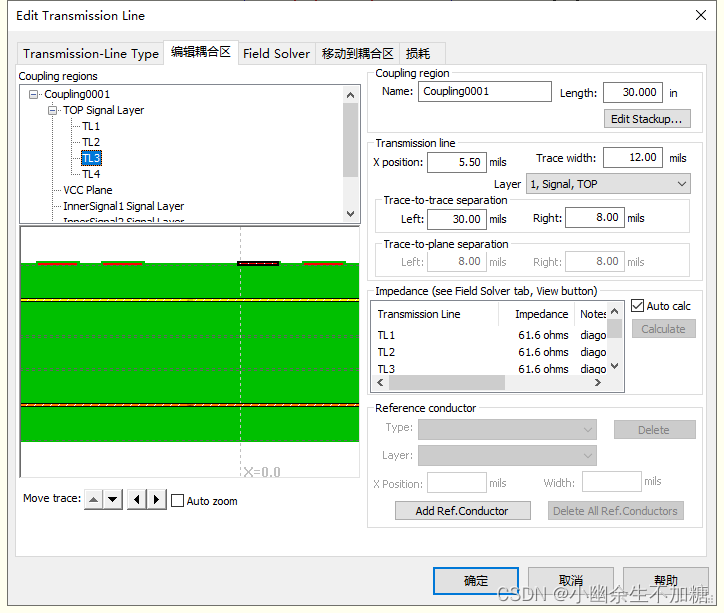

为了减少损耗,我们要对布线进行修改。回到传输线编辑对话框,双击TL1或者TL2打开传输线设置对话框,将线迹宽度改为12mil后,差分阻抗变为54.3Ω,如图所示:

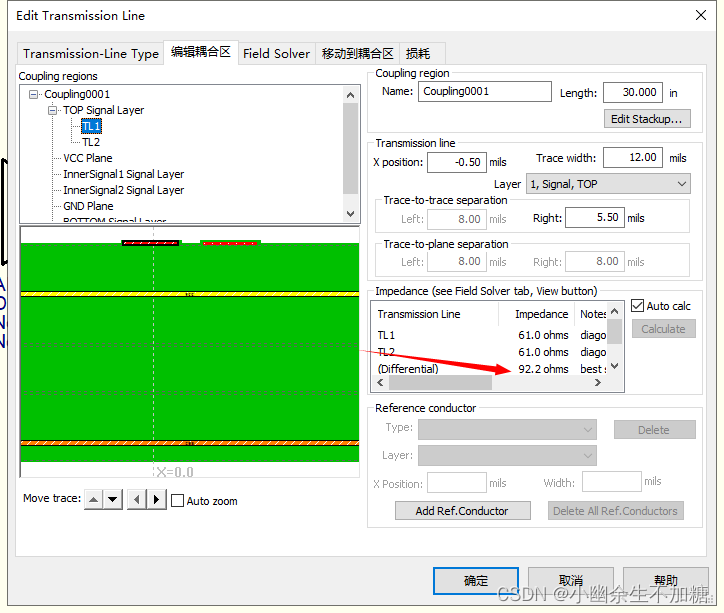

为了保持100Ω的差分阻抗,将叠层第3层厚度改为10mil,如图所示,差分阻抗上升为92.2Ω,同时将线间距改为8mil,如图所示:

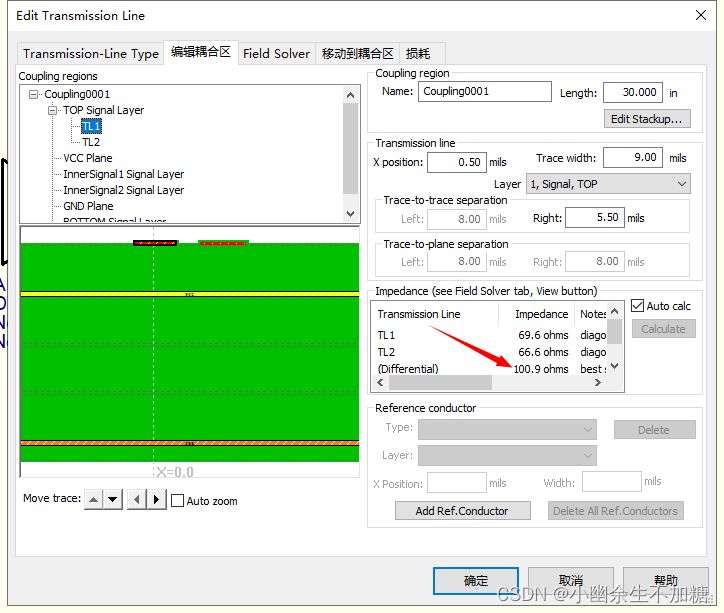

最后差分阻抗为100.9Ω,在新的参数条件下重新运行仿真,如图所示。

新的叠层设置得到了一个满足规格的眼图。说明我们新建的这个叠层同样为100Ω差分电阻,通过增加线宽、线间距及电介质的高度使信号损失减小。

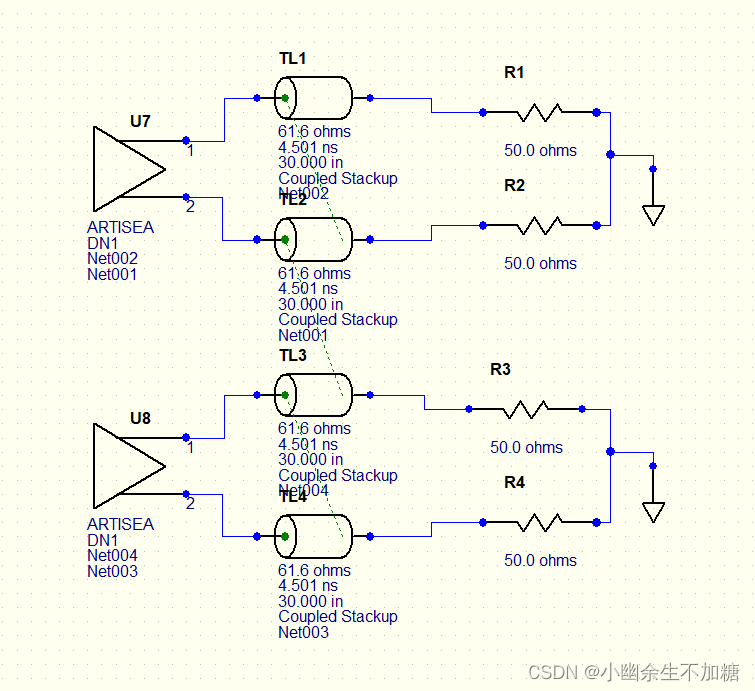

上面的设置得到的信号已满足要求,下面我们增加一组传输线,仿真它们之间的串扰。

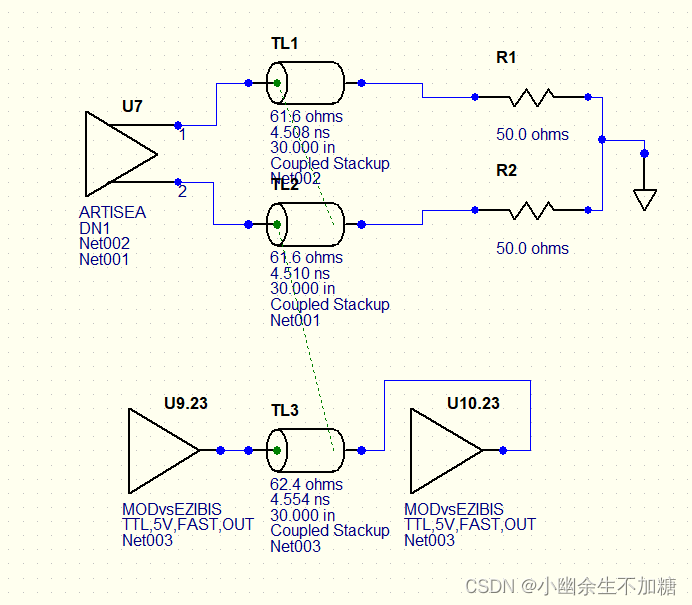

打开3_SATA_loloss_SATAxtk_eyelp5.ffs,如图所示,传输线内部间距为8mil,线宽为12mil,两组传输线的间距设置为30mil,第三层叠层设置厚度为10mil,设置如图所示:

打开示波器,单击“Simulate SI”→“Interactive Simulation in Oscilloscope”,在“Operation”下选择眼图模式,设置和上一个仿真设置相同,得到眼图仿真的结果如图所示:

可以看出入侵信号同为SATA信号时,串扰并没有造成什么影响,眼图依然是符合规格的。但是入侵信号可能不只是SATA信号,也可以是多样的其他信号。

在新的电路图中选择的入侵信号为波动范围5V的单端信号,即打开4_SATA_loloss_5Vxtk_eyelp5.ffs文件,打开原理图如图所示,SATA参数设置和之前的相同,如图所示:

入侵信号改为波动范围为5V的单端信号的串扰测试电路图。

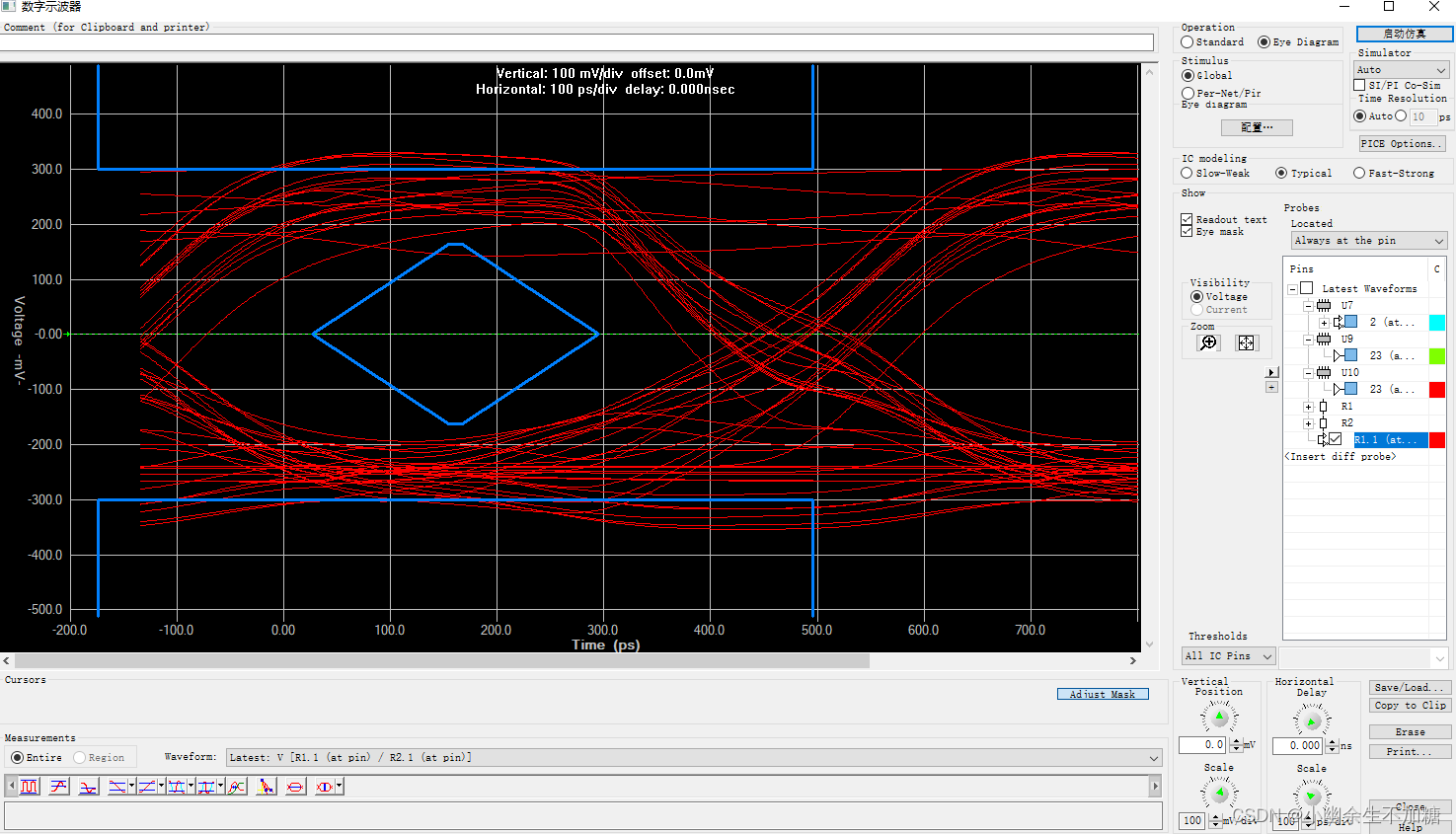

仿真结果如图所示。

由上图可以看出,当入侵信号为5V的单端信号时,在之前的参数设置下,眼图图像很不规范,不符合要求,明显可以看出串扰的影响很大。因此选择扩大传输线之间的间距来减小串扰的影响。将传输线和人侵信号线间距增加到50mil,重新运行仿真,结果如图所示:

提升50mil之后的眼图:

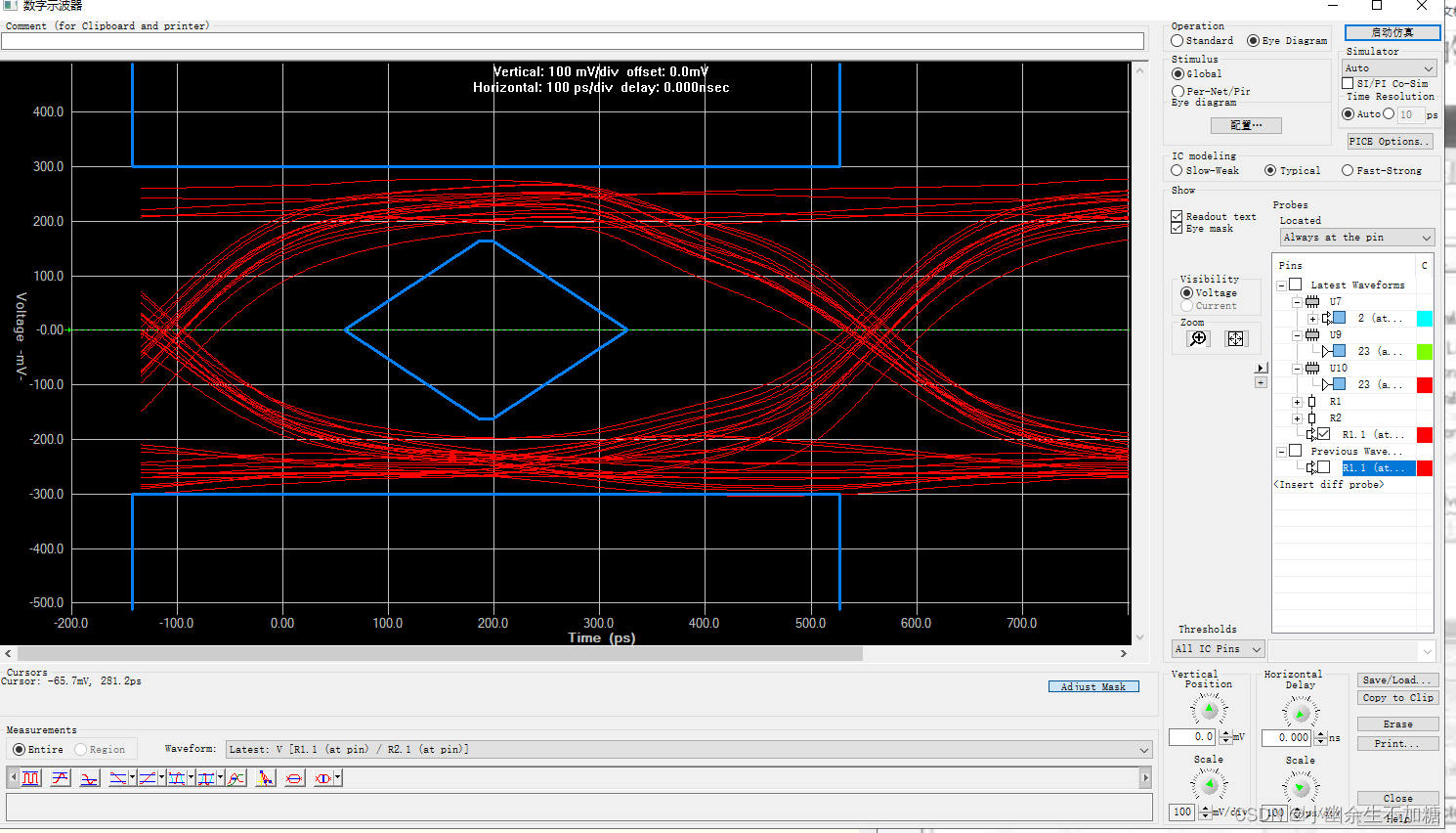

串扰的影响依然存在,但是较之前相比已经有所减少;继续增加间距,将传输线和入侵信号线的间距增加为100mil,仿真结果如图所示:

可以看到,当间距扩大到100mil后,串扰的影响很小,传输信号的眼图也符合规格要求了。

![[转]SATA电源线和数据线接口定义](https://img-blog.csdn.net/20170926221822096?watermark/2/text/aHR0cDovL2Jsb2cuY3Nkbi5uZXQvcWxleGNlbA==/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70/gravity/Center)