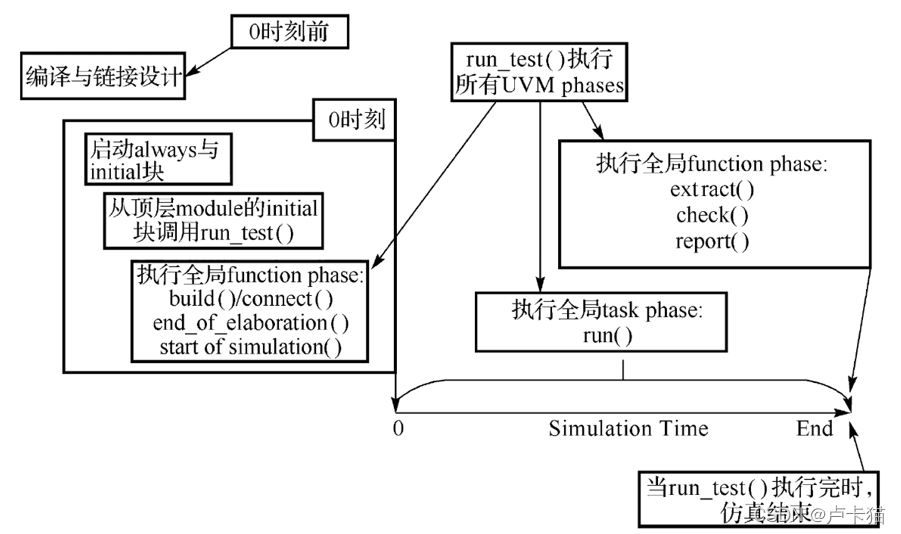

UVM中的phase按照其是否消耗仿真时间($time打印出的时间)可以分为两大类,一类是function phase(不耗费仿真时间),另一类是task phase(耗费仿真时间)。task phase也可以叫做run_ phase ,给DUT施加激励、监测DUT的输出都是在这些phase中完成的。

task phase中run_phase和十二个小phase并行运行。(该运行关系面试常问)

phase机制中使用频率最高的三个phase (build_phase 、connect_phase、main_phase)

(UVM为什么引入12个小的phase呢? )分成小的phase是为了实现更加精细化的控制,reset、configure、main、shutdown四个phase是核心,这四个phase通常模拟DUT的正常工作方式,在reset_phase对DUT进行复位、初始化等操作,在configure phase则进行DUT的配置,DUT的运行主要main_phase完成,shutdown phase则是做一些与DUT断电相关的操作。

phase机制的执行顺序(除了build phase外),所有不消耗仿真时间的phase(function phase)都是自下而上执行的,比如connect phase。

(面试中除了爱问build phase以及connect phase的执行顺序外,还会问为什么是这样执行。)UVM设计的哲学就是在build phase中做实例化的工作,driver和monitor都是agent的成员变量,所以它们的实例化都要在agent的build phase中执行,如果在agent的build phase之前执行driver的build phase,此时driver还没有实例化,所以调用driver.build phase只会引发错误。

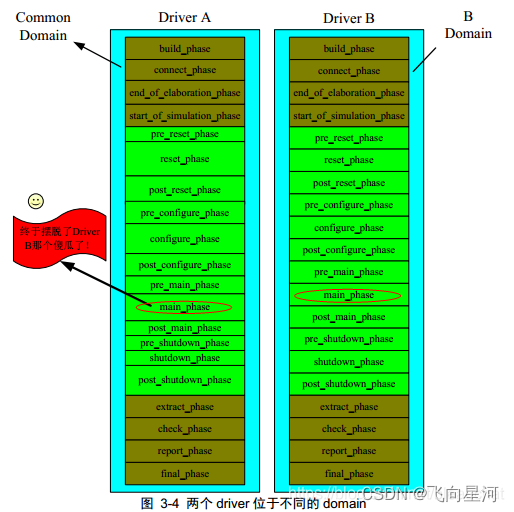

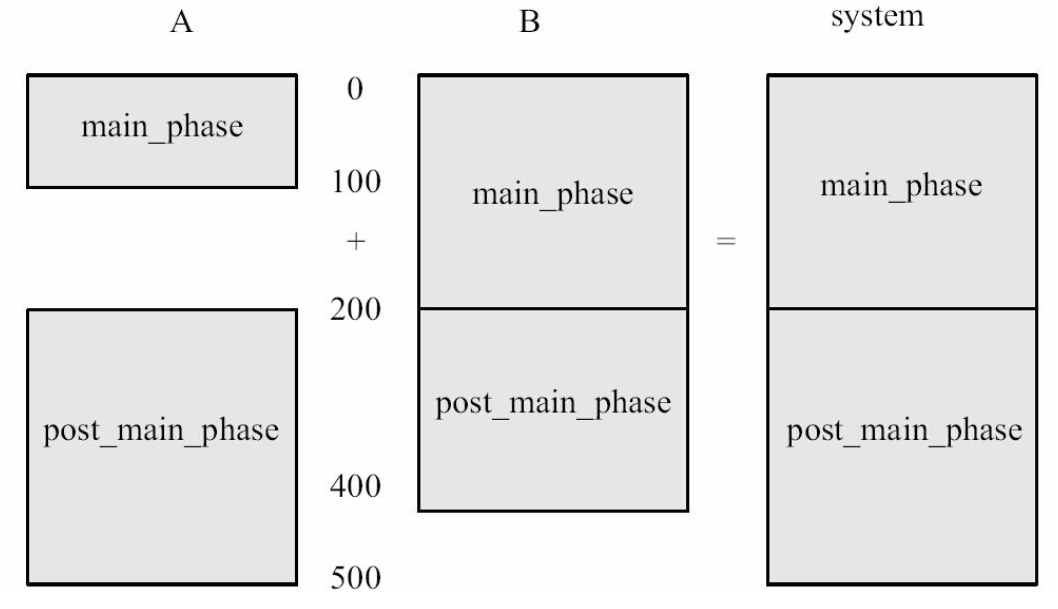

(phase机制的同步)这个思想十分重要,不同componment的同个phase之间是同步的,就是他们的main phase/build phase是同时完成的,比如drive的main phase100us就可以完成,但monitor的main phase 需要200us,但driver需要等待monitor100us才能一起进入下一个phase阶段。但这种同步不仅适用于不同componment的动态运行phase之间,还适用于run_phase和run_phase之间。

(phase机制的跳转)phase机制的跳转在入门项目中几乎没有用到,面试问的相对来说少些。phase机制若向前跳转,不能跳到function phase中,uvm_pre_reset_phase::get()后的所有phase都可以。而向后跳转就没有限制了,甚至可以跳到final phase。

(phase机制的优点)在不同时间做不同的事情,是UVM中phase的设计哲学。phase的引入在很大程度上解决了因代码顺序杂乱可能引发的问题,遵循UVM的代码顺序划分原则(如build phase做实例化工作、connect phase做连接工作等),可以在很大程度上减少验证平台开发者的工作量,使其从一部分杂乱的工作中解脱出来。

(超时退出机制)在UVM中通过uvm_root的set_timeout函数可以设置超时时间,set_timeout函数有两个参数,第一个参数是要设置的时间,第二个参数表示此设置是否可以被其后的set_timeout语句覆盖。你所做项目的超时时间要记一下,面试很可能会问到。

(objection 机制)在进入某一phase时,UVM会收集此phase提出的所有objection,并且实时监测所有objection是否已经被撤销了,当发现所有都已经被撤销后,那么就会关闭此phase,开始进入下一个phase。当所有的phase都执行完毕后,就会调用$finish来将整个的验证平台关闭。如果想执行一些耗费时间的代码,那么要在此phase下任意一个componment中至少提起一次objection。上述结论只适用于12个run-time的phase,对于run_phase则不适用,由于run_phase与动态运行的phase是并行运行的,如果12个动态运行的phase有objection被提起,那么run_phase根本不想与爱raise_objectoin 就可以自动执行。一般来说,在一个实际的验证平台中,通常会在以下两种objection的控制策略中选择一种,第一种是在scoreboard中进行控制,第二种是在sequence中提起sequencer的objection,当seuqence完成后,在撤销此objection。其中第二种方法应用较多,这种方式是UVM提倡的方式,UVM设计的哲学就是全部由sequence来控制激励的生成,因此一般情况下只在sequence中控制objection。

(set_drain_time)在sequence中,发送完最后一个transaction,如果此时立刻drop_objection,那么最后一包数据可能无法被接收到,所以有了set_drain_time机制。当UVM在main_phase检测到所有的objection被撤销后,接下来会检查有没有设置drain time。如果没有设置,则马上进入post_main_phase,否则延迟drain time 后再进入post_main_phase。

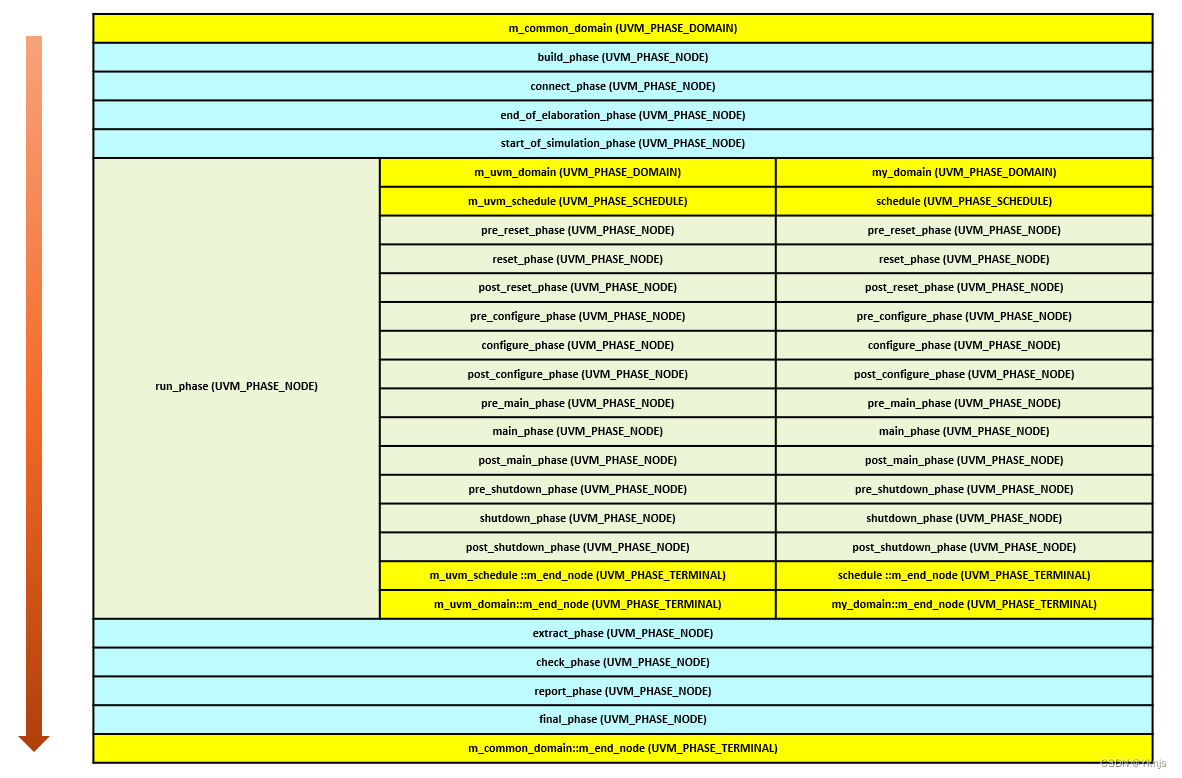

(domain机制)domain机制把两块时钟域隔开,之后两个时钟域内的各个动态运行的phase就可以不必同步,注意,这里domain只能隔离run-time的phase,对于其他的phase,其实还是同步的,即两个domain的run_phase依然是同步的吗,其他的function phase也是同步的。