文章目录

- AHB信号

- 基本AHB传输

- 传输类型

- 其它AHB控制信号

- 关注作者

AHB信号

- HRESETn 低电平有效

- HADDR[31:0] 32位系统地址总线

- HWDATA[31:0] 写数据总线,从主设备写到从设备

- HRDATA[31:0] 读数据总线,从从设备读到主设备

- HTRANS 指出当前传输的状态,有IDLE、BUSY、NONSEQ、SEQ四种

- HSIZE 指出当前传输的大小

- HBURST 指出传输的burst类型

- HRESP 从设备发给主设备的总线传输状态,有OKAY、ERROR、RETRY、SPILT四种

- HREADY 高:从设备指出传输结束 低:从设备需延长传输周期

NONSEQ当前地址和前一地址无关,SEQ指的是当前地址和前一地址连续

HBURST有八种

retry不影响当前被拒绝的master的优先级,spilt会影响,arbiter会降低master的优先级

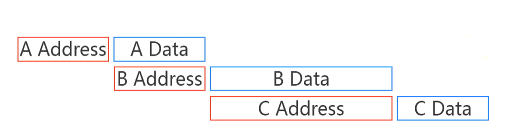

基本AHB传输

两个阶段

- 地址周期,只有1个cycle

- 数据周期,由HREADY信号决定需要几个cycle

流水线传送,先是地址周期,然后是数据周期。

一次无需等待状态的简单传输

需要两个等待周期的简单传输

master最多等你16个周期,否则使用retry或hresp

流水线

传输类型

HTRANS[1:0]:当前传输的状态

- IDLE(00)主设备占用总线,但没进行传输;两次burst传输中间主设备发IDLE

- BUSY(01)主设备占用总线,但是在burst传输过程中还没有准备好进行下一次传输;一次burst传输中间主设备发BUSY

- NONSEQ(10)表示一次单个数据的传输;或者一次burst传输的第一个数据;地址和控制信号与上一次传输无关

- SEQ(11)表示burst传输接下来的数据;地址和上一次传输的地址是相关的

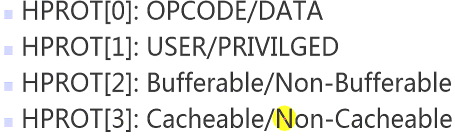

其它AHB控制信号

- HWRITE 高电平写 低电平读

- HSIZE[2:0]

HPORT[3:0]

关注作者

- 自述

作者是一位中科大数字设计专业的研究生,水平有限,如有错误,请大家指正,想要与大家一同进步。 - 经历

曾获得国家奖学金,“高教社杯”数学建模国家二等奖等 - 陆续更新:

1.与verilog数字设计相关的一些基础模块设计

2.SV与UVM

3.数字IC设计/验证过程中一些工具及语言的用法

4.保研与竞赛经历等 - 微信公众号

欢迎大家关注公众号“数字IC小白的日常修炼”,期待与大家一同仗剑遨游数字IC世界。