总结

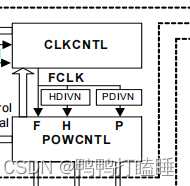

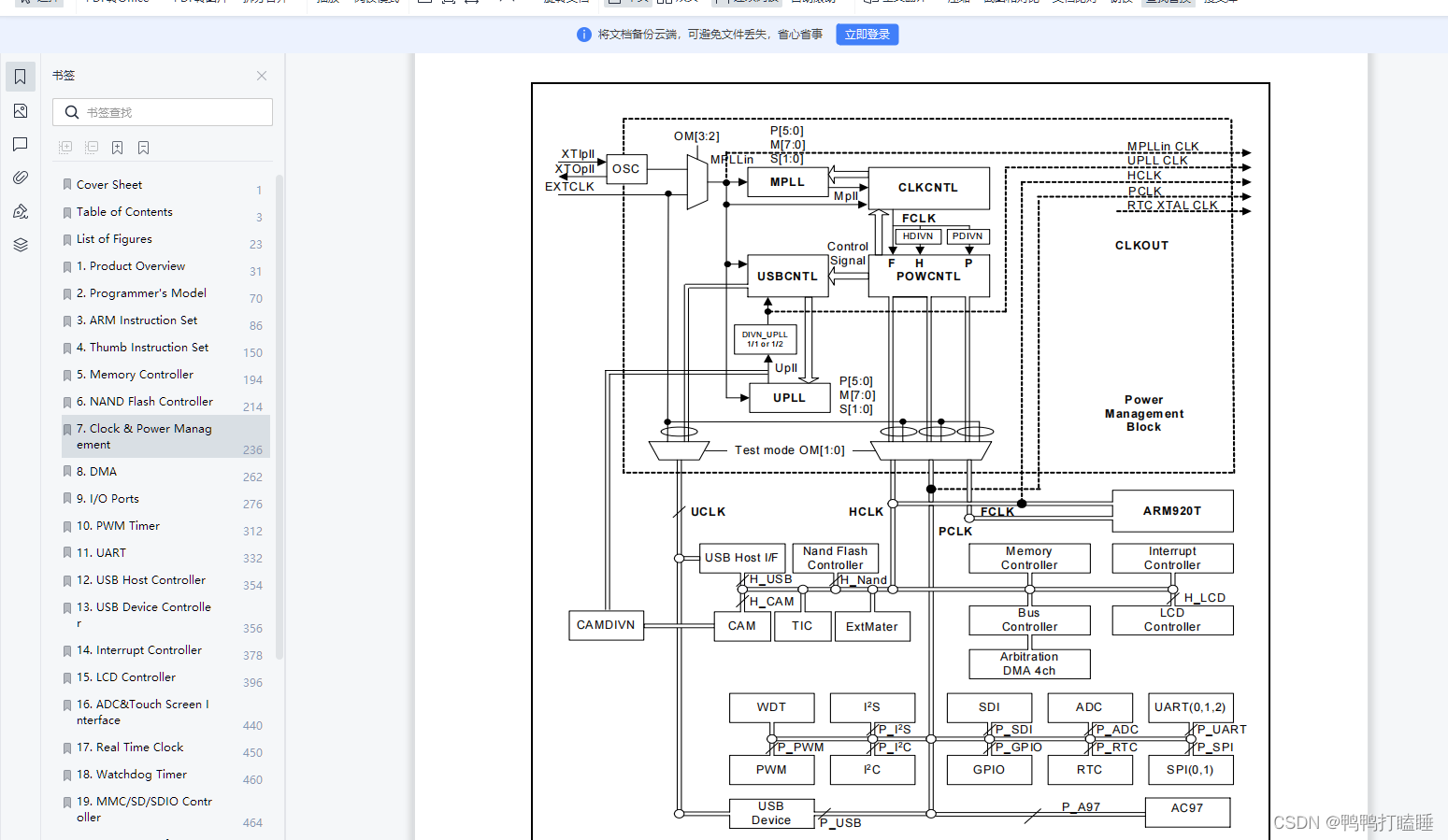

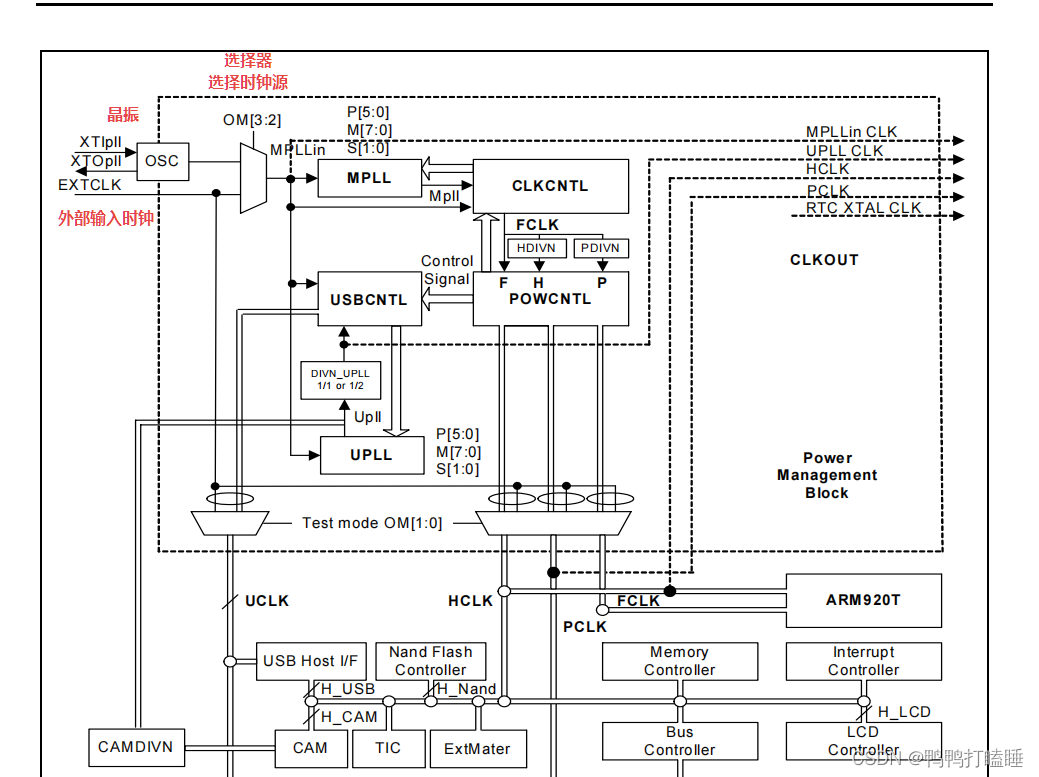

这里soc从外界得到外部时钟源,通过硬件的锁相环(PLL)进行加速,

加速完的内部时钟通过分频为三个时钟源 cpu_fclk ahb_hclk apb_pclk

给不同的器件进行使用

soc内部时钟源获取和分类的流程

从datasheet中的第7章,把所有器件的时钟源说明清楚 从外部的时钟源进来

到分发到两个总线上给各种器件进行使用

高速设备和低速设备,和他们所在的总线上

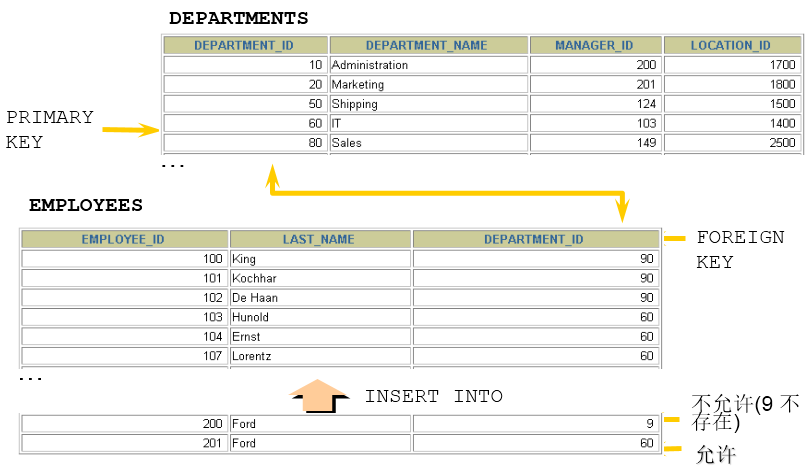

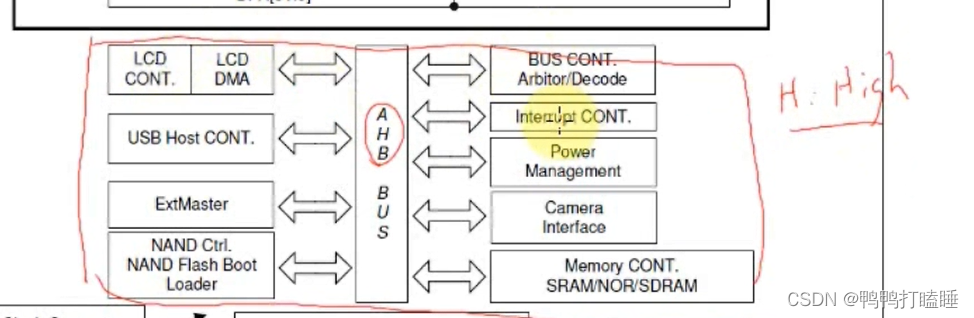

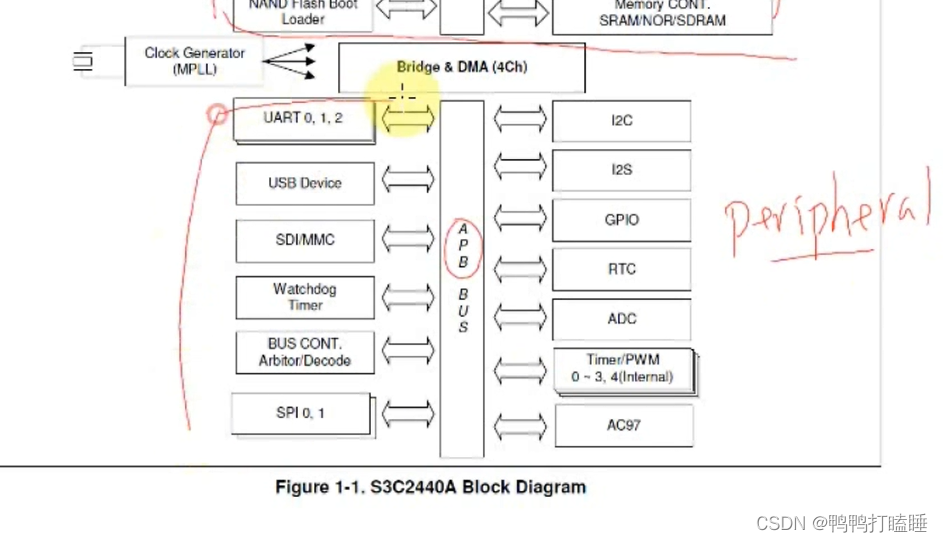

soc 也就是system on chip, 里面有cpu和各种外设

外设分了两部分挂载在两个总线上

ahb总线 :hight 高速总线 比如lcd控制器,中断控制器,usb控制器

apb总线:peripheral 外围设备总线 低速设备 i2c,spi等

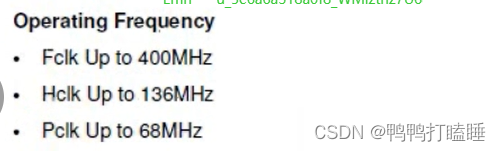

上面就有了三个时钟:cpu_fclk ahb_hclk apb_pclk 在datasheet里面能看见三个时钟的最大速率

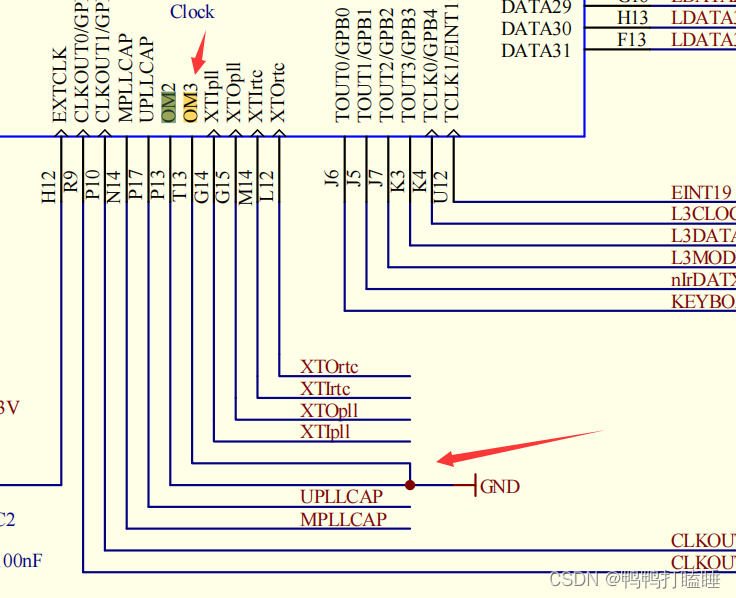

外部时钟源的选择

外部时钟源有两个,一种是硬件的时钟源 一种是外部输入时钟

在原理图中,硬件时钟源是一个12Mhz的晶振

通过一些硬件单元(PLL锁相环)产生上面三种不同内部时钟频率

根据datasheet 看见外部输入时钟源有两个 一个12M晶振 还有一个外部输入的时钟

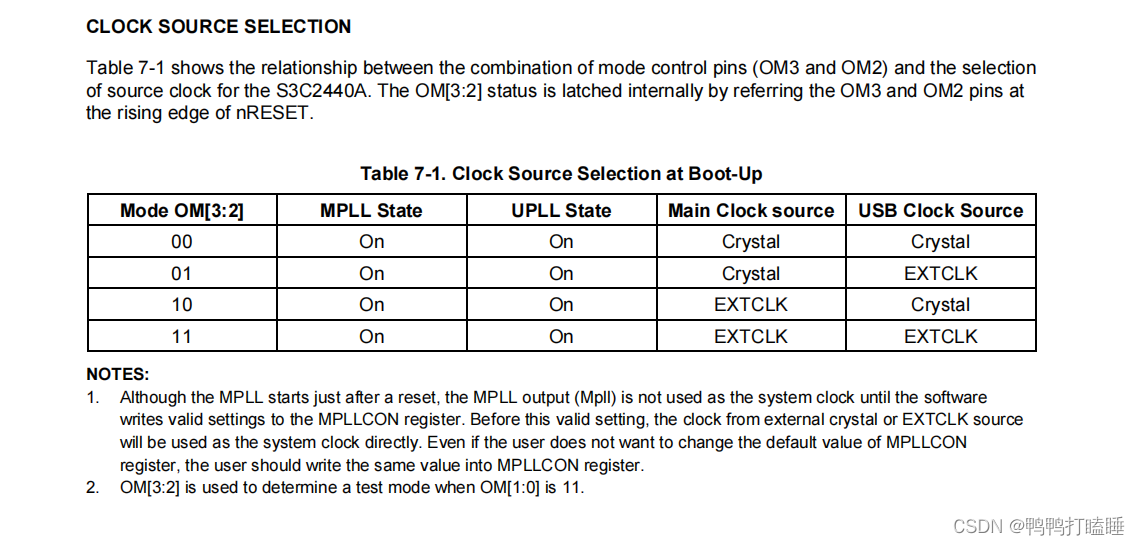

通过更改OM引脚的值,修改 PLL索取时钟源的不同

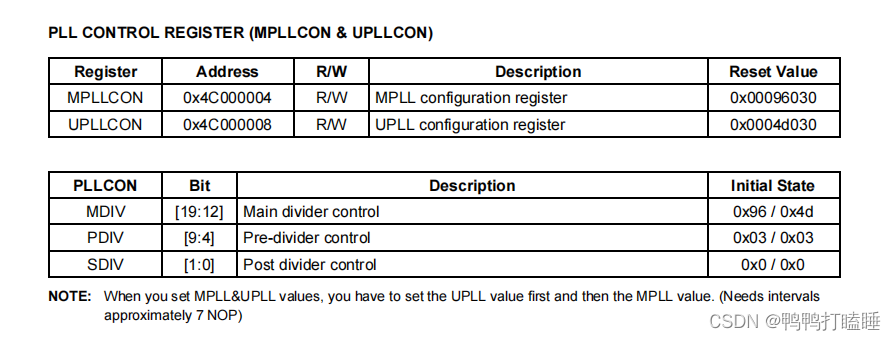

datasheet上描述 有两个PLL,MPLL(main_pll)生产时钟给cpu用,UPLL生产时钟给usb用

OM3和OM2在下面图上都接地,根据datasheet,表示用硬件晶振12M作为时钟源

输出时钟频率的选择

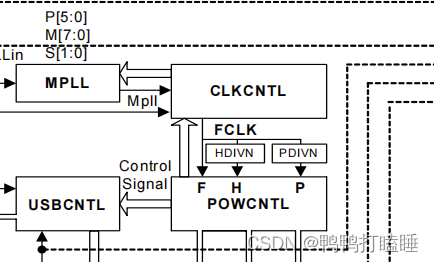

外部晶振进入后,到MPLL控制 PMS三个参数选择输出时钟的频率

最后的分频

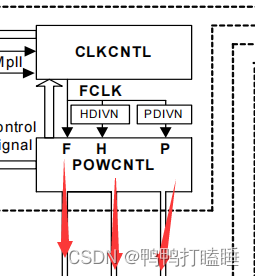

MPLL后得到时钟频率放入clkcntrl里面,直接作为FCLK传给cpu

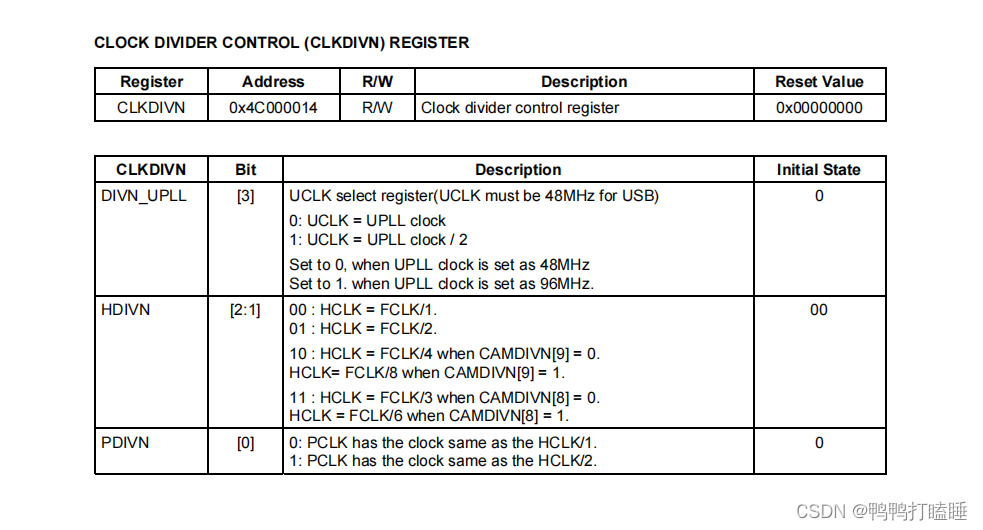

经过HDIVN分频,得到HCLK,经过AHB总线传给各种高速设备

经过PDIVN分频,得到DPIVN,传给APB总线各种低速外设

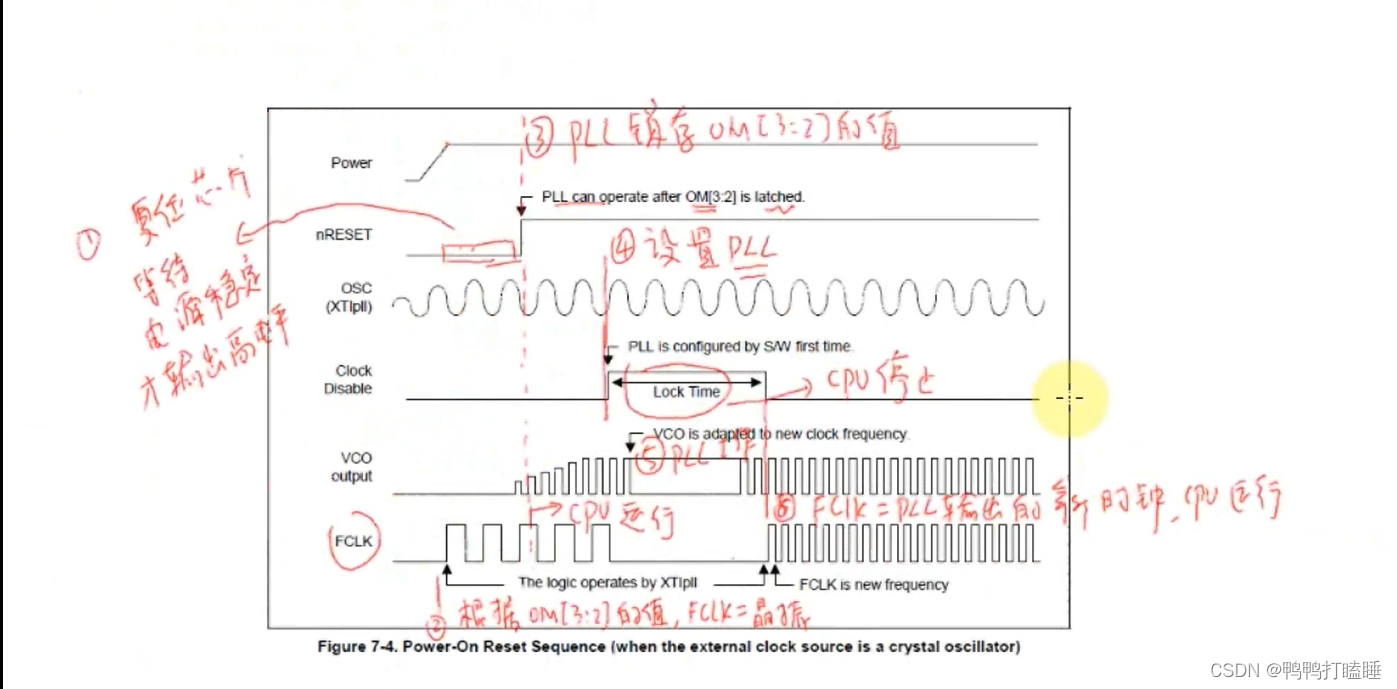

cpu在软件上获得时钟的时序

先看设置时序

还是在datasheet上进行搜索 下面这个图显示了 开机重置序列过程中的时钟行为。

根据图中分了几个部分

1.电源power上拉后,nreset等待电源稳定才输出高电平

2.刚开始时,fclk等于硬件的晶振12M

3.PLL锁存OM32的引脚的值

4.设置PLL的值,根据图中lock_time拉高,时钟disalble 同时FCLK停止,cpu停止

5.FCLK等于PLL输出的时钟,cpu重新运行

寄存器分析

根据上面的步骤,继续在datasheet上面搜索,需要配置的寄存器

参考表中的输入频率是12MHZ的时候需要输出的频率为400MHZ 这时候配置流程图中的MPLL

给MPLLCPM寄存器写 mdiv位0x5c pdiv位0x01 sdiv位0x01 配置输出400Mhz的时钟

如果不想用参考的值,可以根据公式自己进行计算拿取想要的MPLL输出参数

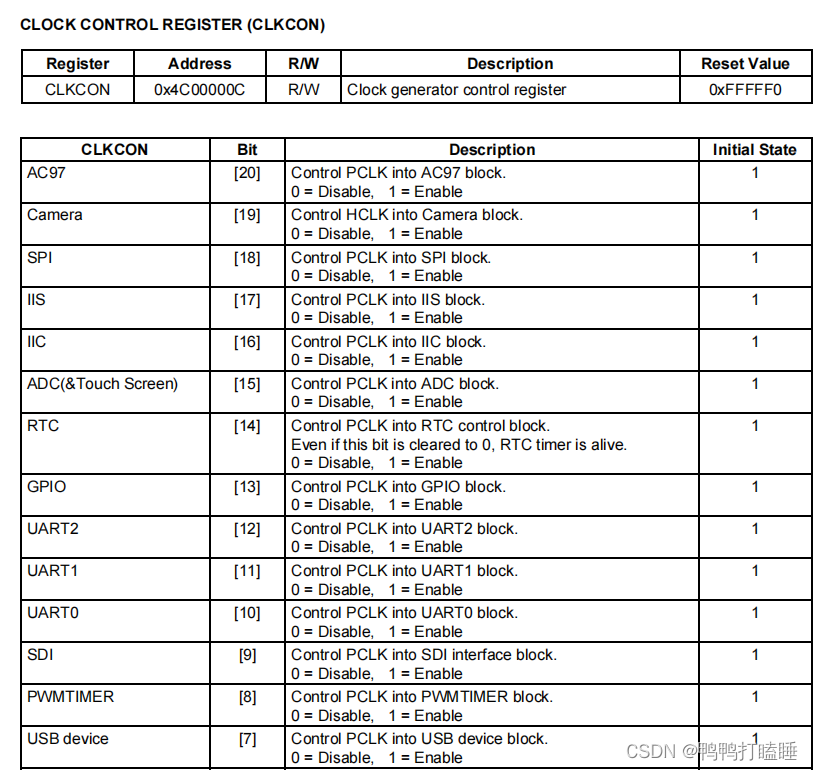

设置寄存器clkcon 控制哪些外设时钟需要使能,哪些不需要

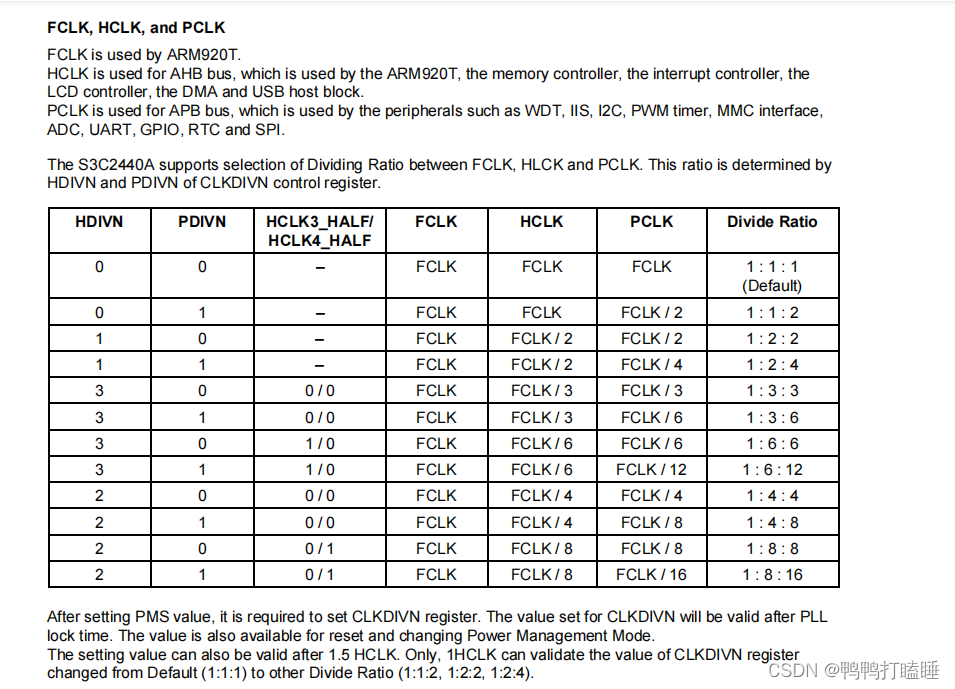

设置HDIVN寄存器 让CPU时钟进行分配 分为HCLK和PCLK时钟

根据流程图上面说的,只要控制 HDIVN才能去把FCLK 分配为 HCLK和PCKLK

翻找datasheet ->determined by HDIVN and PDIVN of CLKDIVN control register.

因为被定义在 CLKDIVN 寄存器 下面就是配置CLKDIVN 这个寄存器