目录

1.VGA视频接口介绍

2. VGA的硬件电路介绍

3.VGA电气特性

4. VGA接口信号

5. VGA时序

VGA时钟计算

1.VGA视频接口介绍

VGA(Video Graphics Array)视频图形阵列是IBM于1987年提出的使用模拟信号的电脑显示接口标准。共15pin,分3排每拍5孔,是显卡上应用比较广泛的接口类型,绝大多数显卡都带有该种接口,VGA接口就是显卡上输出模拟信号的接口。

它传输红绿蓝模拟信号以及同步信号(水平和垂直信号)。VGA最早支持640*480分辨率下的16种彩色和256种灰度,或者320*240分辨率下可显示256种颜色。以后在此基础上推出更高分辨率的800*600(SVGA)或1024*768(XGA)、SXGA(1820*1024)等这些扩充的模式。这些模式仍然采用与之前一致的接口插件,即15针的梯形插头,传输模拟信号。

目前大多数计算机与外部显示设备之间的连接都是通过VGA接口(如今笔记本早已普及HDMI接口了)。计算机内部以数字的方式生成的显示图像信息,经显卡中的数字/模拟转换器(DAC)转变为R、G、B三原色信号和行、场同步信号,这些信号通过VGA接口和电缆传输到显示设备中。而如今虽说VGA标准对于个人计算机市场已经过时, 但是VGA仍然是所有制造商所支持的最低标准,例如不管哪个厂商的显卡都支持VGA标准显示。

2. VGA的硬件电路介绍

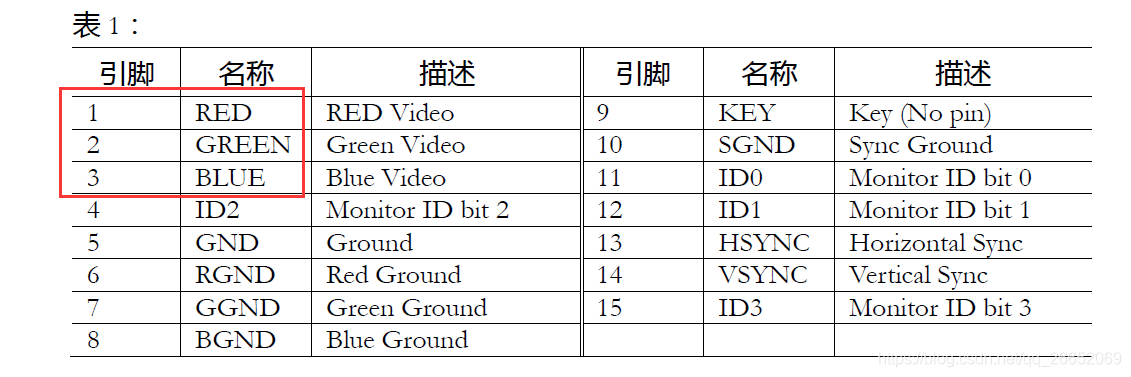

VGA接口是一种D型接口(D-SUB),上面共有三排共15pin。

实物图如下:

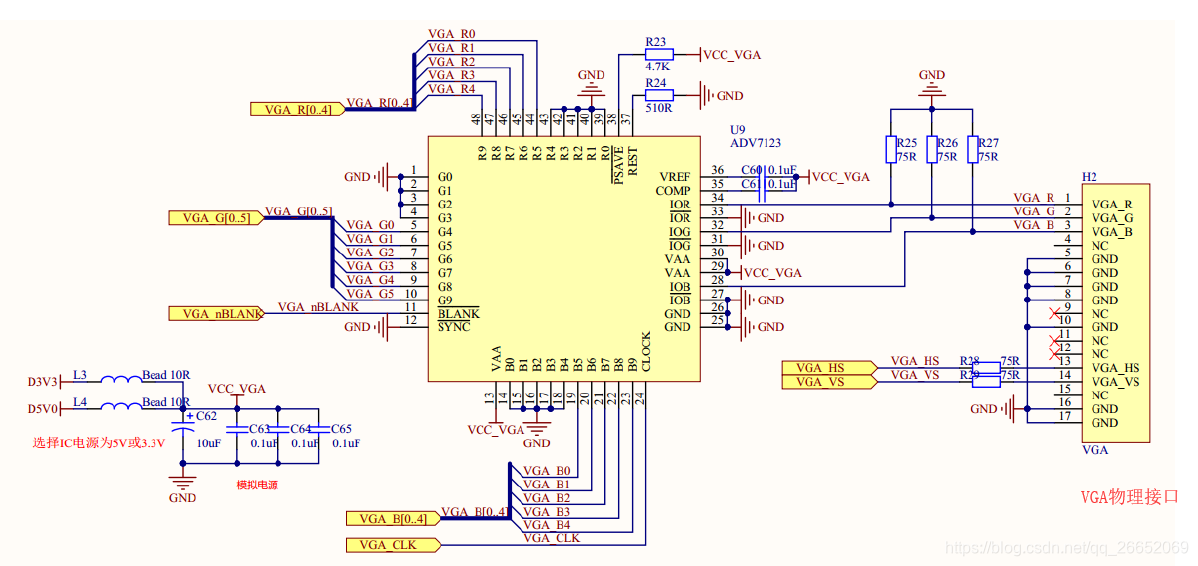

常用的专用VGA视频编码芯片有ADV/GM7123,然后通过标准的VGA物理接口输出,实现与VGA显示器通信。

下面这幅同样是ADV7123原理图,看起来更为清晰一点。但是与上面不同的是,这里的VGA显示选择了RGB565模式,R0-4,G0-5,B0-4,这样同样也节省了FPGA的引脚。

3.VGA电气特性

VGA引脚定义如下表所示

引脚1、2、3分别代表红绿蓝三基色模拟电压,为0~0.714V(peak-peak),0V代表无色,0.714V代表满色。一些非标准显示器使用1Vppd 满色电平。

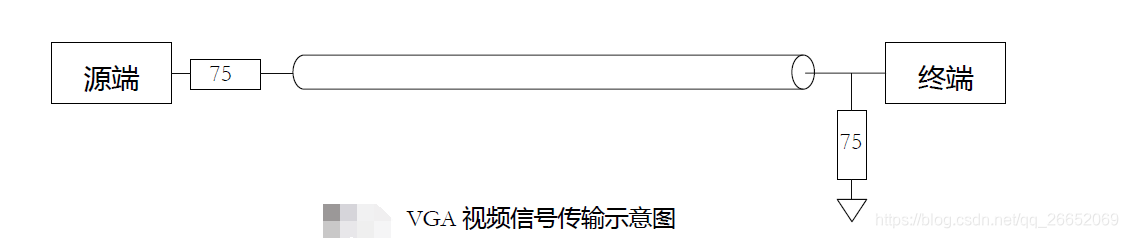

三基色源端及终端匹配电阻均为75欧姆,下如所示。

HSYNC 和VSYNC分别为行数据同步与帧数据同步,为TTL电平。

4. VGA接口信号

ADV7123硬件电路中,与FPGA开发板相连的接口信号共29个。ADV7123的输入接FPGA的VGA控制器,即由FPGA控制器提供:

| 信号名 | 描述 |

| HS | 行同步信号 |

| VS | 场同步信号 |

| Blank | 消隐信号 |

| VGA_CLK | VGA驱动时钟 |

| R0-7 | 红色信号 |

| G0-7 | 绿色信号 |

| B0-7 | 蓝色信号 |

大致可以分为三类:

- 恒定不变的信号(VGA_BLANK,VGA_SYNC)

- 时序控制信号(VGA_CLK,VGA_HS,VGA_VS)

- 数据信号(VGA_R0-7,VGA_G0-7,VGA_B0-7)

使用VGA显示时我们需要将VGA_BLANK默认置1,VGA_SYNC默认置0。VGA_CLK是VGA显示的主时钟,它的频率决定了VGA显示的分辨率(也就是说VGA主频大小与分辨率挂钩)。

VGA_HS是VGA的水平同步信号,它决定了VGA显示的宽度。VGA_VS是VGA的垂直同步信号,它决定了VGA显示的高度。数据信号中R、G、B三种颜色的小大都是8位,所以这个VGA模块显示的颜色深度为24位,也就是说VGA显示的是24位真彩色,显示的质量非常高。

VGA显示的分辨率、宽度和高度。我们需要知道,VGA也是一个视频传输标准,所以VGA的分辨率也就是视频的分辨率。VGA视频标准有很多种,每个制造商似乎都在其监视器手册中列出了不同的时序,通过查看视频格式手册可以知道VGA的分辨率有哪些。

5. VGA时序

分为 行数据时序和帧(场)数据时序 :

显示一行数据需要处理两件事:产生行同步信号HSYNC;产生显示的数据信号。

行同步是周期性脉冲信号,周期就是一行的时间e=a+b+c+d,因分辨率不同而有所差异; 而数据信号为模拟信号,当在显示有效数据(Active video)内,DATA信号为0-0.174Vpp的模拟电压(R、G、B)。

VGA需要的是模拟信号,而FPGA提供 的是数字信号,因此还需要专用的DAC芯片进行数模转换。很多开发板为了节省成本,会选择用电阻网络R-2R作为视频DAC(黑金AX309开发板就是如此)。

帧同步与行同步同理可得。

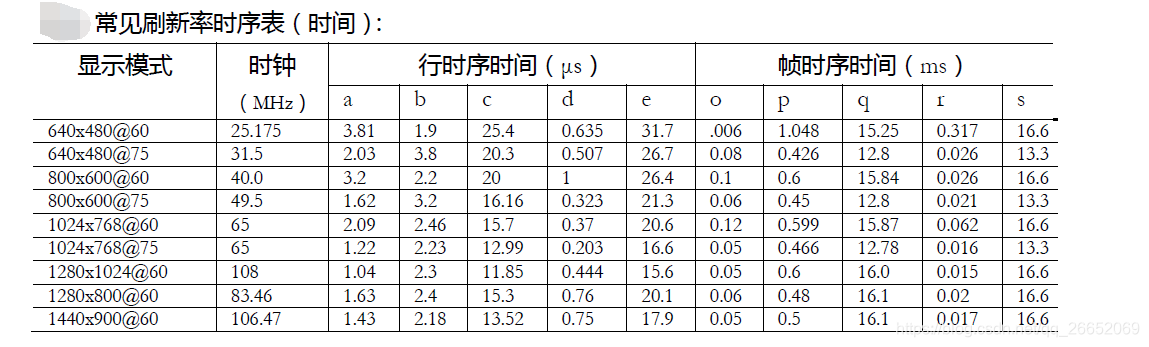

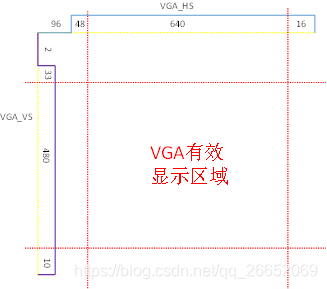

选择一个最常见的分辨率640*480p@60Hz,这里的640、480表示水平和垂直方向的像素点个数,也就表示VGA输出了一个60Hz的640*480的视频信号。把行时序与帧(场)时序合起来看:

VGA_HS(HSYNC):信号是一个周期信号,在一个周期内,VGA_HS的低电平时间为96个VGA_CLK信号周期,高电平时间为704个VGA_CLK信号周期。VGA的数据信号在VGA_HS高电平的第49个VGA_CLK信号周期开始有效,一直持续到VGA_HS高电平的第688个VGA_CLK信号周期。

其中,96个Hsync脉冲低电平:Sync_pulse = 96;704个周期的Hsync的高电平由分为:Front Porch= 16周期,和BackFront Porch =48周期,剩余的704-16-48=640即为一行的有效数据周期(一个像素周期传送一个像素)。

VGA_VS(VSYNC)信号也是一个周期信号,在一个周期内,VGA_VS的低电平时间为2个VGA_HS信号周期,高电平时间为523个VGA_HS信号周期。VGA的数据信号在VGA_VS高电平的第34个VGA_HS信号周期开始有效,一直持续到高电平的第513个VGA_HS信号周期。为了更直观的表达这一时序,我们用下面这个图表示。

VGA的显示时序就是一个逐行扫描的过程,每完成一个行扫描(即VGA_HS信号经过一个周期),则开始扫描下一行。只有当VGA_HS和VGA_VS同时有效,VGA数据信号才有效。

VGA时钟计算

上节提到,VGA驱动时钟与图像显示的分辨率和帧率有关,那么如何计算呢?对于640*480@60即一帧图像的分辨率为640*480,每秒60的频率帧刷新,则一帧的传输的全部像素个数为800*525(注意分辨率640*480指的是有效显示数据的分辨率,而计算时候需要用全分辨率)个,一秒刷新的像素个数为640*480*60,而一个像素就需要一个耗时像素时钟周期传输,因此可得出该标准下VGA_CLK=640*480*60。

于是可总结出:VGA_CLK=HS_total×VS_total×FPS。

其中,HS_total为VGA_HS信号的一个行周期内包含的VGA_CLK信号周期个数,VS_total为VGA_VS信号的一个场周期内包含的VGA_HS信号周期个数,FPS为帧率,分辨率640*480p@60Hz时,HS_total为800,VS_total为525。

因此VGA_CLK信号的频率为800×525×60Hz=25.2MHz。

![[转]ADAS各功能模块及ADAS解决方案提供商详解](https://img-blog.csdn.net/2018091114263348?watermark/2/text/aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3dlaXhpbl80MjIyOTQwNA==/font/5a6L5L2T/fontsize/400/fill/I0JBQkFCMA==/dissolve/70)