第一讲 Cortex-M3介绍及使用场景

一、Cortex-M3介绍

Cortex-M3内核是MCU的中央处理器单元, Cortex-M3内核通过接口总线的形式挂载了储存器、外设、中断等组成一个MCU:

CM3的主要特点包括:

• 性能强劲

• 功耗低

• 实时性好

• 代码密度高

• 使用更方便

• 低成本的整体解决方案

• 遍地开花的优秀开发工具

二、Cortex-M3 使用场景

高性能+高代码密度+小硅片面积,3璧合一,使得CM3大面积地成为理想的处理平台,主要应用范围:

- 低成本单片机:CM3与生俱来就适合做单片机,甚至简单到用于做玩具和小电器的单片机,都能使用CM3作为内核。这里本是8位机和16位机统治最牢固的腹地,但是CM3更便宜,更高性能,更易使用,所以值得开发者们转到这个新生的ARM32位系统中来。

- 汽车电子:CM3同时拥有非常高的性能和极低的中断延迟,打入实时领域的大门。CM3处理器能支持多达240个外部中断,内建了嵌套向量中断控制器,还可以选择配上一个存储器保护单元(MPU)。所有这些,使它用于高集成度低成本的汽车应用最合适不过了。

- 数据通信:CM3的低成本+高效率,再加上Thumb-2的强大位操作指令s,使CM3非常理想地适合于很多数据通信应用,尤其是无线数传和Ad-Hoc网络,如ZigBee和蓝牙等。

- 工业控制:在工控场合,关键的要素在于简洁、快速响应以及可靠。再一次地,CM3处理器的中断处理能力,低中断延迟,强化的故障处理能力(fault-handing),足以让它能昂首挺胸地踏入这片热土。

- 消费类产品:以往,在许多消费产品中,都必须使用一块甚至好几块高性能的微处理器。别看CM3只是个小处理器,它的高性能和MPU机制可是足以让复杂的软件跑起来的,同时提供健壮的存储器保护。目前在市场上已经有了好多基于Cortex-M3内核的处理器产品,最便宜的还不到1美元,让ARM终于比很多8位机还便宜了。

第二讲 ARM架构

一 、Cortex M3内核概述

- Cortex M3 Vendor-ARM介绍

- Cortex M3处理器整体架构

- Cortex M3处理器内核特性

- Cortex N3嵌套向量中断

- Cortex N3MPU保护单元

- Cortex M3总线接口

- Cortex N3低成本调试接口

1. Cortex M3 Vendor-ARM介绍

- 摩托罗拉很贵,ARM公司就借助精简指令集,后来和苹果、Acorn和LSI三家公司成立了Advance RSIC Machine公司,不生产芯片!

- 与X86相比,功耗很低!

- 用它的时候,要给两次钱,买这个vip时候要付费,流片成功使用的时候要付费!

2. Cortex M3处理器整体架构

译码控制、向量中断控制

核采用的是指数和数据并行执行,流水操作得以实现

MPU保护单元:做一些地址单元的逻辑保护,防止内存踩踏,黑客就是来搞这个,给跑废

3. Cortex M3处理器内核特性

两种指令集:Tvmb(16位)和ARM32(32位),Thumb-2都支持这两种指令集

三级流水

指令和数据并发

堆栈隔离

兼容v6

4. Cortex N3嵌套向量中断

动态优先级改变

摇尾操作!

处理器自动保存

5. Cortex N3MPU保护单元

8块内存区域,设置,只读

6. Cortex M3总线接口

7. Cortex N3低成本调试接口

通过AHB-AP

支持两类调试:SW、JTAG(调试速度快,管脚多)

二 、Cortex M3-CODE

- Cortex M3内核架构

- Cortex M3处理器内核-寄存器

- Cortex M3处理器内核指令预取

- Cortex M3处理器内核-流水技术

- Cortex M3处理器内核- Interface

1. Cortex M3内核架构

FETCH:取指单元

DEC:指令译码

EXEU:运行

处理流水由上面三个单独操作

ALU+REG_BANK

LSU:内存取数

EMT_INTF:加速访问

STATUS:状态上报

PMU:数据流,可以不要

2. Cortex M3处理器内核-寄存器

3. Cortex M3处理器内核-指令预取

4. Cortex M3处理器内核-流水技术

5. Cortex M3处理器内核-Interface

注意地址的对应

三、 Cortex-M3 NVIC

- Cortex M3 NVIC概述

- Cortex M3 中断 Enable与 Clear

- Cortex V3 中断 Priority

- Cortex N3 中断 Pending与 Depending

- Cortex M3 Systick定时器

1. Cortex M3 NVIC概述

IRQs可以屏蔽的

2. Cortex M3 中断 Enable与 Clear

- Enable与 Clear独立寄存器控制

- 每个中断对应一个 Enable和 Clear寄存器

- 1~240分别映射到8对32bits寄存器

- Enable和 Clear按照写1清方式完成使能和清除

- 异常号16+n

- SETENAS:xEO00E100-0XE00OE11C(1C/4+1)*32=256(与下面之间预留了,为了扩展)

- CLRENAS: 0XE000E180-OXE000 E19C((1C/4+1)*32=256

3. Cortex V3 中断 Priority

4. Cortex N3 中断 Pending与 Depending

5. Cortex M3 Systick定时器

处理器最少有一个timer

三、Cortex-M3 中断机制

- Cortex N3中断响应行为

- Cortex M3中断退出行为

- Cortex M3中断嵌套

- Cortex M3咬尾中断

- Cortex M3中断延迟

- Cortex M3中断响应的Faut处理

1. Cortex N3中断响应行为

2. Cortex M3中断退出行为

3. Cortex M3中断嵌套

4. Cortex M3咬尾中断

5. Cortex M3中断延迟

6. Cortex M3中断响应的Faut处理

五、MCU Memory Map

- Cortex M3 Memory Map Overview

- Cortex M3 Memory Region Permissions

- Cortex M3 Bit-banding

- Cortex M3 ROM Memory Table

1. Cortex M3 Memory Map Overview

2. Cortex M3 Memory Region Permissions

3. Cortex M3 Bit-banding

一个地址对应的是8bit,就是一个byte。加了alias映射后,7bit对应的是2200001c的地址,每一个bit对应一个地址,操作时方便很多,只需要处理映射地址的最低位!

以前修改一个bit,需要先把那个byte全部读出来,然后再屏蔽其他位,再进行写入!

4. Cortex M3 ROM Memory Table

六、Cortex M3-时钟与复位

- Cortex M3 Clocking

- Cortex M3 Resets

- Cortex M3 Resets Mode

- Cortex M3 Reset Diagram

- Cortex M3 Power Control

1. Cortex M3 Clocking

FCLK:要一直存在!

2. Cortex M3 Resets

3. Cortex M3 Resets Mode

4. Cortex M3 Reset Diagram

5. Cortex M3 Power Control

七、Cortex M3-Debug System

- Cortex M3 System Debug Access Overview

- Cortex M3 System debug architecture

- Cortex M3 FPB

- Cortex M3 DWT

- Cortex M3 TM

- Cortex M3 AHB-AP

- Cortex M3 TPIU

1. Cortex M3 System Debug Access Overview

2. Cortex M3 System debug architecture

可以挂多个ap,基本上可以访问所有空间,但是dft应该会单独做一个ap

3. Cortex M3 FPB

代码区:flash存放,

如果flash有坏的,打补丁,映射到RAM

4. Cortex M3 DWT

5. Cortex M3 TM

6. Cortex M3 AHB-AP

7. Cortex M3 TPIU

第三讲 MCU芯片存储系统

一、MCU芯片存储系统-ROM

1.MCU存储系统ROM概述

2.MCU存储系统ROM基本原理

3.MCU存储系统ROM分类

4.MCU存储系統ROM生成

5.MCU存储系统ROM集成

1.MCU存储系统ROM概述

只读存储器,非易失性,不容改变,

2.MCU存储系统ROM基本原理

简单的rtl就可以完成一个简单的rom

1024x32一般都是基本单元

3.MCU存储系统ROM分类

东芝1984年发明了flash,工业界用的要么是ROM和flash,前者简单,面积小;重点用的是flash

4.MCU存储系統ROM生成

两种启动方式,GUI和命令行,其实感觉quartus II也可以生成这些东西!

GUI一次只会生成一个,脚本一次可以生成很多,看需求!

可以生成需要用的文件,验证的时候做验证模型,综合用的文件等

5.MCU存储系统ROM集成

-

Interface

Basic可以配置这ROM,cpu一开始就是来读它的,所以它之前就配置好的

CEN是片选 -

Basic Function

- Test Function

- EMA

- Power Gating

二、MCU芯片存储系统-Flash

1.MCU存储系统 Flash基本原理

2.MCU存储系统Flash种类

3.MCU存储系统Fash时序(复用和非复用)

1.MCU存储系统 Flash基本原理

非易失性:掉电也不会影响

2.MCU存储系统flash种类

NAND 按块进行访问的,NOR按位进行访问的

3.MCU存储系统Flash时序(复用和非复用)

- Flash时序(NOR)

一般集成在MCU中,只有几十K,MCU中地址与数据分离的作用不大!

三、MCU芯片存储系统-SRAM

1.MCU存储系统- SRAM Concept

2.MCU存储系统- SRAM Orgnization

3.MCU存储系统- SRAM Type

4.MCU存储系统- SRAM Interface

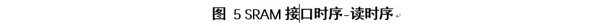

5.MCU存储系统- SRAM Timing

6.MCU存储系统- SRAM Generation

1.MCU存储系统- SRAM Concept

只要有电,就存下来了,由于面积比较大,内部用的就是这个,速度比较快

FIFO比较大的话就用sram

2.MCU存储系统- SRAM Orgnization

典型的sram使用6个晶体管构成,来寄存一个bit的数据!

1024X4,可能会摆成512x8的阵列,把形状尽量做成正方形,便于后端摆放

3.MCU存储系统- SRAM Type

SP单端读写端口:不能同时读写,不会有读写冲突,尽量不要有先读后写,或者先初始化,防止出错!

DP双端读写端口:速度快,MCU中很少用,用两个SRAM做乒乓操作

一般是通过地址查找内容,但是也有通过内容查找地址,如路由器(CAM)!

4.MCU存储系统- SRAM Interface

5.MCU存储系统- SRAM Timing

一个时钟周期

6.MCU存储系统- SRAM Generation

第四讲 AMBA总线

一、AMBA总线-APB

1.MCU总线系统APB2.0总线协议

2.MCU总线系统APB3.0总线协议

3.MCU总线系统APB私有扩展

1.MCU总线系统APB2.0总线协议

AMBA 2.0用在低功耗,挂的是低速的外设,一般用的是时钟的上沿

没有三态,协议也比较简单

PSELx是选择UART、Keypad、Timer等的,采用广播方式,访问地址是统一排放的!

- write transfer

PSEL为低时,应该保持的,减少翻转 - Read transfer

其实读的时候可以一拍完成?

2.MCU总线系统APB3.0总线协议

与2.0相比,增加了PREADY和PSLVERR两个信号!

如果ready为高,和2.0一样也是两拍完成!

3.MCU总线系统APB私有扩展

通过指示,那些地址是有效的,与AXI等保持一致!

一般都是自己写代码,没有工具生成代码!

二、AMBA总线-AHB

AHB is a new generation of AMBA bus which is intended to address the requirements of high-performance synthesizable designs. AMBA AHB is a new level of bus which sits above the APB and implements the features required for high-performance, high clock frequency systems including:

• burst transfers

• split transactions

• single cycle bus master handover

• single clock edge operation

• non-tristate implementation

• wider data bus configurations (64/128 bits).

APB没有流水操作,AHB就是通过添加这个来完成的!

只有等上一个transfer完毕后,才会仲裁下一个!

burst就是连续访问的16个byte(0、4、8、C、10、14、18、1C、、、),连续触发!提出这个burst但是没怎么用!

因为仲裁的原因,超长的仲裁周期,在公司中基本上不用AHB的burst,而AXI这里做好了!

实际应用中,NONSEQ和SEQ是一个东西,没什么区别!(实际经验)

一般都是slave来采用,master不会采用!

HSELx中x代表slave的个数!

RETRY在工程上基本上不会使用!

SPLIT和RETRY基本上不使用!

三、MCU总线系统-AHB2APB总线桥

1.MCU总线系统AHB2APB总线桥作用

2.MCU总线系统AHB2APB总线桥实现状态机

3.MCU总线系统AHB2APB总线桥RTL代码实现解析

1.MCU总线系统AHB2APB总线桥作用

2.MCU总线系统AHB2APB总线桥实现状态机

3.MCU总线系统AHB2APB总线桥RTL代码实现解析

//cmsdk_ahb_to_apb.v

module cmsdk_ahb_to_apb #(// Parameter to define address width// 16 = 2^16 = 64KB APB address spaceparameter ADDRWIDTH = 16,parameter REGISTER_RDATA = 1,parameter REGISTER_WDATA = 0)(

// --------------------------------------------------------------------------

// Port Definitions

// --------------------------------------------------------------------------input wire HCLK, // Clockinput wire HRESETn, // Resetinput wire PCLKEN, // APB clock enable signalinput wire HSEL, // Device selectinput wire [ADDRWIDTH-1:0] HADDR, // Addressinput wire [1:0] HTRANS, // Transfer controlinput wire [2:0] HSIZE, // Transfer sizeinput wire [3:0] HPROT, // Protection controlinput wire HWRITE, // Write controlinput wire HREADY, // Transfer phase doneinput wire [31:0] HWDATA, // Write dataoutput reg HREADYOUT, // Device readyoutput wire [31:0] HRDATA, // Read data outputoutput wire HRESP, // Device response// APB Outputoutput wire [ADDRWIDTH-1:0] PADDR, // APB Addressoutput wire PENABLE, // APB Enableoutput wire PWRITE, // APB Writeoutput wire [3:0] PSTRB, // APB Byte Strobeoutput wire [2:0] PPROT, // APB Protoutput wire [31:0] PWDATA, // APB write dataoutput wire PSEL, // APB Selectoutput wire APBACTIVE, // APB bus is active, for clock gating// of APB bus// APB Inputinput wire [31:0] PRDATA, // Read data for each APB slaveinput wire PREADY, // Ready for each APB slaveinput wire PSLVERR); // Error state for each APB slave// --------------------------------------------------------------------------// Internal wires// --------------------------------------------------------------------------reg [ADDRWIDTH-3:0] addr_reg; // Address sample registerreg wr_reg; // Write control sample registerreg [2:0] state_reg; // State for finite state machinereg [3:0] pstrb_reg; // Byte lane strobe registerwire [3:0] pstrb_nxt; // Byte lane strobe next statereg [1:0] pprot_reg; // PPROT registerwire [1:0] pprot_nxt; // PPROT register next statewire apb_select; // APB bridge is selectedwire apb_tran_end; // Transfer is completed on APBreg [2:0] next_state; // Next state for finite state machinereg [31:0] rwdata_reg; // Read/Write data sample registerwire reg_rdata_cfg; // REGISTER_RDATA paramaterwire reg_wdata_cfg; // REGISTER_WDATA paramaterreg sample_wdata_reg; // Control signal to sample HWDATA// -------------------------------------------------------------------------// State machine// -------------------------------------------------------------------------localparam ST_BITS = 3;localparam [ST_BITS-1:0] ST_IDLE = 3'b000; // Idle waiting for transactionlocalparam [ST_BITS-1:0] ST_APB_WAIT = 3'b001; // Wait APB transferlocalparam [ST_BITS-1:0] ST_APB_TRNF = 3'b010; // Start APB transferlocalparam [ST_BITS-1:0] ST_APB_TRNF2 = 3'b011; // Second APB transfer cyclelocalparam [ST_BITS-1:0] ST_APB_ENDOK = 3'b100; // Ending cycle for OKAYlocalparam [ST_BITS-1:0] ST_APB_ERR1 = 3'b101; // First cycle for Error responselocalparam [ST_BITS-1:0] ST_APB_ERR2 = 3'b110; // Second cycle for Error responselocalparam [ST_BITS-1:0] ST_ILLEGAL = 3'b111; // Illegal state// --------------------------------------------------------------------------// Start of main code// --------------------------------------------------------------------------// Configuration signalassign reg_rdata_cfg = (REGISTER_RDATA==0) ? 1'b0 : 1'b1;assign reg_wdata_cfg = (REGISTER_WDATA==0) ? 1'b0 : 1'b1;// Generate APB bridge selectassign apb_select = HSEL & HTRANS[1] & HREADY;// Generate APB transfer endedassign apb_tran_end = (state_reg==3'b011) & PREADY;assign pprot_nxt[0] = HPROT[1]; // (0) Normal, (1) Privilegedassign pprot_nxt[1] = ~HPROT[0]; // (0) Data, (1) Instruction// Byte strobe generation// - Only enable for write operations// - For word write transfers (HSIZE[1]=1), all byte strobes are 1// - For hword write transfers (HSIZE[0]=1), check HADDR[1]// - For byte write transfers, check HADDR[1:0]assign pstrb_nxt[0] = HWRITE & ((HSIZE[1])|((HSIZE[0])&(~HADDR[1]))|(HADDR[1:0]==2'b00));assign pstrb_nxt[1] = HWRITE & ((HSIZE[1])|((HSIZE[0])&(~HADDR[1]))|(HADDR[1:0]==2'b01));assign pstrb_nxt[2] = HWRITE & ((HSIZE[1])|((HSIZE[0])&( HADDR[1]))|(HADDR[1:0]==2'b10));assign pstrb_nxt[3] = HWRITE & ((HSIZE[1])|((HSIZE[0])&( HADDR[1]))|(HADDR[1:0]==2'b11));// Sample control signalsalways @(posedge HCLK or negedge HRESETn)beginif (~HRESETn)beginaddr_reg <= {(ADDRWIDTH-2){1'b0}};wr_reg <= 1'b0;pprot_reg <= {2{1'b0}};pstrb_reg <= {4{1'b0}};endelse if (apb_select) // Capture transfer information at the end of AHB address phasebeginaddr_reg <= HADDR[ADDRWIDTH-1:2];wr_reg <= HWRITE;pprot_reg <= pprot_nxt;pstrb_reg <= pstrb_nxt;endend// Sample write data control signal// Assert after write address phase, deassert after PCLKEN=1wire sample_wdata_set = apb_select & HWRITE & reg_wdata_cfg;wire sample_wdata_clr = sample_wdata_reg & PCLKEN;always @(posedge HCLK or negedge HRESETn)beginif (~HRESETn)sample_wdata_reg <= 1'b0;else if (sample_wdata_set | sample_wdata_clr)sample_wdata_reg <= sample_wdata_set;end// Generate next state for FSM// Note : case 3'b111 is not used. The design has been checked that// this illegal state cannot be entered using formal verification.always @(state_reg or PREADY or PSLVERR or apb_select or reg_rdata_cfg orPCLKEN or reg_wdata_cfg or HWRITE)begincase (state_reg)// IdleST_IDLE :beginif (PCLKEN & apb_select & ~(reg_wdata_cfg & HWRITE))next_state = ST_APB_TRNF; // Start APB transfer in next cycleelse if (apb_select)next_state = ST_APB_WAIT; // Wait for start of APB transfer at PCLKEN highelsenext_state = ST_IDLE; // Remain idleend// Transfer announced on AHB, but PCLKEN was low, so waitingST_APB_WAIT :beginif (PCLKEN)next_state = ST_APB_TRNF; // Start APB transfer in next cycleelsenext_state = ST_APB_WAIT; // Wait for start of APB transfer at PCLKEN highend// First APB transfer cycleST_APB_TRNF :beginif (PCLKEN)next_state = ST_APB_TRNF2; // Change to second cycle of APB transferelsenext_state = ST_APB_TRNF; // Change to state-2end// Second APB transfer cycleST_APB_TRNF2 :beginif (PREADY & PSLVERR & PCLKEN) // Error received - Generate two cycle// Error response on AHB bynext_state = ST_APB_ERR1; // Changing to state-5 and 6else if (PREADY & (~PSLVERR) & PCLKEN) // Okay receivedbeginif (reg_rdata_cfg)// Registered versionnext_state = ST_APB_ENDOK; // Generate okay response in state 4else// Non-registered versionnext_state = {2'b00, apb_select}; // Terminate transferendelse // Slave not readynext_state = ST_APB_TRNF2; // Unchangeend// Ending cycle for OKAY (registered response)ST_APB_ENDOK :beginif (PCLKEN & apb_select & ~(reg_wdata_cfg & HWRITE))next_state = ST_APB_TRNF; // Start APB transfer in next cycleelse if (apb_select)next_state = ST_APB_WAIT; // Wait for start of APB transfer at PCLKEN highelsenext_state = ST_IDLE; // Remain idleend// First cycle for Error responseST_APB_ERR1 : next_state = ST_APB_ERR2; // Goto 2nd cycle of error response// Second cycle for Error responseST_APB_ERR2 :beginif (PCLKEN & apb_select & ~(reg_wdata_cfg & HWRITE))next_state = ST_APB_TRNF; // Start APB transfer in next cycleelse if (apb_select)next_state = ST_APB_WAIT; // Wait for start of APB transfer at PCLKEN highelsenext_state = ST_IDLE; // Remain idleenddefault : // Not usednext_state = 3'bxxx; // X-Propagationendcaseend// Registering state machinealways @(posedge HCLK or negedge HRESETn)beginif (~HRESETn)state_reg <= 3'b000;elsestate_reg <= next_state;end// Sample PRDATA or HWDATAalways @(posedge HCLK or negedge HRESETn)beginif (~HRESETn)rwdata_reg <= {32{1'b0}};elseif (sample_wdata_reg & reg_wdata_cfg & PCLKEN)rwdata_reg <= HWDATA;else if (apb_tran_end & reg_rdata_cfg & PCLKEN)rwdata_reg <= PRDATA;end// Connect outputs to top levelassign PADDR = {addr_reg, 2'b00}; // from sample registerassign PWRITE = wr_reg; // from sample register// From sample register or from HWDATA directlyassign PWDATA = (reg_wdata_cfg) ? rwdata_reg : HWDATA;assign PSEL = (state_reg==ST_APB_TRNF) | (state_reg==ST_APB_TRNF2);assign PENABLE = (state_reg==ST_APB_TRNF2);assign PPROT = {pprot_reg[1], 1'b0, pprot_reg[0]};assign PSTRB = pstrb_reg[3:0];// Generate HREADYOUTalways @(state_reg or reg_rdata_cfg or PREADY or PSLVERR or PCLKEN)begincase (state_reg)ST_IDLE : HREADYOUT = 1'b1; // IdleST_APB_WAIT : HREADYOUT = 1'b0; // Transfer announced on AHB, but PCLKEN was low, so waitingST_APB_TRNF : HREADYOUT = 1'b0; // First APB transfer cycle// Second APB transfer cycle:// if Non-registered feedback version, and APB transfer completed without error// Then response with ready immediately. If registered feedback version,// wait until state_reg==ST_APB_ENDOKST_APB_TRNF2 : HREADYOUT = (~reg_rdata_cfg) & PREADY & (~PSLVERR) & PCLKEN;ST_APB_ENDOK : HREADYOUT = reg_rdata_cfg; // Ending cycle for OKAY (registered response only)ST_APB_ERR1 : HREADYOUT = 1'b0; // First cycle for Error responseST_APB_ERR2 : HREADYOUT = 1'b1; // Second cycle for Error responsedefault: HREADYOUT = 1'bx; // x propagation (note :3'b111 is illegal state)endcaseend// From sample register or from PRDATA directlyassign HRDATA = (reg_rdata_cfg) ? rwdata_reg : PRDATA;assign HRESP = (state_reg==ST_APB_ERR1) | (state_reg==ST_APB_ERR2);assign APBACTIVE = (HSEL & HTRANS[1]) | (|state_reg);endmodule

第五讲 MCU外设系统-IO

一、MCU典型外设-UART应用和作用

- UART Concept

- UART Data Framing

- UART Receiver

- UART transmitter

- UART special transceiver conditions

1. UART Concept

全双工,点对点传输,一个master对应一个slave

2. UART Data Framing

3. UART Receiver

4. UART transmitter

5. UART special transceiver conditions

二、MCU典型外设-UART电路设计

- UART architecture

- UART register configuration

- UART Receiver

- UART transmitter

- UART special transceiver conditions

1. UART architecture

2. UART register configuration

3. UART Receiver

4. UART transmitter

5. UART special transceiver conditions

三、MCU典型外设-UART RTL代码编写

配置寄存器、

先略,如有需要,再来补充学习!

四、MCU典型外设-I2C应用和作用

- 12C Concept

- 12C Application

- 12C Revision

- 12C Design

- 12C Message protocols

- Timing

1. 12C Concept

终于知道 I方C 的来源了

多master和多slave,而uart是单master单slave

串行接口:需要做串并转换,传输距离比较短

飞利浦->NXP,现在也四分五裂了

2. 12C Application

cpu外围低速度设备控制

3. 12C Revision

4. 12C Design

5. 12C Message protocols

6. Timing

五、MCU典型外设-I2C电路设计

- I2C设计架构

- 12C设计PAD

- I2C寄存器配置

1. I2C设计架构

2. 12C设计PAD

双向pad

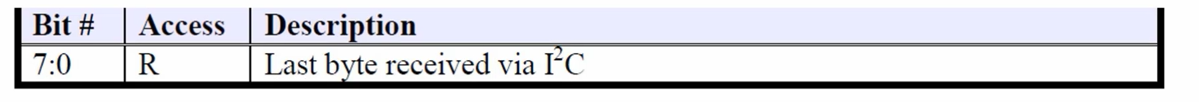

3. I2C寄存器配置

- control register

- Transmitter

- receiver

- status

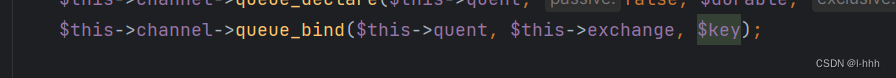

六、MCU典型外设-I2C RTL代码编写

略,如有需要,再来补充学习!

七、MCU典型外设-SPI应用和作用

- Spl Concept

- SPI Interface

- SPI Clock Polarity and Phase

- SPI Topology Independent slave configuration

- SPI Advantages

- SPI Disadvantages

- SPI Variant

1. Spl Concept

- A synchronous serial communication interface

- Used for short distance communication, primarily in embedded systems

- Developed by Motorola in the mid 1980s

- Communicate in full duplex mode using a single master multiple slave architecture

- The master originates the frame for reading and writing

- Multiple slave devices are supported through individual slave select(SS)lines

2. SPI Interface

3. SPI Clock Polarity and Phase

4. SPI Topology Independent slave configuration

5. SPI Advantages

6. SPI Disadvantages

- Requires more pins on IC packages than PC, even in the three-wire variant

- No in-band addressing; out-of-band chip select signals are required on shared buses

- No hardware flow control by the slave

- No hardware slave acknowledgment

- Typically supports only one master device

- No error-checking protocol is defined

- Only handles short distances compared to RS-232, RS-485, or Can-bus

- Many existing variations

7. SPI Variant

Three wire serial bus

- Uses single bidirectional data line(SSO)instead of two lines(Mosl and MISO)

- Restricted to a half duplex mode

- Used for lower performance parts such as small EEPROMS sensors and Microwire

Dual SPI: A half-duplex configuration to send two bits per clock cycle

- The Mosl line becomes SIO0 and carries even bits

- The MISO line becomes Slo1 and carries odd bits

- Data is still transmitted msbit-first

Slo1 carries bits 7, 5, 3 and 1 of each byte

八、MCU典型外设-SPI电路设计

- SPI架构

- SPI寄存器

1. SPI架构

SPCR、SPER、SPSR是寄存器,写寄存器用来配置内部,读内存器是用来了解内部工作状态

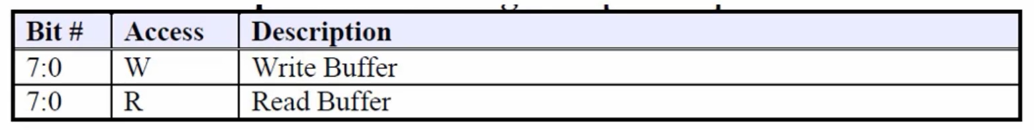

2. SPI寄存器

- 配置寄存器

- 控制寄存器

- 状态寄存器

- 数据寄存器

- SPI寄存器

九、MCU典型外设-SPI RTL代码编写

先略,如有需要,再来补充学习!

第六讲 外设系统-内部控制单元

一、MCU典型外设-WDT应用和作用

- WDT Concept

- WDT Restart

- WDT Reset

1. WDT Concept

Watch Dog Timer 看门狗,没有人来喂狗的话,cpu就会挂死(不停的复位?)

2. WDT Restart

相当于喂狗,在cpu外面,不断地给它东西,MCU在内部给指令就行

3. WDT Reset

二、 MCU典型外设-WDT电路设计

- WDT 架构

- WDT 寄存器

1. WDT 架构

Free Running Countering,自动减一

2. WDT 寄存器

如果复位值太小,就会不断的复位!

- WDT Load & Control

- WDT INT

原始中断raw watching interrupt

上报中断watching interrupt

中断一般包括三部分:中断使能/mask、原始中断、中断上报

三、 MCU典型外设- WDT RTL编码

先略,如有需要,再来补充学习!

四、 MCU典型外设- Timer应用和作用

- Timer Concept

- Timer Application

1. Timer Concept

特别的时间间隔,记住的是相对时间,不是绝对时间

加1的、减1的

有硬件的、有软件的timer,软件的计数不精准,硬件计数特别精准,硬件不会耗费cpu指令

2. Timer Application

- Time slot for OS

- WDT

- Counter for software

与WDT相似,有减1的计数器,计数完成,产生中断

五、 MCU典型外设- Timer电路设计

- Timer设计

- Timer寄存器

1. Timer架构设计

2. Timer寄存器

- Timer Configuration

六、 MCU典型外设- Timer RTL编码

先略,如有需要,再来补充学习!

apb口和内部、外部中断

七、 MCU典型外设-RTC应用和作用

- RTC Concept

- RTC Application

1. RTC Concept

记录的是绝对时间,存在很多产品中,显示时间都是通过这个完成的

2. RTC Application

- RTC Purpose

- RTC Power Source

独立供电 - RTC Timing

八、 MCU型外设-RTC电路设计

九、 MCU类型外设- RIC RTL编码

先略,如有需要,再来补充学习!

第七讲 ARM M3总线接口

前文提到的都是现成的ip?!!!

参考原来的文章:AHB-SRAM简单设计之架构图解

一、总线接口-AHB2SRAM设计文档编写

项目名称:MCU项目AHB2SRAM设计文档

Design Specification

作者:

修订记录:

目录、图目录、表目录

功能特性、架构描述、接口描述、接口时序、模块详细电路设计(电路原理图也可以)

1. 功能特性

- 32位 AHB Slave interface

- 支持8位、16位和32位的SRAM据读写操作

- 支持低功耗工作(8位/16位操作)

2.架构框图

架构框图如图1所示,AHB2SRAM实现 AHB Slave接口与SRAM接口转换,AHB与SRAM均在同一个时钟域,不涉及异步处理。

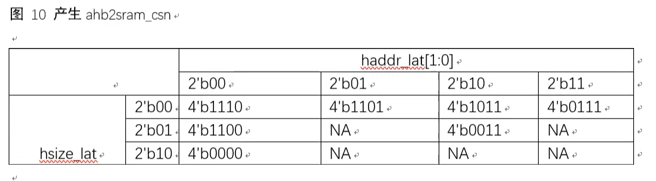

考虑低功耗,SRAM通过4块8Kx8SRAM拼接,要求,进行 HALF WORD和BYTE访问时没有被访问数据单元的SRAM不打开。

大小:32kb

位宽:32bit = 4B

32/4=8KB x 4B

8092 x 32(宽度是32,深度是8092),为了低功耗,把它分成了8K x 8的,不用的时候将其关闭

3. 接口描述

还可以描述的更详细

4.接口时序

5.模块详细电路设计

Timedesign画时序图,很多破解版

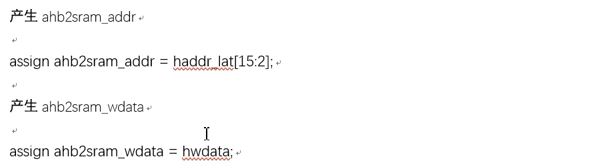

AHB地址阶段,完成对于命令解析,产生对应SRAM写的CS信号,并延后一拍与写数据对齐,写地址延后一拍 haddr_1d与数据 iwata对齐

尽可能做到一个图产生一个信号!

二、总线接口-AHB2SRAM RTL电路编码

先略,如有需要,再来补充学习!

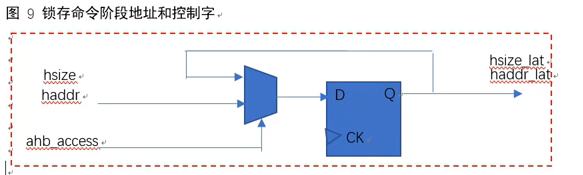

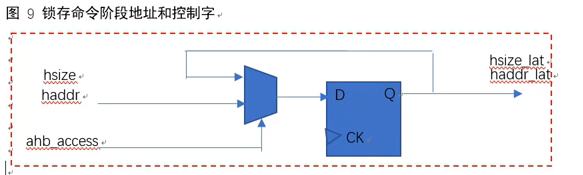

//锁存对应的电路?不是锁存器吧!

always@(posedge hclk or negedge hrst_n)beginif(hrst_n == 1'b0) beginhsize_lat <= {1{1'b0}};haddr_lat <= {HADDR_WIDTH{1'b0}};endelse if(ahb_access == 1'b1)beginhsize_lat <= hsize;haddr_lat <= haddr;end

end

三、总线接口-AHB2SRAM 实践练习

参考原来的文章:AHB-SRAM简单设计之架构图解

第八讲 ARM M3 TOP设计

一、MCU CRG设计-时钟设计

- 时钟设计需求

- 时钟设计要点

- 时钟设计电硌结构

1. 时钟设计需求

- 生成AHB时钟,APB时钟,RTC时钟

- AHB最高时钟频率为98MHz

- APB时钟为AHB同步时钟,且可以配置AHB时钟的1/2,1/4,1/8

- RTC时钟单独控制时钟,时钟频率1KHz

- 各外设时钟可以单独门控,满足低功耗要求

2. 时钟设计要点

- DFT可控,在DFT模式,可有DFT工程师插入DFT时钟

- DFT隔离,在DFT模式,SCAN描述不影响时钟的稳定产生

- DFT观测,内部时钟可输出

- 上电工作外部参考时钟,PLL稳定后,时钟自动切换

- 低功耗要求,在系统不工作时,时钟自动关闭

- 低功耗要求,各个外设时钟均能门控

3. 时钟设计电路结构

PLL锁相环,倍频

二、MCU CRG设计-时钟设计代码

先略,如有需要,再来补充学习!

三、MCU CRG设计-复位设计

- 复位需求

- 复位设计要点

- 复位设计电路结构

1. 复位需求

- 生成AHB时钟,APB时钟,RTC时钟于对应异步复位同步撤离时钟

- 根据WDT的中断,能够自动复位CPU(如果没有喂狗,cpu就会被reset)

- 根据系统中断,能够自动复位CPU

- 每个外设具有单独软复位

- 满足DFT可控要求

2. 复位设计要点

- 输入复位需要滤毛刺

- DFT可控,在DFT模式,可有DFT工程师插入DFT复位

- DFT隔离,在DFT模式,SCAN描述不影响复位的稳定产生

- 与时钟同步进行撇离

- WDT,系统控制中断自动复位启动和撤离

- 实现软复位

3. 复位设计电路结构

滤波、同步、软复位

DFT隔离

四、MCU CRG设计-复位设计代码

先略,如有需要,再来补充学习!

第九讲 ARM M3 TOP-系统控制器

一、MCU系统控制器设计

- 系统控制器作用

- 系统控制器-寄存器类型

- 系统控制器寄存器电路设计

1. 系统控制器作用

挂在apb下面

2. 系统控制器-寄存器类型

- RW可读可写

- RO只读

- RC读清

- WC写清

3. 系统控制器寄存器电路设计

- 系统控制器-寄存器电路设计RW

- 系统控制器-寄存器电路设计WC

- 系统控制器-寄存器电路设计RC

- 系统控制器-寄存器电路设计RO

二、MCU系统控制器设计代码

先略,如有需要,再来补充学习!

第十讲 ARM M3 TOP集成

一、MCU系列培训-PAD介绍

- PAD时序参数

- PAD类型

1. PAD时序参数

- Transition Time(Rise/Fall)

2. PAD类型

- PAD-PBSxRN

- PAD-PBCDxRN

- PAD-PBCUxRN

- PAD-PBSUxRN

- PAD-PISDRN

- PAD-PICDRN

- PAD-PISRN

- PAD-PISURN

- PAD-PICURN

可配上拉、下拉;施密特、非施密特; - PAD-PXxRN

二、MCU IO复用及代码讲解

所有场景的IO都做出来的话,编程很大、

不同的场景将不同的IO映射

先略,如有需要,再来补充学习!