I2S

- I2S

- 什么是I2S

- I2S特点

- I2S接口

- I2S Philips 标准

- 高位先行(MSB)和低位先行(LSB)

- 时序要求

I2S

I2S(Inter-IC Sound)总线, 又称集成电路内置音频总线,是飞利浦半导体公司(现为恩智浦半导体公司)针对数字音频设备之间的音频数据传输而制定的一种总线标准。该总线专门用于音频设备之间的数据传输,广泛应用于各种多媒体系统。

什么是I2S

它为音频应用而设计,是一种电子的串行总线,用于连接电子音频设备。

它传输的是PCM音频数据(即脉冲编码调制),PCM音频数据是未经压缩的音频采样数据裸流,它是由模拟信号经过采样、量化、编码转换成的标准数字音频数据。I2S是音频数字化后数据排列的一种格式。

声音数字化过程:

转为 PCM 格式三个参数:

声道数、采样位数和采样频率。

采样频率:每秒钟取得声音样本的次数。采样频率越高,声音质量越好,还原越真实,但同时它占的资源比较多。

采样位数:每个采样点用多少二进制位表示数据范围。量化位数越多,音质越好,数据量也越大。

声道数:使用声音通道的个数,有单声道和立体声之分,立体声比单声道数据量翻倍。

音频数据量=采样频率×量化位数×声道数/8(字节/秒)

例如:在.WAV音频文件中,格式是PCM,它记录了所有采样到的模拟信号二进制电压值,而这正是可以在I2S总线上传输的数据。

I2S特点

①支持全双工和半双工通信。(单工数据传输只支持数据在一个方向上传输;半双工数据传输允许数据在两个方向上传输,但是在某一时刻,只允许数据在一个方向上传输,它实际上是一种切换方向的单工通信;全双工数据通信允许数据同时在两个方向上传输,因此,全双工通信是两个单工通信方式的结合,它要求发送设备和接收设备都有独立的接收和发送能力。

②支持主/从模式。(主模式:就是主CPU作为主机,向从机(挂载器件)发送接收数据。从模式:就是主CPU作为从机,接收和发送主机(挂载器件)数据。而主从机的分别其实是一个触发的作用,主机主动触发,从机只能被动响应触发。)

I2S接口

I2S总线必须的3个信号线

(1) SCK: (continuous serial clock) 串行时钟

串行时钟SCK,也叫位时钟BCLK。对应数字音频的每一位数据,SCK都有1个脉冲。SCK的频率 = 声道数 * 采样频率 * 采样位数。

(2) WS: (word select) 字段(声道)选择

字段选择信号WS,也叫LRCLK,用于切换左右声道的数据。WS的频率 = 采样频率。

字段选择信号WS表明了正在被传输的声道。I2S Philips标准WS信号的电平含义如下:

WS为0,表示正在传输的是左声道的数据;

WS为1,表示正在传输的是右声道的数据。

(3) SD: (serial data) 串行数据

串行数据SD,就是用二进制补码表示的音频数据。I2S串行数据在传输的时候,由高位(MSB)到低位(LSB)依次进行传输。

(4) I2S2ext_SD和I2S3ext_SD

用于控制I2S全双工模式的附加引脚。

(5) 主时钟MCLK

一般还有MCLK,主时钟。是采样频率的256倍或384倍。有时为了使系统间能够更好地同步,当I2S配置为主模式(并且SPI_I2SPR寄存器中的MCKOE位置1)时,使用此时钟,该时钟输出频率 256×fs,fs即音频信号采样频率(fs)。

对于系统而言,能够产生SCK和WS的信号端就是主设备,用MASTER表示,简单系统示意图如下:

I2S Philips 标准

对于所有数据格式和通信标准而言,始终会先发送最高有效位(MSB 优先)。

发送端和接收端必须使用相同的数据格式,确保发送和接收的数据一致。

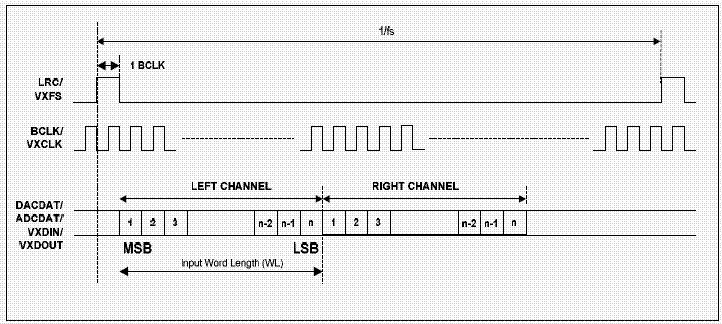

使用LRCLK信号来指示当前正在发送的数据所属的声道,为0时表示左声道数据。LRCLK信号从当前声道数据的第一个位(MSB)之前的一个时钟开始有效。LRCLK信号在BCLK的下降沿变化。发送方在时钟信号BCLK的下降沿改变数据,接收方在时钟信号BCLK的上升沿读取数据。LRCLK频率等于采样频率Fs,一个LRCLK周期(1/Fs)包括发送左声道和右声道数据。

对于这种标准I2S格式的信号,无论有多少位有效数据,数据的最高位总是被最先传输(在WS变化(也就是一帧开始)后的第2个SCK脉冲处)。这就使得接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位。这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位。

I2S典型的接口时序

高位先行(MSB)和低位先行(LSB)

高位先行即在传输一个字节的时候先传输高位;低位先行即在传输一个字节的时候先传输低位。高位先行和低位先行是针对串行数据传输方式来说的。常见的串行传输方式有串口(UART)、I2C、SPI等。以串口传输方式为例,标准的串口传输方式是低位先行,如下图所示,芯片在通过TX引脚发送数据时,依次发送位0、位1……位7。

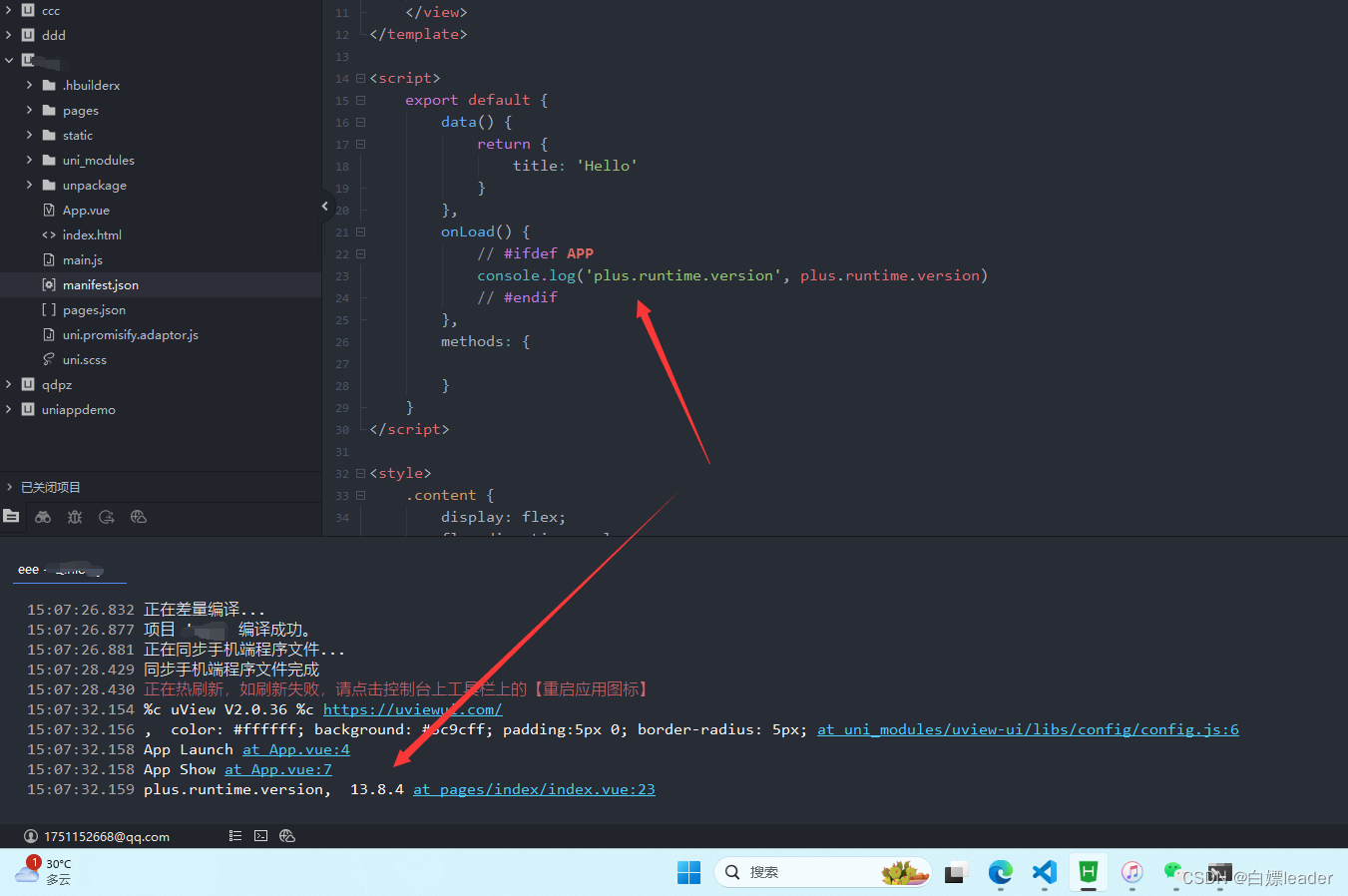

下面以常用的模拟I2C为例,从代码上更加直观的看一下高位先行和低位先行。

I2C在数据传输时,所有使用I2C的设备必须遵循I2C协议,协议规定了数据传输必须是高位先行,这样才能实现通用性。以下代码为I2C发送一个字节:

void IIC_Send_Byte(u8 txd)

{ u8 t; SDA_OUT(); IIC_SCL=0; //拉低时钟开始传输数据for(t=0;t<8;t++) //循环8次,即发送一个字节{ IIC_SDA=(txd&0x80)>>7;//每次左移7位,即将最高位移到最低位,发送出去txd<<=1; delay_us(2); IIC_SCL=1;delay_us(2); IIC_SCL=0; delay_us(2);}

}

从第8行和第9行代码中可以看到,在发送一个字节时,先将最高位发送出去,然后是第6位……第0位;同样在接收一个字节时,接收到的第1位认为是最高位,接收一个字节代码如下:

u8 IIC_Read_Byte(unsigned char ack)

{unsigned char i,receive=0;SDA_IN();//SDAÉèÖÃΪÊäÈëfor(i=0;i<8;i++ ){IIC_SCL=0; delay_us(2);IIC_SCL=1;receive<<=1; //每次左移一位,循环8次后,第1次接收的位移到了最高位,依次类推if(READ_SDA)receive++; delay_us(1); } if (!ack)IIC_NAck();//发送非应答elseIIC_Ack(); //发送应答 return receive;

}

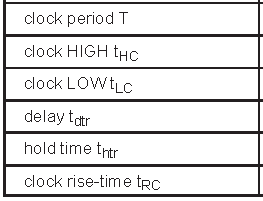

时序要求

其中:

在12s总线中,任何设备都可以通过提供必需的时钟信号成为系统的主导装置,而从属装置通过外部时钟信号来得到它的内部时钟信号,这就意味着必须重视主导装置和数据以及命令选择信号之间的传播延迟,总的延迟主要由两部分组成:

- 外部时钟和从属装置的内部时钟之间的延迟

- 内部时钟和数据信号以及命令选择信号之间的延迟

对于数据和命令信号的输入,外部时钟和内部时钟的延迟不占据主导地位,它只是延长了有效的建立时间(set—up time)。延迟的主要部分是发送端的传输延迟和设置接收端所需的时间。

T是时钟周期,Tr是最小允许时钟周期,T>Tr这样发送端和接收端才能满足数据传输速率的要求。

对于所有的数据速率,发送端和接收端均发出一个具有固定的传号空号比(mark—space ratio)的时钟信号,所以t LC和t HC是由T所定义的。t LC和t HC必须大于0.35T,这样信号在从属装置端就可以被检铡到。

延迟(t dtr)和最快的传输速度(由T tr定义)是相关的,快的发送端信号在慢的时钟上升沿可能导致t dtr 不能超过 t RC而使t htr为零或者负。只有t RC不大于t RCmax的时候(t RCmax>: 0.15T),发送端才能保证t htr大于等于0。

为了允许数据在下降沿被记录,时钟信号上升沿及T相关的时间延迟应该给予接收端充分的建立时间(set-up time)。数据建立时间(set-up time)和保持时间(hold time)不能小于指定接收端的建立时间和保持时间。

转载文章:https://www.pianshen.com/article/6461715634/

转载视频:https://www.bilibili.com/video/BV1Pt4y1X7M1?from=search&seid=6713006475754183255

转载文章:https://blog.csdn.net/suaoyang/article/details/29351833

转载文章:https://blog.csdn.net/u013073067/article/details/83590536

开源资料:i2s总线规范 specification https://ishare.iask.sina.com.cn/f/12109759.html