功耗结构设计

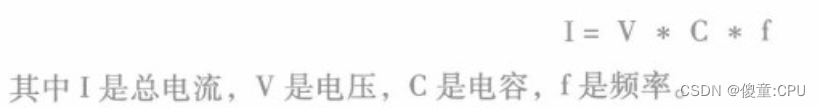

在COMS技术中,动态功耗与门和金属引线的寄生电容充放电有关。

因此,为了减少驱动电流,必须减少这三个关键的参数。在FPGA设置中,电压通常是固定的,只留下电容C和频率f对电流的操纵。电容C直接与随时被触发的门的数量以及连接这些门的布线长度有关,频率f直接与时钟频率有关。

1、时钟控制

在同步数字电路中降低动态功耗的最有效和广泛使用的技术是动态禁止在特定区域中的时钟,在数据流中这个区域不需要在特定级激活。

在设计的非激活区域暂时终止时钟是这类功耗最小化最直接的方法。

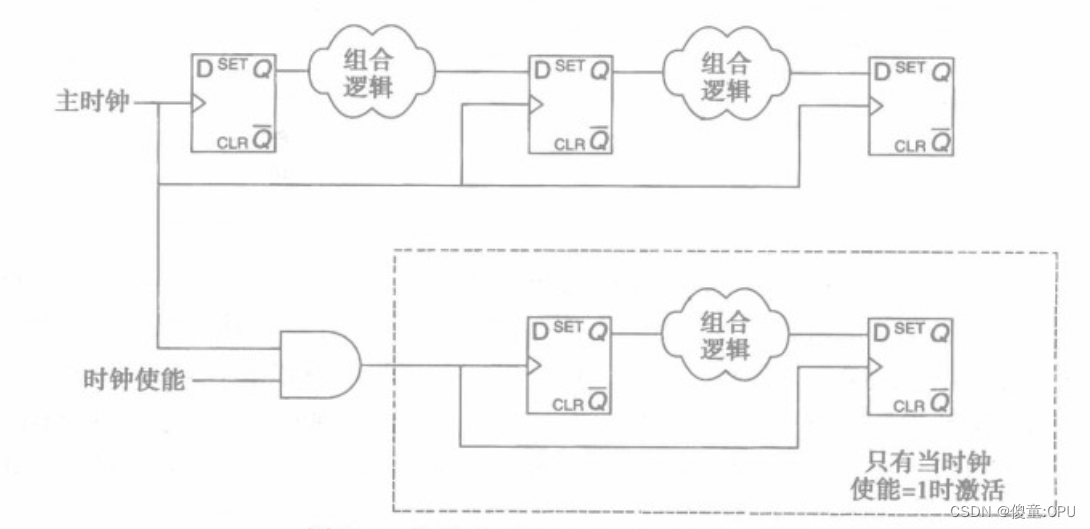

推介的方法是利用触发器的时钟使能引脚,或利用全局时钟的多路选择器(mux)。有时会借助直接选通系统时钟的方法。

诸如时钟使能触发器输入或全局时钟多路选择器等时钟控制资源应该代替直接时钟选通来使用。

时钟选通是减少动态功耗的直接手段,但是在实现和时序分析方面会产生困难。

对FPGA设计者,选通时钟会引入新的时钟区域,并将产生困难。

1.1时钟偏移

是指同样的时钟产生的多个子时钟信号之间的延时差异。skew通常是时钟相位上的不确定。由于时钟源到达不同