介绍

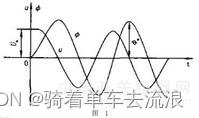

DAC 模块由一个内部 12 位 DAC 和一个能够驱动外部负载的模拟输出缓冲器组成。 DAC 输出上的集成下拉电阻有助于在禁用输出缓冲器时提供已知的引脚电压。 这个下拉电阻不能被禁用,并且仍然作为引脚上的无源组件,即使对于其他共享的 pinmux 功能也是如此。 缓冲 DAC 是一种通用 DAC,除交流波形(如正弦波)外,还可用于生成方波、三角波等。 对 DAC 值寄存器的软件写入可以立即生效,也可以与 EPWMSYNCPER 事件同步。

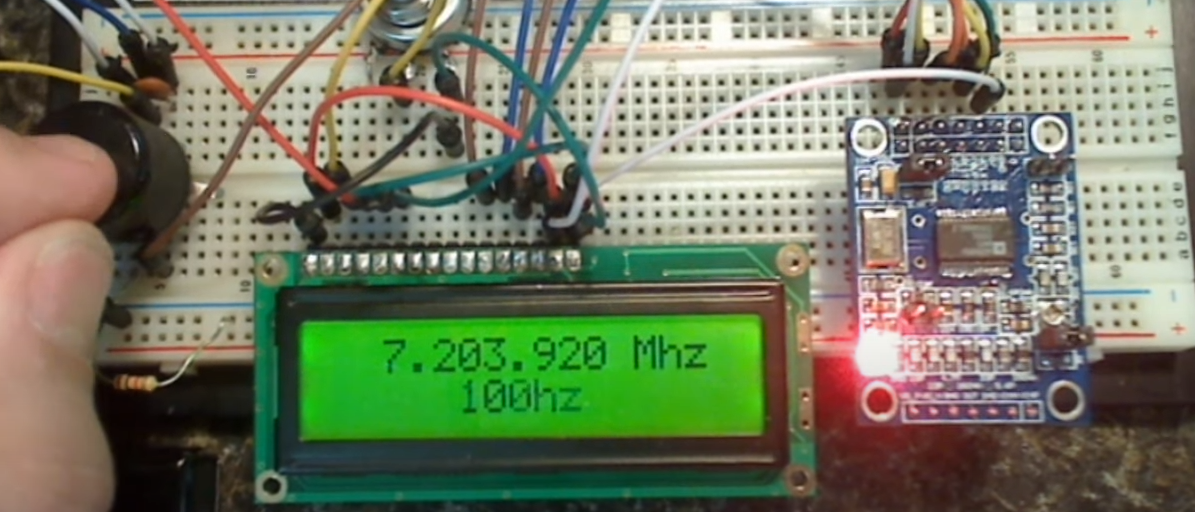

内部功能框图如下:

DAC配置流程

内部 DAC 的参考电压源 DACREF 可在 VDAC 和 VREFHI 之间选择。

缓冲 DAC 模块中存在两组 DACVAL 寄存器,DACVALA 和 DACVALS。

DACVALA 是一个只读寄存器,可主动控制缓冲的 DAC 值。 DACVALS 是一个可写影子寄存器,它可以立即加载到 DACVALA 中,也可以与下一个 EPWMSYNCPER 事件同步。

如果缓冲 DAC 输出电压时缓冲 DAC 的时钟被禁用,则输出电压不受影响,但 DACVALA 和 DACVALS 将不再随寄存器写入而更新。 启用缓冲 DAC 的时钟会将其恢复到禁用时钟之前的状态。

初始化顺序

- 使能缓冲 DAC 时钟。

- 用 DACREFSEL 设置 DACREF。

- 使用 DACOUTEN 为缓冲 DAC 上电。

- 等待上电时间结束后再输出电压。 要确定缓冲 DAC 的上电时间,请参阅特定器件的数据手册。

- 对于缓冲 DAC 的可预测行为,对 DACVALS 的连续写入应根据 buf 的建立时间间隔开

DAC 偏置校准

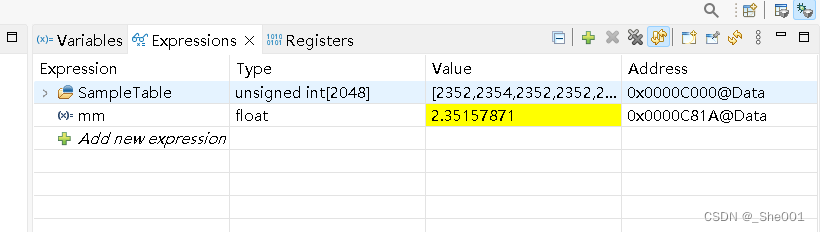

零偏移误差定义为中间码 (2048) 处的电压与 1.25v(对于 2.5v 参考电压)之间的差异。 DAC 偏移误差在 2.5v 参考电压下进行校准,并作为 Device_cal() 函数的一部分加载到 DAC 偏移调整寄存器中。 如果 DAC 用于 2.5v 以外的任何参考电压,则必须调整偏移微调以确保偏移误差性能保持在器件特定数据手册限制范围内。 DAC 偏移寄存器是一个 16 位寄存器,在寄存器的下半部分包含 8 位有符号偏移微调。 使用 C2000Ware 中的函数调用 DAC_tuneOffsetTrim() 来调整偏移量。

EPWMSYNCPER 信号

EPWMSYNCPER 来自 EPWM 的时基子模块。当 DACCTL [LOADMODE] = 1 时加载 DACVALA 的 EPWMSYNCPER 信号是电平触发加载。 如果 EPWM 的 TBCTR 和 TBPRD 都为 0,则 EPWMSYNCPER 将保持在高电平,并且无论 DACCTL [LOADMODE] 的值如何,都将立即从 DACVALS 加载 DACVALA。因此,建议在将 DACCTL [LOADMODE] 设置为 1 之前先配置 EPWM。

Lock Registers

提供了一个 DACLOCK 寄存器来防止虚假写入修改 DACCTL、DACVALS 和 DACOUTEN 寄存器。 一旦寄存器通过 DACLOCK 得到保护,写入访问将被锁定,直到器件复位。

DAC寄存器

详细内容见参考手册相关章节,此处列出主要内容

DAC Base Addresses

DAC_REGS Registers

Register to Driverlib Function Mapping