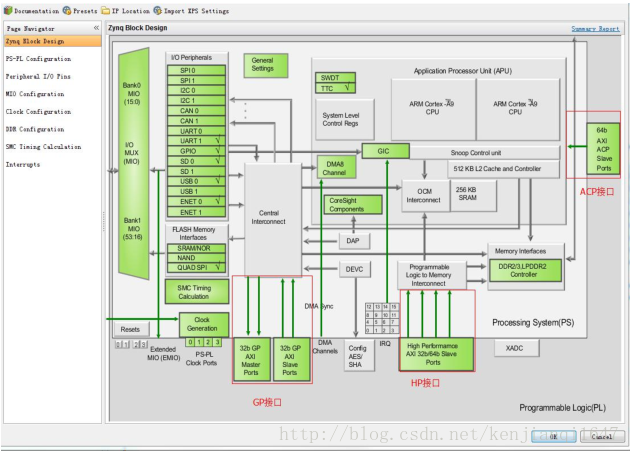

1、PL和PS的接口类型总共有两种:

(1)功能接口:AXI、EMIO、中断、DMA流控制、时钟调试接口。

(2)配置接口:PCAP、SEU、配置状态信号和Program/Done/Init信号。这些信号连接到PL内配置模块的固定逻辑上,给PS提供对PL的控制能力。

2、AXI总线:AXI (Advanced eXtensible Interface)本是由ARM公司提出的一种总线协议。用于PL和PS之间的通信。

总线:是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般由由数据线、地址线、控制线等构成。

接口:是一种连接标准,又常常被称之为物理接口。

协议:就是传输数据的规则

(1)AXI总线:在ZYNQ中有支持三种AXI总线

AXI4:(For high-performance memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允许最大256轮的数据突发传输;

AXI4-Lite:(For simple, low-throughput memory-mapped communication )是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元。

AXI4-Stream:(For high-speed streaming data.)面向高速流数据传输;去掉了地址项,允许无限制的数据突发传输规模。

(2)zynq的AXI接口共有9个,包括如下类型:

1)AXI_ACP接口:加速器一致性接口,用来管理DMA之类不带缓冲的AXI外设,PS端是Slave接口。

通过该接口PL端可以直接访问PS部分cache,故PL逻辑可以直接从cache中拿到CPU的计算结果,同时也可以进一步第一时间将计算的逻辑加速运算的结果送至CPU。

2)AXI_HP接口:高性能/带宽的AXI3.0标准接口,共有4个,PL模块作为主设备连接。。主要用于PL访问PS上的存储器(DDR和On-Chip RAM)。

AXI-HP接口主要是为了PL访问PS上的存储器(DDR和on-chip RAM)而设计的高速数据通路。AXI-HP端口分为两部分一部分直接和PL相连,另一部分连接到AXI interconnect。例如视频处理时,高清的图像有FPGA直接采集处理,然后通过AXI-HP接口将数据传输到DDR中,供APU完成进一步图像处理。

3)AXI_GP接口:通用AXI接口,共有4个,包括两个32位主设备接口和两个32位从设备接口。

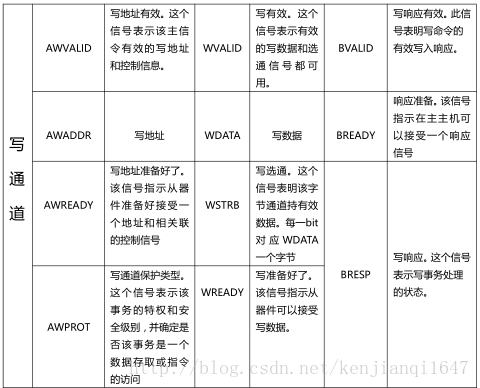

(3)AXI协议

AXI总线协议的两端可以分为分为主(master)、从(slave)两端,他们之间一般需要通过一个AXI Interconnect相连接,作用是提供将一个或多个AXI主设备连接到一个或多个AXI从设备的一种交换机制。AXI Interconnect的主要作用是,当存在多个主机以及从机器时,AXIInterconnect负责将它们联系并管理起来。由于AXI支持乱序发送,乱序发送需要主机的ID信号支撑,而不同的主机发送的ID可能相同,而AXI Interconnect解决了这一问题,他会对不同主机的ID信号进行处理让ID变得唯一。

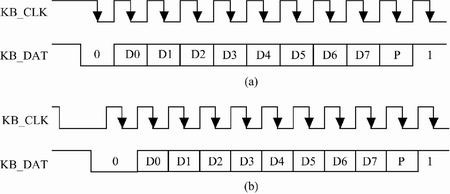

(4)AXI协议之握手协议

AXI4 所采用的是一种 READY,VALID 握手通信机制,简单来说主从双方进行数据通信前,有一个握手的过程。传输源产生 VLAID 信号来指明何时数据或控制信息有效。而目地源产生 READY 信号来指明已经准备好接受数据或控制信息。传输发生在 VALID和 READY 信号同时为高的时候。VALID 和 READY 信号的出现有三种关系。

1) VALID 先变高 READY 后变高

2) READY 先变高 VALID 后变高

3) VALID 和 READY 信号同时变高

3、 AXI4-Lite 详解

(1)先要自定义一个AXI-Lite的IP,新建工程之后,选择,菜单栏->Tools->Creat and Package IP。

(2)next - 选择Create AXI4 Peripheral,然后Next - 默认,选择Next - 这里接口类型选择Lite,选择Next - 选择Edit IP,点击Finish - 此后,Vivado会新建一个工程,专门编辑该IP,通过该工程,我们就可以看到Vivado为我们生成的AXI-Lite的操作源码。

(3)代码分析:

文章转自:https://blog.csdn.net/zhongjianblackberry/article/details/79456338