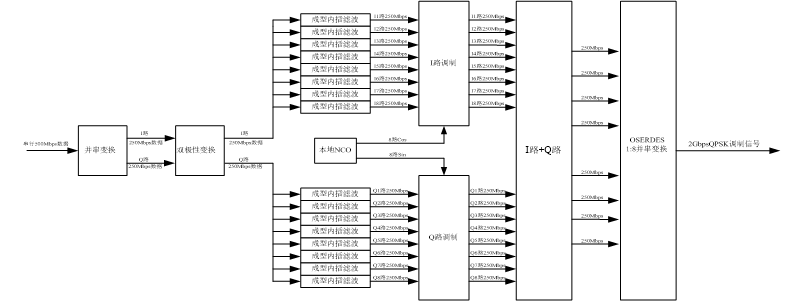

在前面的章节中,已经讲过QPSK调制的方案和Matlab算法仿真,在本篇中,主要讲解基于FPGA的高速QPSK调制的实现。根据前面提到的技术指标,本系统传输的数据速率为500Mbps,中频为720MHz,因此,传统的串行QPSK调制已经不合适在FPGA中实现,需采用全数字的并行方式进行调制,具体实现框图如图1所示,有需要的读者,可以下载完整的调制代码,进行参考。

图1 基于FPGA的并行QPSK调制实现框图

1 成型滤波器设计

在本方案中,由于中频为720MHz,根据奈奎斯特采样定理,至少需要2倍以上的采样率才能将数据恢复出来,因此设计的数模转换主时钟为2GHz,而串行输入的数据速率为500Mbps,转换为IO两路,每路数据速率为250Mbps,这样相当于需要内插8倍的时钟至2GHz。考虑到FPGA具体实现,采用并行8路多相滤波器处理,如图2所示。

![[C++]vector模拟实现](https://img-blog.csdnimg.cn/2c75a68a41454f10a47da1e110d276cc.png)