本章将着重讲述PCIe的MSI和MSI-X中断机制,在FPGA应用中主要通过XDMA中断与上位机进行通信,本文略长。

-

简介

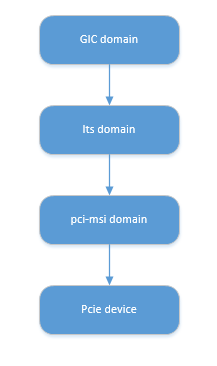

在PCIe总线中,MSI和MSI-X中断机制使用存储器写请求TLP向处理器提交中断请求,所以将MSI/MSI-X中断信息的存储器写报文简称为MSI/MSI-X报文。

x86使用FSB Interrupt Message方式处理MSI/MSI-X中断请求。

PCIe设备在提交MSI中断请求时,都是向MSI/MSI-X Capability结构中的Meaasge Address的地址写Message Data数据,从而组成一个存储器写TLP,向处理器提交存储器写请求。

翻译一下就是说:

由于存储器域和PCIe域地址的相互映射,向MessageAddress地址写数据,也就是向对应的存储器域地址写数据,写入的数据为Message Data,从而组成一个存储器写TLP,向存储器提交存储器写请求。

-

虚拟中断线方式

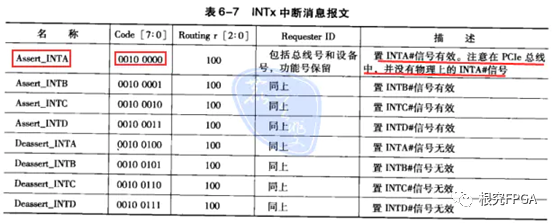

在PCIe桥下挂载PCI设备时,如果该PCI设备不支持MSI终端机制,在PCI设备发出INTx中断请求时,PCIe桥将该INTx中断信号转换为INTx中断消息报文,并向Root Complex提交中断请求。在PCIe总线中,一共规定了8种INTx中断消息报文:

当PCIe设备不使用MSI报文向RC提交中断请求时,可以首先使用ASSERT_INTx向RC提交中断请求,当RC处理完毕后发出一个Deassert_INTx中断请求,设备接收到Deassert_INTx报文后,将结束接收到的INTx中断请求。

PCIe设备接收到一个INTx中断请求后,需要首先结束该INTx中断消息,之后根据中断路由表产生一个新的INTx中断消息,直到这个中断消息传递到RC。

-

Legacy Interrupt

Legacy Interrupt,翻译过来是传统中断,百思不得其解,直到看到这样一段解释:

Legacy interruptare two interrupts that were in ARM before GIC arrived:

nIRQ-normalinterrupt request

fIRQ-fastinterrupt

Legacyinterrupts were made for single-core processors,and they don’t support multi-coreprocessors internally.

The legacy arehardwired into one of the cores

LegacyInterrupts:传统中断,非MSI中断,PCI设备使用INTx中断请求的方式与电平触发类似,而MSI/MSI-X中断请求的方式与边沿触发方式类似。

当PCI设备的INTx信号有效时,PCIe桥将该信号转换为Assert_INTX消息报文,当这些INTx信号无效时,PCIe桥将该信号转换为Deassert_INTx中断信号。

-

MSI与MSI-X的区别

MSI中断机制最多支持32个中断请求,而且要求中断向量连续;

MSI-X可以支持更多的中断请求,而且并不要求中断向量连续。

MSI/MSI-X Capabiliity结构

PCIe设备可以通过MSI或MSI-X报文向处理器提交中断请求,但是对于某个PCIe设备,可能仅支持一种报文,PCIe设备可以含有两种中断Capability,一种是MSI Capability,另一种是MSI-X Capability结构,但是一般情况下,PCIe设备一般只包含一种结构,或为MSI Capability结构,或为MSI-X Capability结构。

-

MSI Capability结构

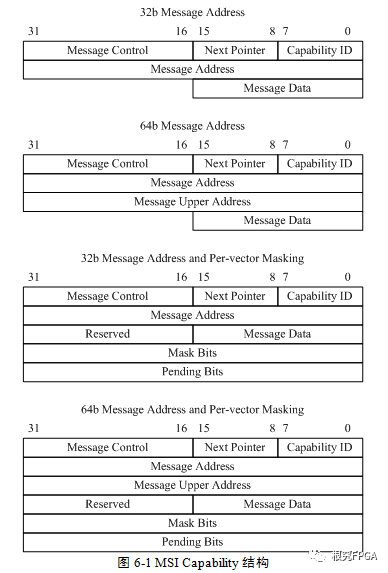

MSI Capability有四种结构形式,翻译一下就是有四种结构体,有两种是不带中断掩码的,32、64位的信息地址的MSI Capability,还有两种是带中断Masking的MSI Capability,MSI Capability结构体的结构如图所示:

Capability ID

当前MSI Capability结构体的ID。

在PCIe设备中,每一个MSI Capability都有自己的中断号。

Message Control

存放当前PCIe设备使用MSI机制进行中断请求的状态与控制信息,诸如是否支持中断掩码,中断地址是否为64bit,实际分配的中断个数和理论上支持的中断个数。

Message Address:

当MSI Enable位有效时,该寄存器存放目标存储器写事务地址的低32位,该寄存器的32:2字段有效,系统软件可以对该字段进行读写操作,位[1:0]为0。

Message UpperAddress:

当MSI Enable位有效时,该寄存器存放目标存储器写事务地址的高32位。

Next Pointer

下一个MSI Capability结构体的地址。

Message Data[15:0]

当MSI Enable位有效时,该字段存放MSI报文使用的中断数据,PCIe设备可以通过改变Message Data中的数据发送不同的中断请求。

如果一个PCIe设备需要使用8个中断请求且使用MSI中断机制时,Meaasge Data[2:0]字段的值可以是3’b000~3’b111,因此可以发送8个中断请求,但是这8个中断请求的中断号必须要保持连续,在许多中断控制器中,Message Data字段连续也意味着中断控制器需要为这个PCIe设备分配8个连续的中断向量号。

Mask Bits

中断掩码寄存器

PCIe总线规定当一个设备使用MSI中断机制时,最多使用32个中断向量,一个设备最多发送32种中断请求,所以Mask Bits为32位,相应位为1时表示相应的中断被屏蔽。该字段和Pending字段对于MSI中断机制是可选字段。

Pending Bits

待处理中断寄存器。

该字段对于系统软件可读,PCIe设备内部逻辑可以改变该字段的值。该字段的长度为32位,与Mask字段配合使用,当一个中断对应的Mask bit位为1(屏蔽)时,Pending Bits字段对应的位将被PCIe内部逻辑置一,此时PCIe设备并不会向中断控制器发送MSI中断报文;当系统软件将对应的Mask bit位由1改为0时,PCIe设备向中断控制器发送MSI中断报文。

在PCIe设备驱动程序开发时,有时需要Mask Bits和Pending Bits字段配合防止处理器丢失中断请求。

————————————————————

-

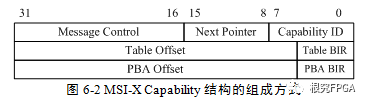

MSI-X Capability结构

MSI-X中断机制提出目的是扩展PCIe设备使用的中断向量个数(次要),同时解决MSI中断要求使用中断向量必须保持连续的问题(主要)。

有时在一个PCIe中断控制器中,虽然有8个以上的中断向量号,但是很难保证这8个中断向量号是连续的,此时该PCIe设备的“”Multiple Interrupt Capable将小于“Multiple Interrupt Enable”字段。

使用MSI-X机制可以很好地解决该问题,在MSI-X Capability结构中,每一个中断向量使用独立的Meaasge Address和Message Data字段,从而中断控制器可以更加合理的为PCIe设备分配中断资源。

与MSI Capability寄存器相比,MSI-X Capability寄存器使用一个结构体来专门存放“Message Address”字段和“Message Data”字段,而不是将这两个字段放入MSI-X Capability寄存器中,MSI-X机制中存放“Message Data”和“Message Address”字段的结构体就称为MSI-X Table。

-

MSI-X Capability ID

该字段存放该Capability的ID号。

-

Next Pointer

下一个MSI-X Capability的地址。

-

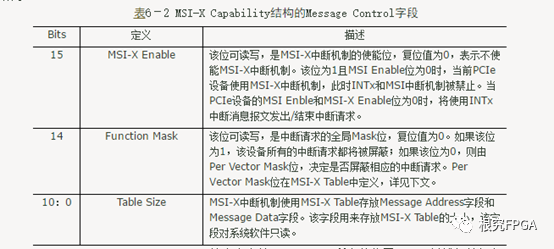

Message Control

指明当前PCIe设备使用MSI-X机制进行中断请求的状态和控制信息。

可以看到,与MSI机制相比,该寄存器为16bit,将相应寄存器数量缩减一半。

-

Table BIR(BAR Indicator Register)

基地址指示寄存器,该字段存放MSI-X Table所在的位置,PCIe总线规定,MSI-X Table存放在BAR空间中,该寄存器指示使用BAR0~BAR5寄存器中的哪个空间存放MSI-X Table,该字段由3位构成,3’b000~3’b101分别对应BAR0~BAR5。

-

Table Offset

该字段存放MSI-X Table结构体在对应BAR空间中的偏移。

-

PBA BIR

Pengding Bit Array字段,该字段存放Pending字段位于哪个BAR空间中,与Table BIR类似。

-

PBA OFFSET

该字段指示在BAR空间中,Pending字段对应的偏移。

-

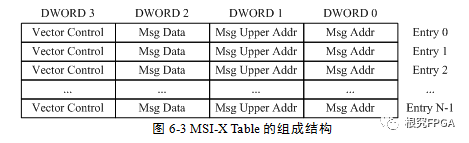

MSI Table

MSI-X Table存放该设备使用的所有“Message Address”和“Message Data”!

MSI-X Table由多个Entry组成,其中每个Entry与一个中断请求相对应,每个Entry中存在四个参数:

Msg Addr

当MSI-X Enable位有效时,该字段存放MSI-X存储器写事务的目的地址低32位,该双字的31:2位有效,系统软件可读可写。

Msg Upper Addr

当MSI-X Enable位有效时,该字段存放MSI-X存储器写事务的目的地址高32位。

Msg Data

存放MSI-X中断报文使用的数据。

Vector Control

该字段可读可写,该字段只有第0位(Per Vector Mask)位有效,其他未保留,该位在复位时为0,为1时,PCIe设备不能使用该Entry提交中断请求,与MSI机制中的Mask位类似。

-

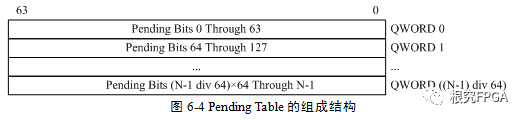

Pending Table

Pending位需要与Per Vector Mask位配套使用。

当Per Vector Mask位为1时,PCIe设备不能马上发送MSI-X中断报文,而是需要首先将对应的Pending位置一,当系统软件将Per Vector Mask清零时,PCIe设备需要提交MSI-X中断请求,同时将Pending位清零。

————————————————————

-

x86处理器处理MSI-X中断请求

PCIe设备发出MSI-X中断请求的方式与MSI机制类似,都是向对应的存储器地址(Message Address)写中断数据(Message Data),只是MSI-X机制支持更多的中断类型,同时允许“Message Data”中断向量可以不连续。

MSI-X机制使用的Message Data与Message Address并不放在配置空间中,而是放在BAR(基地址空间)中,从而可以由用户决定所使用的中断请求的个数。

-

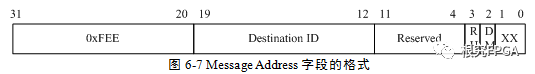

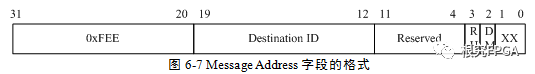

PCIe设备使用Message Address字段

在x86处理器系统中,PCIe设备使用的Message Address字段仍保存PCI总线域的存储器地址,其格式为:

其中第31~20位存放FSB Interrupt存储器空间的基地址,其值为0xFEE。当PCIe设备对“0xFEEx_xxxx”这段“PCI域”的地址空间进行写操作时,MCH/ICH会首先进行“PCI总线域”到“存储器域”的地址转换,之后将这个写操作翻译为FSB总线的Interrupt Message总线事务,从而向CPU内核提交中断请求。

-

Destination ID

该字段保存目标CPU的ID号。

-

RH(Redirection Hint Indication)

该字段指示是否进行中断转发,当RH为0时,表示FSB Interrupt Message中断报文直接发向与Destination ID字段相同的CPU,为1时,将使能中断转发功能。

-

DM(Destination Mode)

该字段表示在传递优先权最低的中断请求时,Destination ID字段被翻译为Logical或者Physical APIC ID。

-

PCIe设备使用Message Data字段

-

Trigger Mode

中断触发方式控制寄存器,

2’b00: PCIe设备使用边沿触发方式申请中断

2’b10: PCIe设备使用低电平触发方式申请中断

2’b11: PCIe设备使用高电平触发方式申请中断

-

Vector

表示这个中断使用的中断向量,FSB Interrupt Message总线事务在提交中断请求的同时,也将中断向量提交给处理器,因此使用FSB Interrupt Meaasge总线事务时,处理器不需要使用中断响应周期通过读取中断控制器获取中断向量号。该方式的中断请求效率较高。

在x86处理器中,MSI机制使用的Message Data字段与MSI-X机制使用的Message Data字段相同。但是当一个PCIe设备支持多个MSI中断请求时,其Message Data字段必须是连续的,即其使用的vector字段是连续的,使用MSI-X机制有效的解决了该问题。

-

Delivery Mode

该字段标识着如何处理来自PCIe设备的中断请求。

————————————————————

最后以一个实例对中断机制进行说明:X86处理器如何使用FSB总线Interrupt Message事务?

X86处理器使用FSB总线的Interrupt Message总线事务,向CPU提交MSI/MSI-X中断请求。

PCIe设备在发送MSI/MSI-X中断请求之前,系统软件需要合理的设置PCIe设备的MSI/MSI-X Capability寄存器,使Message Address寄存器的值为0xFEexx00y(xx:APIC ID y:RH+DM),同时合理的设置Message Data寄存器和Vector字段。

PCIe设备提交MSI/MSI-X中断请求时,首先需要向“Message Address”0xFEexx00y地址写“Message Data”寄存器中包含的数据,并以存储器写事务TLP的形式发送到RC。

P2P桥发现这个存储器写事务TLP的目的地址在FSB Interrupt存储器空间中,则将这个PCIe存储器写事务转换为Interrupt Message总线事务,并在FSB总线上传播。

FSB总线上的CPU,根据APIC ID信息,选择是否接受这个Interrupt Message总线事务,并进入中断状态,之后该CPU将直接从这个总线事务中获得中断向量号,执行相应的中断处理函数,而不需要从APICID中断控制器获得中断向量。

https://mp.weixin.qq.com/s?__biz=MzA5NjI1NDk0NQ==&mid=2247484502&idx=1&sn=7e58b23475bcbf0c5081773ee3e3ae86&chksm=90b3aad8a7c423ceb2f8fc94d8673be28efe09c227686f5c2d86829b72c8c9220838c445d9c3&scene=178&cur_album_id=1462562427954216964#rd