摘要:PCIE——第 10 章——MSI 和 MSI⁃X 中断机制

目录

第 10 章 MSI 和 MSI⁃X 中断机制

10. 1 MSI / MSI⁃X Capability 结构

10. 1. 1 MSI Capability 结构

10. 1. 2 MSI⁃X Capability 结构

10. 2 PowerPC 处理器如何处理 MSI 中断请求

10. 2. 1 MSI 中断机制使用的寄存器

10. 2. 2 系统软件如何初始化 PCIe 设备的 MSI Capability 结构

10. 3 x86 处理器如何处理 MSI⁃X 中断请求

10. 3. 1 Message Address 字段和 Message Data 字段的格式

10. 3. 2 FSB Interrupt Message 总线事务

10. 4 小结

第 10 章 MSI 和 MSI⁃X 中断机制

在 PCI 总线中, 所有需要提交中断请求的设备, 必须能够通过 INTx 引脚提交中断请求, 而 MSI 机制是一个可选机制。 而在 PCIe 总线中, PCIe 设备必须支持 MSI 或者 MSI⁃X 中断请 求机制, 而可以不支持 INTx 中断消息。

10. 1 MSI / MSI⁃X Capability 结构

PCIe 设备可以使用 MSI 或者 MSI⁃X 报文向处理器提交中断请求, 但是对于某个具体的PCIe 设备, 可能仅支持一种方式。 在 PCIe 设备中含有两个 Capability 结构, 一个是 MSI Ca⁃ pability 结构, 另一个是 MSI⁃X Capability 结构。 通常情况下一个 PCIe 设备仅包含一种结构, 或者为 MSI Capability 结构, 或者为 MSI⁃X Capability 结构

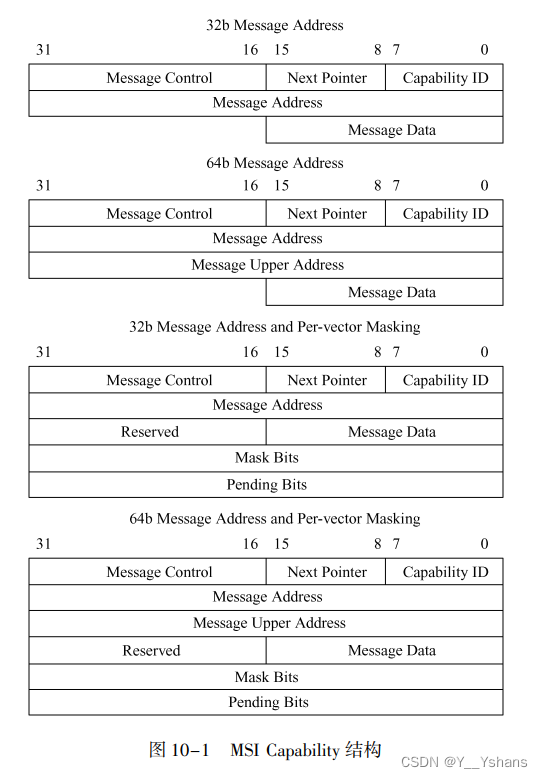

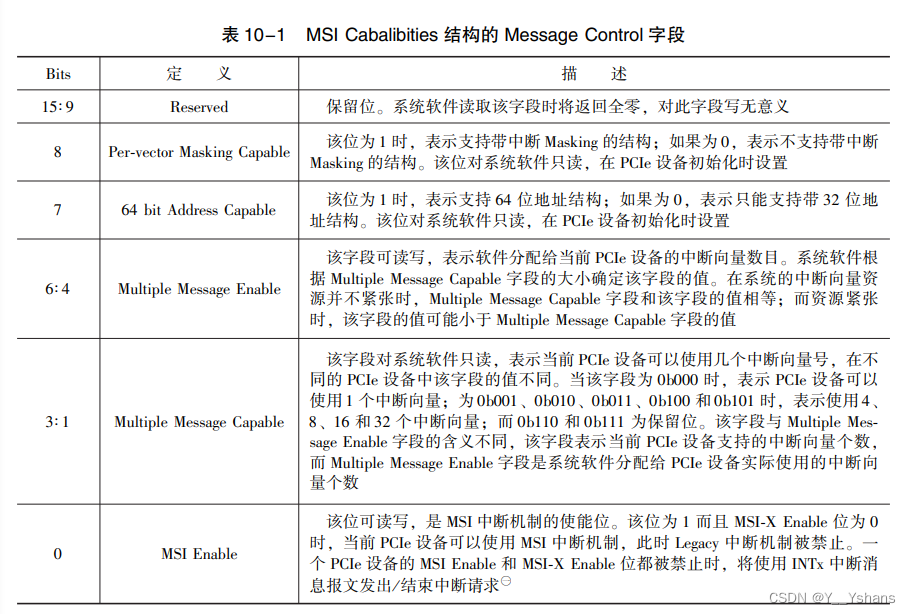

10. 1. 1 MSI Capability 结构

10. 1. 2 MSI⁃X Capability 结构

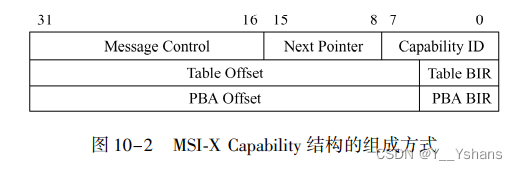

MSI⁃X Capability 中断机制与 MSI Capability 的中断机制类似。 PCIe 总线引出 MSI⁃X 机制 的主要目的是为了扩展 PCIe 设备使用中断向量的个数, 同时解决 MSI 中断机制要求使用中 断向量号连续所带来的问题。

有时在一个中断控制器中, 虽然具有 8 个以上的中断向量号, 但是很难保证这些中断向 量号是连续的。而使用 MSI⁃X 机制可以合理解决该问题。 在 MSI⁃X Capability 结构中, 每一个中断请求 都使用独立的 Message Address 字段和 Message Data 字段, 从而中断控制器可以更加合理地为 该设备分配中断资源。

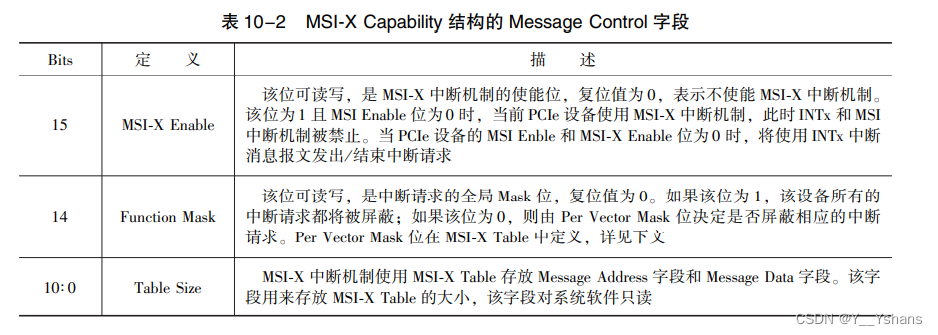

1. MSI⁃X Capability 结构

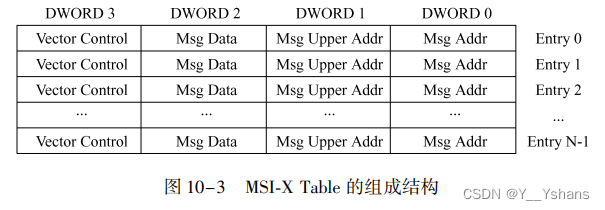

2. MSI⁃X Table

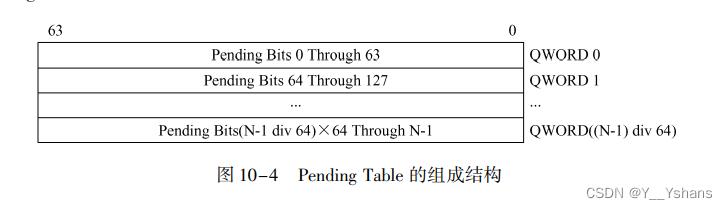

3. Pending Table

10. 2 PowerPC 处理器如何处理 MSI 中断请求

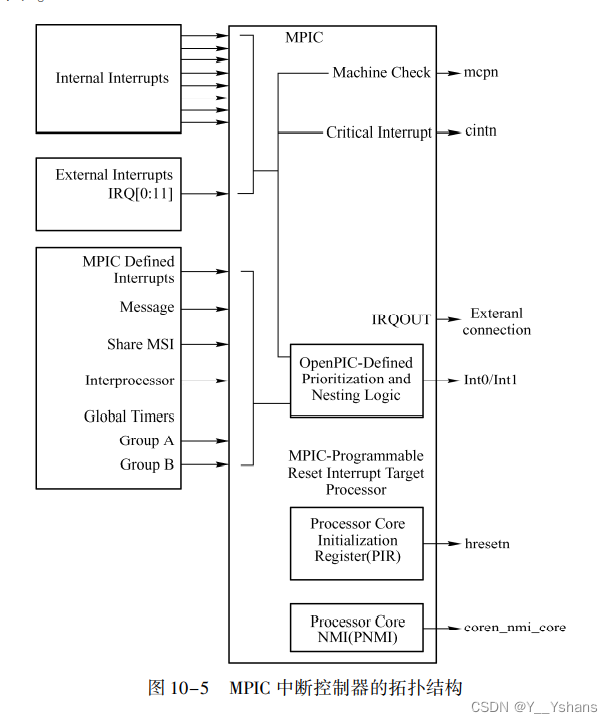

PowerPC 处理器使用 OpenPIC 中断控制器或者 MPIC 中断控制器, 处理外部中断请求。

使用 MPIC 中断控制器处理 MSI 中断时, PCIe 设备的 MSI 报文, 其目的地址为 MPIC 中 断控制器的 MSIIR 寄存器。 当该寄存器被 PCIe 设备写入后, MPIC 中断控制器将向处理器内 核提交中断请求, 之后处理器再通过读取 MPIC 中断控制器的 ACK 寄存器获得中断向量号, 并进行相应的中断处理。 这种方式与 x86 处理器的 FSB Interrupt Message 机制相比, 处理器 需要读取 ACK 寄存器, 从而中断处理的延时较大。

由上图所示, MPIC 中断控制器可以处理内部中断请求㊀ 、 外部中断请求, Message、 处 理器间中断请求和 Share MSI 中断请求等。

10. 2. 1 MSI 中断机制使用的寄存器

在 PowerPC 处理器系统中, MSI 机制的实现过程是 PCIe 设备向 MSIIR 寄存器写入指定 的数据。 MPIC 中断控制器发现该寄存器被写入后, 将向处理器提交中断请求。 处理器收到 这个中断请求后, 将通过读取 MPIC 中断控制器的 ACK 寄存器确定中断向量, 并依此确定 中断源。 为此 PowerPC 处理器还设置了其他寄存器实现 MSI 中断机制。

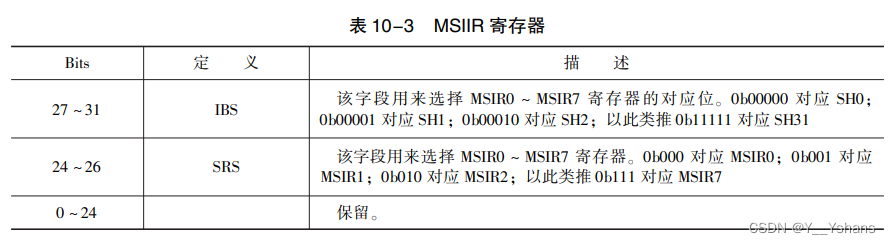

1. MSIIR 寄存器

在 PowerPC 处理器中, MSIIR ( Shared Message Signaled Interrupt Index Register) 寄存器 是实现 MSI 机制的重要寄存器。当 PCIe 设备对 MSIIR 寄存器进行写操作时, MPC8572 处理器将使能 MSIR0⁃MSIR7 寄存 器的相应位, 从而向 MPIC 中断控制器提交中断请求, 而中断控制器将转发这个中断请求, 由处理器进一步处理。

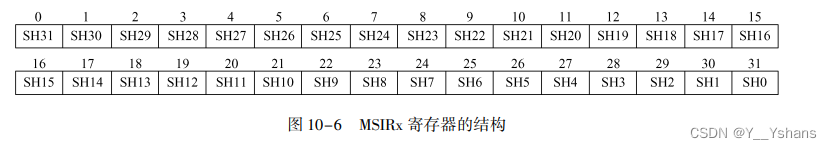

2. MSIR 寄存器组

MSIR ( Shared Message Signaled Interrupt Registers) 寄存器组共由 8 个寄存器组成, 分别为 MSIR0 ~ MSIR7。其中每一个 MSIRx 寄存器中有 32 个有效位, 分别为 SH0 ~ 31。系 统软件通过读取该寄存器获得中断源, 该寄存器读清除, 对此寄存器进行写操作没有意义。

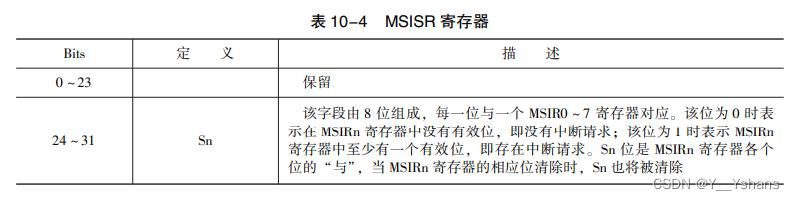

3. MSISR 寄存器

MSISR 寄存器 ( Shared Message Signaled Interrupt Status Register) 共由 8 个有效位组成, 每一位对应一个 MSIR 寄存器。MPC8572 处理器设置该寄存器的主要目的是方便系统软件定 位究竟是哪个 MSIR 寄存器中存在有效的中断请求。

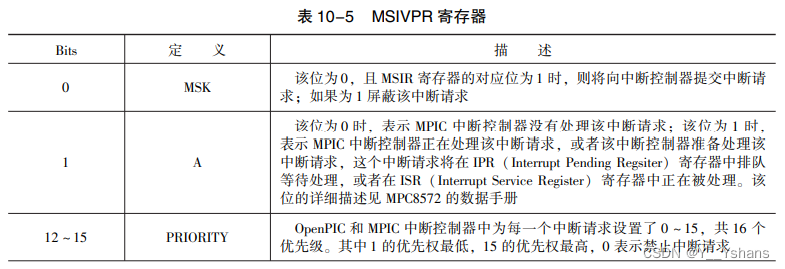

4. MSIVPR 寄存器组

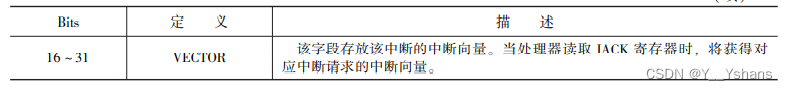

MSIVPR ( Shared Message Signaled Interrupt Vector / Priority Register) 寄存器组由 8 个寄存 器组成, 分别为 MSIVPR0 ~ 7 寄存器。分别为 MSIVPR0 ~ 7 寄存器。 该组寄存器设置对应中断请求的优先级别和中断向 量。 其中每个 MSIVPR 寄存器对应一个 MSIR 寄存器, MSIVPR 寄存器各字段的详细解释如 表 10-5 所示。

5. MSIDR 寄存器组

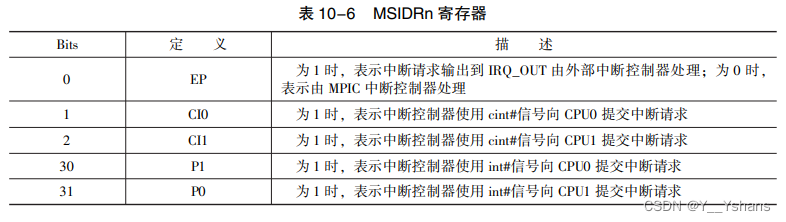

MSIDR ( Shared Message Signaled Interrupt Destination Registers) 寄存器组共由 8 个寄存 器组成, 分别为 MSIDR0 ~ 7。 其中每一个 MSIDRn 寄存器对应一个 MSIR 寄存器。 MPIC 中断控制器支持 Pass⁃through 方式, 在这种方式下, PowerPC 处理器可以使用外部 中断控制器处理中断请求 (这种方法极少使用) , 而不使用内部中断控制器。 MPIC 中断控 制器可以使用 cint#和 int#信号提交中断请求, 但是绝大多数系统软件都使用 int#信号向处理 器提交中断请求。 此外在 MPC8572 处理器中有两个 CPU, 分别为 CPU0 和 CPU1, MSI 机制提交的中断请 求可以由 CPU0 或者 CPU1 处理。 系统软件可以通过设置 MSIDRn 寄存器完成这些功能, 该 寄存器各字段的详细描述如表 10-6 所示。

10. 2. 2 系统软件如何初始化 PCIe 设备的 MSI Capability 结构

如果 PCIe 设备支持 MSI 机制, 系统软件首先设置该设备 MSI Capability 结构的 Message Address 和 Message Data 字段。如果该 PCIe 设备支持 64 位地址空间, 即 MSI Capability 寄存 器的 64 bit Address Capable 位有效时, 系统软件还需要设置 Message Upper Address 字段。 系 统软件完成这些设置后, 将置 MSI Capability 结构的 MSI Enable 位有效, 使能该 PCIe 设备的 MSI 机制。

其中 Message Address 字段所填写的值是 MSIIR 寄存器在 PCI 总线域中的物理地址。

10. 3 x86 处理器如何处理 MSI⁃X 中断请求

PCIe 设备发出 MSI⁃X 中断请求的方法与发出 MSI 中断请求的方法类似, 都是向 Message Address 所在的地址写 Message Data 字段包含的数据。 只是 MSI⁃X 中断机制为了支持更多的 中断请求, 在 MSI⁃X Capablity 结构中存放了一个指向一组 Message Address 和 Message Data 字段的指针, 从而一个 PCIe 设备可以支持的 MSI⁃X 中断请求数目大于 32 个, 而且并不要求 中断向量号连续。 MSI⁃X 机制使用的这组 Message Address 和 Message Data 字段存放在 PCIe 设备的 BAR 空间中, 而不是在 PCIe 设备的配置空间中, 从而可以由用户决定使用 MSI⁃X 中 断请求的数目。

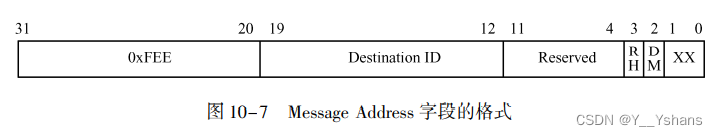

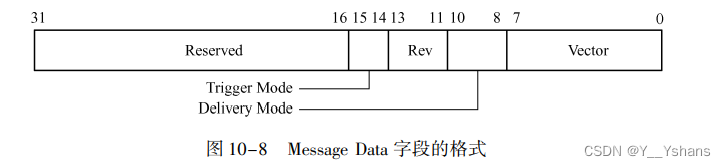

10. 3. 1 Message Address 字段和 Message Data 字段的格式

10. 3. 2 FSB Interrupt Message 总线事务

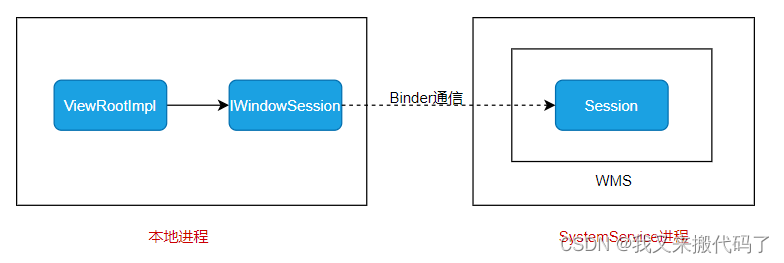

与 MPC8572 处理器处理 MSI 中断请求不同, x86 处理器使用 FSB 的 Interrupt Message 总 线事务, 处理 PCIe 设备的 MSI / MSI⁃X 中断请求。由上文所示, MPC8572 处理器处理 MSI 中 断请求时, 首先由 MPIC 中断控制器截获这个 MSI 中断请求, 之后由 MPIC 中断控制器向 CPU 提交中断请求, 而 CPU 通过中断响应周期从 MPIC 中断控制器的 ACK 寄存器中获得中 断向量。

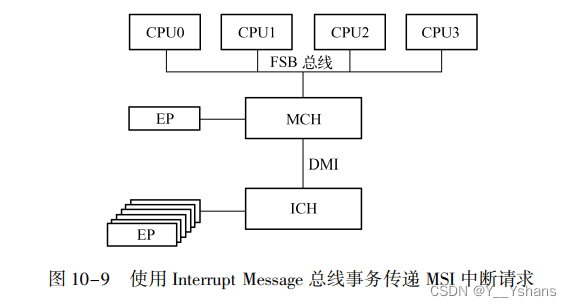

在 x86 处理器中, 这种方式基 本上已被弃用。 下面以图 10-9 为例, 说明 x86 处理器如何使用 FSB 总线的 Interrupt Message 总线事务, 向 CPU 提交 MSI / MSI⁃X 中断请求。

PCIe 设备在发送 MSI / MSI⁃X 中断请求之前, 系统软件需要合理设置 PCIe 设备 MSI / MSI⁃ X Capability 寄存器, 使 Message Address 寄存器的值为 0xFEExx00y㊀ , 同时合理地设置 Mes⁃ sage Data 寄存器 Vector 字段。 ㊀ 其中 xx 表示 APIC ID, 而 y 为 RH + DM。 PCIe 设备提交 MSI / MSI⁃X 中断请求时, 需要向 0xFEExx00y 地址写 Message Data 寄存器 中包含的数据, 并以存储器写 TLP 的形式发送到 RC。 如果 ICH 收到这个存储器写 TLP 时, 将通过 DMI 接口将这个 TLP 提交到 MCH。 MCH 收到这个 TLP 后, 发现这个 TLP 的目的地 址在 FSB Interrupts 存储器空间中, 则将 PCIe 总线的存储器写请求转换为 Interrupt Message 总 线事务, 并在 FSB 总线上广播。 FSB 总线上的 CPU, 根据 APIC ID 信息, 选择是否接收这个 Interrupt Message 总线事务, 并进入中断状态, 之后该 CPU 将直接从这个总线事务中获得中断向量号, 执行相应的中断 服务例程, 而不需要从 APIC 中断控制器获得中断向量。 与 PowerPC 处理器的 MPIC 中断控 制器相比, 这种方法更具优势。

10. 4 小结

本章详细描述了 MSI / MSI⁃X 中断机制的原理, 并以 PowerPC 和 x86 两个处理器系统为例 说明这两种中断机制实现机制。 本章因为篇幅有限, 并没有详细讲述这两个处理器使用的中 断控制器。 而理解这些中断控制器的实现机制是进一步理解 MSI / MSI⁃X 中断机制的要点。 对此部分有兴趣的读者可以继续阅读 MPIC 中断控制器和 APIC 中断控制器的实现机制, 以 加深对 MSI / MSI⁃X 中断机制的理解。 设备的中断处理是局部总线的设计难点和重要组成部分, 而中断处理的效率直接决定了 局部总线的数据传送效率。 在一个处理器系统的设计与实现中, 中断处理的优化贯彻始终。