文章目录

- 一、什么是架构

- 二、ARM架构分类

- Arm-A架构

- Armv7-A

- (1)指令集

- (2)处理器模式

- (3)通用寄存器

- (4)特殊寄存器

- Armv8-A

- 寄存器

- 指令集

- 异常模型及处理器模式

一、什么是架构

“架构”(Architecture)指的是功能规范,ARM架构即是ARM处理器的功能规范,包括以下主要内容:

- 指令集:每条指令的功能,指令在存储器中的表示方法(编码);

- 寄存器集:寄存器的数量、大小、功能,以及寄存器的初始状态;

- 异常模型:不同特权级、异常类型,以及采纳异常和从异常返回时的处理动作;

- 存储器模型:存储器的访问顺序,当软件必须执行准确维护时,缓存的行为;

- 调试、跟踪和统计:如何设置和触发断点,跟踪工具可以捕获的信息和采用的方式。

“架构”没有直接说明如何构建处理器并工作,它只是提供了一种软件和硬件之间行为规范,具体的处理器的构建和设计称为“微架构”Micro-Architecture,微架构包括:

- 流水线的长度和布局

- 缓存的数量和大小

- 单个指令的周期数(一条指令周期对应几个时钟周期)

- 其它可选特性

二、ARM架构分类

ARM提供了三种架构概要:

- A-Profile(应用):用于复杂得计算应用领域,如服务器、移动电话、汽车主机;

- R-Profile(实时):用于需要实时响应的地方,如安全关键应用或需要确定性响应的应用,如医疗设备、车辆转向、制动和信号等;

- M-Profile(微控制器):用于能效、功耗、尺寸有较强需求的地方,如深度嵌入式芯片、小型传感器、通信模块、智能家居产品等。

处理器的构建和设计称为“微架构”,微架构定义处理器的工作原理,包括:流水线的长度和布局,缓存的数量和大小,单个指令的周期数以及其它可选特性。

Arm-A架构

Armv7-A

(1)指令集

ARMv7-A架构是32位处理器架构,也是load/store架构,即数据处理指令操作在通用寄存器完成,只有load/store指令可以访问内存。此外ARM指令集还有一大特点,就是ARM指令集几乎所有的指令都可以增加条件码。

ARM指令集可以归为一下四类:

- 数据处理操作(ALU操作例如ADD);

- 内存操作(load/store);

- 控制流(循环,跳转,条件码等);

- 系统(协处理器,debug,模式切换等等)。

Armv7-A支持Arm(A32)和Thumb(T32)数据集。

ARM core只能在寄存器上执行数据处理,而不能直接在内存上执行。

数据操作指令一般由一个目标寄存器和两个源操作数组成,所有ARM数据处理指令都可以加后缀(Suffix),并影响状态标志(CPSR)。其基本格式如下:

Operation{cond}{S}Rd,Rn,Operand2 - Operation : 指令助记符;

- cond: 执行条件;

- S:后缀,是否影响CPSR寄存器状态位;

- Rd:目标寄存器;

- Rn:第一个操作数寄存器;

- Operand2:第二个操作数;

- {}:可选。

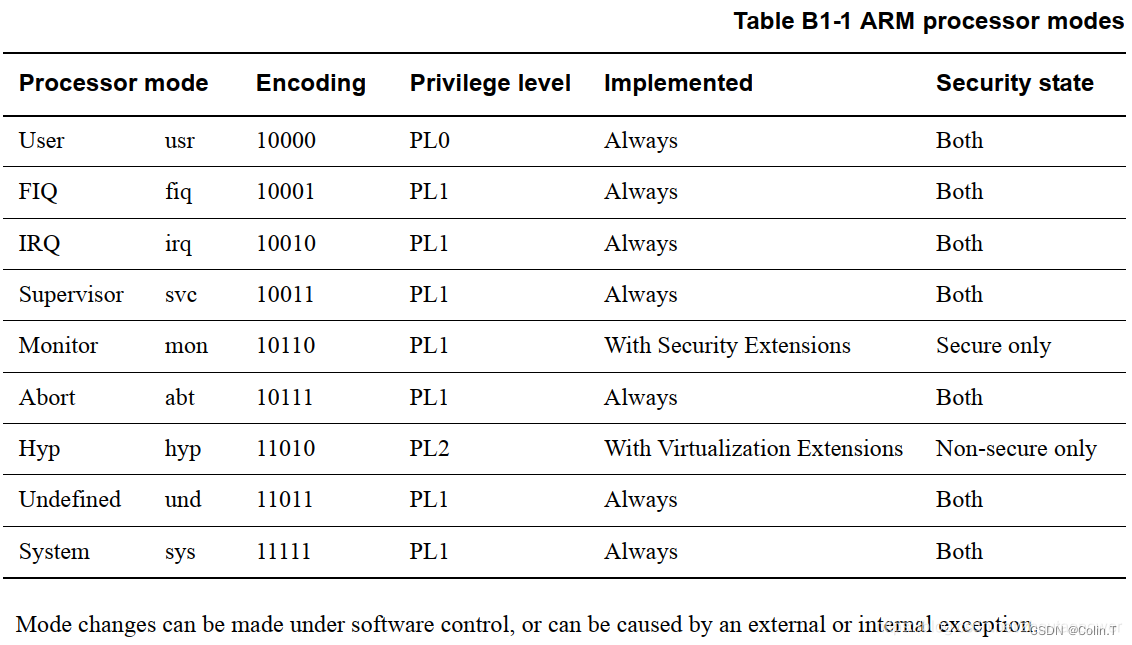

(2)处理器模式

ARMv7架构支持安全扩展,如果使能了安全扩展,ARMv7-A架构分为安全模式(Secure State)和非安全模式(Non-secure State)两个世界。

在非安全模式下,存在三种运行特权PL0,PL1和PL2(privilege level)。

| 特权等级 | 描述 |

|---|---|

| PL0 | PL0运行在用户模式(User),用于运行应用程序。该模式程序受限访问系统资源。对应Linux用户态。 |

| PL1 | PL1运行非用户模式和Hyp模式外的所有模式。Linux内核运行在PL1。包含了ARMv6架构中的System,SVC,FIQ,IRQ,UNDEF及Abort模式。此外,安全模式中的Montior也运行在PL1等级,管理安全模式和非安全模式的切换。 |

| PL2 | PL2用于虚拟化。虚拟化超级管理程序(Hypervisor)运行在 PL2。 |

处理器模式:

- User:用户模式,运行再 PL0 这个特权等级上,也就是没有特权等级,他是OS上运行应用程序时候的等级,他不可以访问系统资源(MMU 等),在这个模式下,无法主动切换模式,除非遇到中断或者异常(诸如 SWI 触发系统调用);

- FIQ:快中断模式,发生 FIQ快中断的时候处理器模式;

- IRQ:中断模式,发生 IRQ 快中断的时候处理器模式;

- Supervisor:管理员模式,复位后的默认模式,运行再 PL1 特权等级,可以通过 SWI(SVC) 系统调用呼叫产生Supervisor Call 异常,进入 Supervisor 模式,操作系统常用的模式;

- Monitor:监视模式,针对Security 扩展,不详细讨论;

- Abort:停止模式,当发生 Data Abort exception 或者 Prefetch Abort exception 异常时候进入这个模式;

- Hyp:当支持虚拟化扩展的时候模式,不详细讨论;

- Undefined:这是执行和指令相关的模式,当企图执行 UNDEFINED 指令的时候进入这个模式;

- System:系统模式,也是PL1 特权等级,和 Supervisor 的区别是,System 模式具有和 User 模式一样的寄存器,目前大多数系统未使用;

(3)通用寄存器

ARMv7-A 处理器有 16 个通用寄存器:R0~R15,其中:

- R13:通常用做堆栈指针 SP;

- R14:通常用作链接寄存器 LR;

- R15:通常用作程序计数器 PC;

对于每种特权等级访问系统资源的权限不一样,而处理器又有几种模式,每种模式对应的特权等级有一定区别;每一种处理器模式对应的寄存器也有一定区别:

- R0~R7,PC是所有模式下共享的;

- FIQ 模式下,R8-R12、SP、LR 都是有专门的寄存器,有的材料上,称之为“影子寄存器”,什么意思呢?这个模式下,有他专用的 R8~R12、SP、LR;

- 同样道理,Supervisor、Abort、Undefined、IRQ 等,都有他们自己模式下专用的 SP 和 LR,也就是说,从其他模式进来的时候,不需要针对这两个寄存器进行恢复现场;

- FIQ 之所以称之为 FIQ,从软件上也看得出来,他专用的寄存器要多于 IRQ 的,所以也的确是要 Fast 一些;

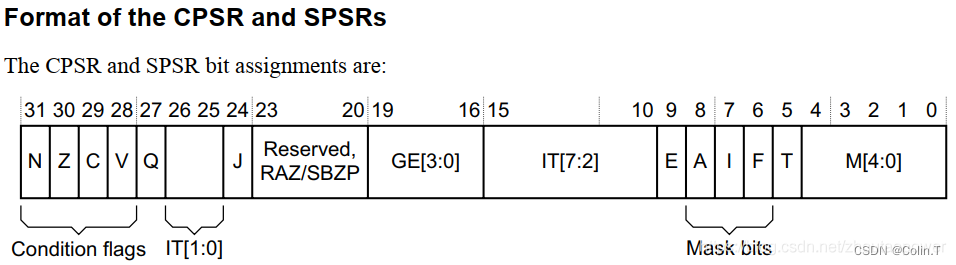

(4)特殊寄存器

ARMv7-A 还有一个特殊寄存器叫:程序状态寄存器 CPSR(Current Program Status Register),再进入异常之前,当前的 CPSR 被保存到 SPSR (Saved Program Status Register)中;

CPRS 在用户层叫做 APSR,APSR 只是 CPSR 寄存器中被截取的一部分,因为在用户层,并不是所有的 CPSR 的位都可以访问;

| Field | 作用 |

|---|---|

| N | ALU返回运算结果是否为负数 |

| Z | ALU返回运算结果是否为0 |

| C | ALU运算是否发生进位 |

| V | ALU运算是否发生溢出 |

| Q | cumulative saturation |

| J | ARM是否处于 Jazelle 状态 |

| E | 控制 load/store 字节序,E=1表示大端模式,E=0表示小端模式 |

| A | disables asynchronous aborts,User模式不能操作 |

| I | 使能/禁能 IRQ,User模式不能操作,I=1表示禁止 IRQ,I=0表示使能 IRQ |

| F | 使能/禁能 FIQ,User模式不能操作,F=1表示禁止 FIQ,I=0表示使能 FIQ |

| T | ARM和Thumb状态标志位 |

| GE | 用于某些SIMD(Single Instruction, Multiple Data)指令 |

| M[4:0] | 处理器模式:FIQ,IRQ,ABT,SVC,UND,MON,HYP。User模式不能操作 |

| IT[7:0] | IT7:2:和IT1:0一起组成IT[7:0],表示IF-THEN指令的执行状态 |

[28-31]:条件码

M[4:0]:处理器模式的Encoding

Armv8-A

Armv8-A架构是针对应用框架的最新一代Arm架构。ARMv8架构继承了ARMv7与之前处理器技术的基础,除了对现有的16/32bit的Thumb2指令支持外,也向前兼容了现有的A32(ARM 32bit)指令集,基于64bit的AArch64架构,除了新增A64(ARM 64bit)指令集外,也扩充了现有的A32(ARM 32bit)和T32(Thumb2 32bit)指令集,另外还新增加了CRYPTO(加密)模块支持。

寄存器

为了向前兼容Armv7,Armv8-A支持两种Execution State,分别是AArch32和AArch64,两种Execution State有如下区别:

| AArch32 | AArch64 |

|---|---|

| 提供13个32bit通用寄存器R0-R12,一个32bit PC指针 (R15)、堆栈指针SP (R13)、链接寄存器LR (R14) | 提供31个64bit通用寄存器X0-X30(W0-W30),其中X30是程序链接寄存器LR |

| 提供一个32bit异常链接寄存器ELR,用于Hyp mode下的异常返回 | 提供一个64bit PC指针、堆栈指针SPx 、异常链接寄存器ELRx |

| 提供32个64bit SIMD向量和标量floating-point支持 | 提供32个128bit SIMD向量和标量floating-point支持 |

| 提供两个指令集A32(32bit)、T32(16/32bit) | 定义ARMv8异常等级ELx(x<4),x越大等级越高,权限越大 |

| 兼容ARMv7的异常模型 | 定义一组PSTATE,用以保存PE(Processing Element)状态 |

| 协处理器只支持CP10\CP11\CP14\CP15 | 没有协处理器概念 |

通用寄存器

在ARM64架构下,CPU提供了33个寄存器, 其中前31个(0~30)是通用寄存器 (general-purpose integer registers)。

| 寄存器 | 说明 |

|---|---|

| X0寄存器 | 用来保存返回值(或传参) |

| X1 ~ X7 寄存器 | 用来保存函数的传参 |

| X8寄存器 | 也可以用来保存返回值 |

| X9 ~ X28寄存器 | 一般寄存器,无特殊用途 |

| X29(FP)寄存器 | 用来保存栈底地址 |

| X30 (LR)寄存器 | 链接寄存器,用来保存返回地址 |

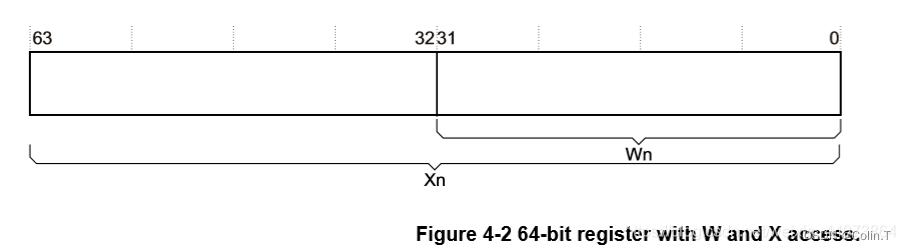

每个AArch64 64位通用寄存器X0-X30都有一个对应的32位寄存器,Wn寄存器是Xn寄存器的低32位,读Wn寄存器时会保持Xn寄存器的高32位不变,如果写W寄存器时,会将X寄存器的高32位设为0。

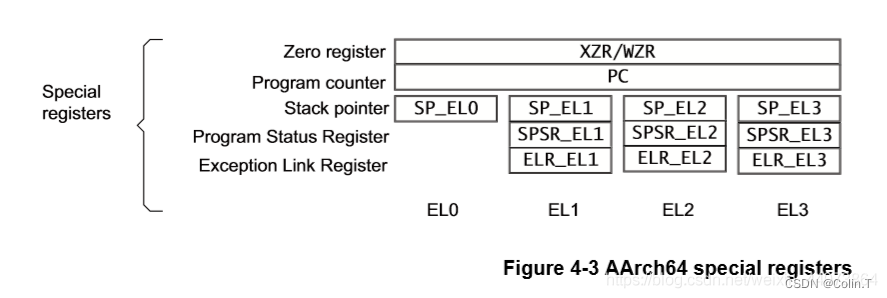

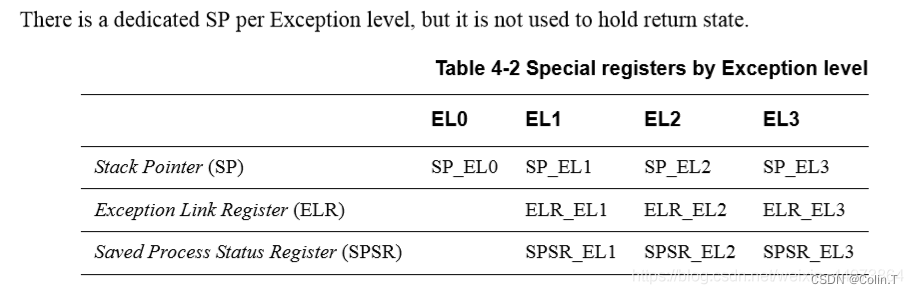

特殊寄存器

除了31个通用寄存器,还有几个特殊的寄存器:

1、zero register:写操作被忽略,读操作都返回0;

2、SP/WSP:当前栈指针;

3、PC program counter:ARMv7指令集使用通用寄存器R15作为PC,直接操作PC可以做一些机智的编程操作,但是ARMv8不能直接进入PC,这使返回更好预测,并且使ABI规范更加简单;

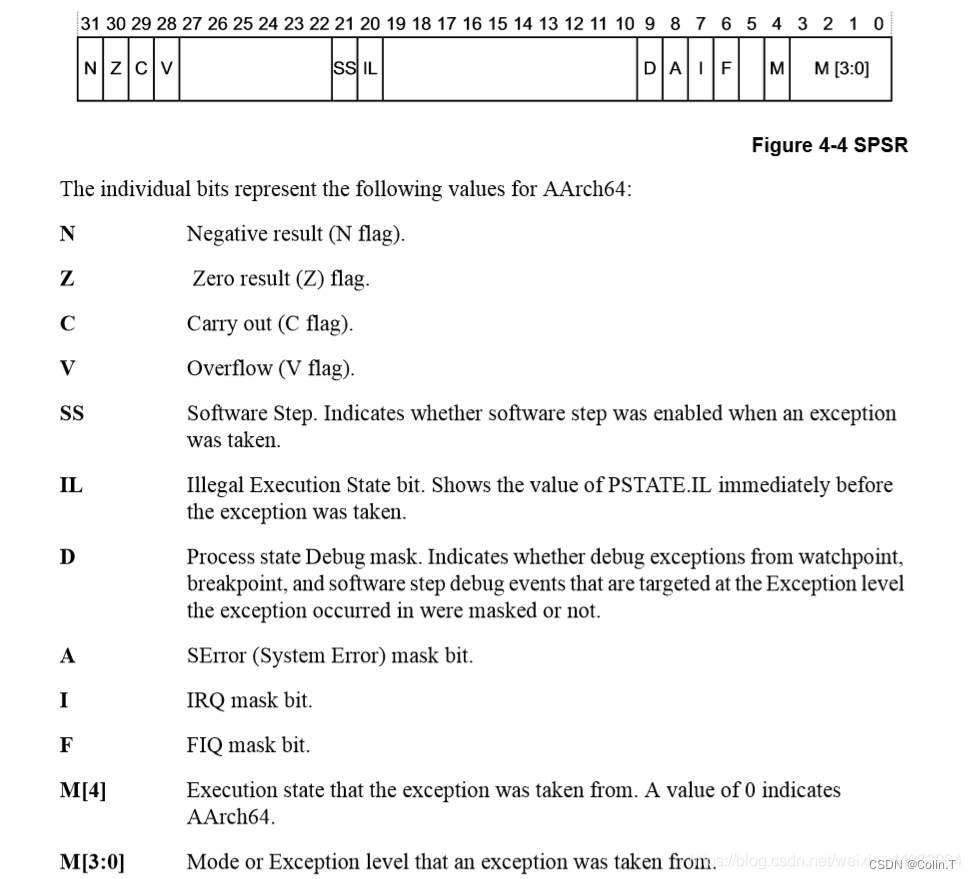

4、ELR / SPSR:当armV8执行在AArch64,每个ELn异常返回状态取决于ELR和SPSR

ELR: exception link register 保存exception返回地址

SPSR: saved processor state register 执行exception前保存当前的processor state, 执行exception完返回时restore

在ARMv8中,如果异常发生在EL1,就使用SPSR_EL1,如果发生在EL2, 使用SPSR_EL2,如果发生在EL3, SPSR_EL3使用

ELR 和SPSR时成对的,其和对应的ELn相关

5、SP 每个 exception level 都有对应的 SP:

Armv8有32个 128bit的浮点寄存器 V0-V31. 这32个寄存器用来处理标量浮点预算和NEON指令。

指令集

A64指令的编码是固定的32bits;A32指令的编码也是固定的32bits;T32指令编码是可变长的16bits、32bits。

ARM指令使用的是 三地址码 , 它的格式如下:

{} {S} , , <shifter_operand>

opcode:操作码,也就是助记符,操作码,也就是助记符,说明指令需要执行的操作类型

cond:指令执行条件码,在编码中占4bit,0b0000 -0b1110

S:条件码设置项,决定本次指令执行是否影响PSTATE寄存器响应状态位值

Rd:目标寄存器,A64指令可以选择X0-X30 or W0-W30

Rn:第一个操作数的寄存器,和Rd一样,不同指令有不同要求

shifter_operand:第二个操作数,可以是立即数,寄存器Rm和寄存器移位方式(Rm,#shit)

指令分类

- 跳转指令:条件跳转、无条件跳转(#imm、register)指令;

- 异常产生指令:系统调用类指令(SVC、HVC、SMC);

- 系统寄存器指令:读写系统寄存器,如 :MRS、MSR指令 可操作PSTATE的位段寄存器;

- 数据处理指令:包括各种算数运算、逻辑运算、位操作、移位(shift)指令;

- load/store内存访问指令:load/store {批量寄存器、单个寄存器、一对寄存器、非-暂存、非特权、独占}以及load-Acquire、store-Release指令 (A64没有LDM/STM指令);

- 协处理器指令:A64没有协处理器指令。

常见指令

add:将某一寄存器的值和另一寄存器的值 相加 并将结果保存在另一寄存器中

add x0, x0, #1 ; 将寄存器 x0 的值和常量 1 相加后保存在寄存器 x0 中

add x0, x1, x2 ; 将寄存器 x1 和 x2 的值相加后保存到寄存器 x0 中

add x0, x1, [x2] ; 将寄存器 x1 的值加上寄存器 x2 的值作为地址,再取该内存地址的内容放入寄存器 x0 中

mov:把一个寄存器的值(要能用立即数表示)赋给另一个寄存器,或者将一个常量赋给寄存器,将后边的量赋给前边的量

mov R1, R0 ; 将寄存器R0的值传送到寄存器R1

mov PC, R14 ; 将寄存器R14的值传送到PC,常用于子程序返回

mov R1, R0, LSL#3 ; 将寄存器R0的值左移3位后传送到R1(即乘8)

movs PC, R14 ; 将寄存器R14的值传送到PC中,返回到调用代码并恢复标志位

sub:用于把操作数1减去操作数2,并将结果存放到目的寄存器中。操作数1应是一个寄存器,操作数2可以是一个寄存器,被移位的寄存器,或一个立即数。该指令可用于有符号数或无符号数的减法运算

sub R0, R1, R2 ;R0 = R1 - R2

sub R0, R1, #256 ;R0 = R1 - 256

sub R0, R2, R3, LSL#1 ;R0 = R2 - (R3 << 1)

异常模型及处理器模式

异常模型

Armv8有四种Exception Level,分别是EL0,EL1,EL2,EL3

| Exception | Level |

|---|---|

| EL0 | Application |

| EL1 | Linux kernel- OS |

| EL2 | Hypervisor |

| EL3 | Secure Monitor |

| Security | |

| Non-secure | Non-secure EL0/EL1/EL2, 只能访问Non-secure memory |

| Secure | Secure EL0/EL1/EL3, 可以访问Non-secure memory & Secure memory |

注意处理器异常等级有如下规则:

- ELx(x<4),x越大等级越高,执行特权越高

- 执行在EL0称为非特权执行

- EL2 没有Secure state,只有Non-secure state

- EL3 只有Secure state,实现EL0/EL1的Secure和Non-secure之间的切换

- EL0 & EL1 必须要实现,EL2/EL3则是可选实现