本文针对7K325T芯片,详细讲解硬件连接需要注意的技术点,可以作为设计和检查时候的参考文件。为了方便使用,按照Bank顺序排列,包含配置Bank、HR Bank、HP Bank、GTX Bank、供电引脚等。

参考文档包括DS182、UG470、UG475、UG476等。

目录

Bank 0(配置Bank)

电源

XADC

JTAG

配置

Bank 14(HR BANK)

电源

普通IO

配置IO

时钟IO

其他IO

Bank 15(HR BANK)

电源

普通IO

配置IO

时钟IO

其他IO

Bank 12/13/16/17/18(HR BANK)

电源

普通IO

时钟IO

其他IO

Bank 32/33/34(HP BANK)

电源

普通IO

时钟IO

其他IO

Bank 115(GTX BANK)

校准

时钟

数据

Bank 116/117/118(GTX BANK)

GTX电源

非GTX电源

Bank 0(配置Bank)

电源

1. VCCO_0:

代表Bank 0中所有IO所遵循的电平标准,可连接3V3/2V5/1V8/1V5等电压。

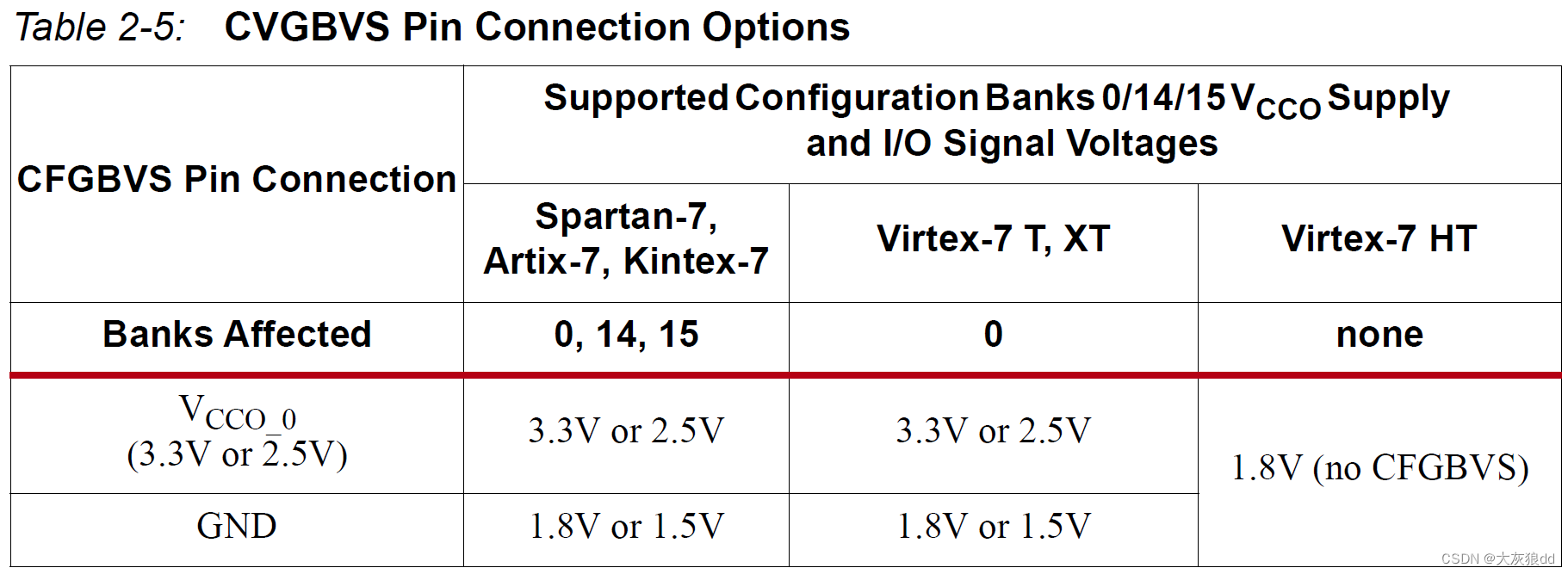

当VCCO_0=3V3或2V5时,CFGBVS也必须和VCCO_0保持一致;当VCCO_0=1V8或1V5时,CFGBVS需要接GND,CFGBVS一般不需要上下拉电阻,直连就可以。

Virtex-7 FPGA比较特殊,非HT(Virtex-7 HT)器件的Bank 0和其他S/A/K系列相同,而Bank 14/15是HP Bank,仅支持1V8以下电平;Virtex-7 HT器件无CFGBVS引脚,仅支持1V8电平。

实际应用中,分两种情况:

- 主SPI:该模式下,FPGA通过CCLK_0输出时钟给FLASH,考虑到当前SPI FLASH以3V3电源为主,Bank 0建议也接3V3,这样能省去电平适配带来的麻烦;

- 主BPI:该模式下,BPI FLASH和Bank 0之间没有连接关系,只要能找到1V8/1V5供电的BPI FLASH,理论上Bank 0可以连接1V5/1V8/2V5/3V3等电压;

- 不管是主SPI还是主BPI,都会涉及到Bank 14/15,此时Bank 14/15的电源需要和Bank 0保持一致,这一点需要注意。

2. VCCBATT_0:

该引脚和配置文件加密功能有关,用到该功能时,该引脚需要接外部电池,防止器件掉电后加密功能也失效,DS182中规定电压范围为1V0~1V89,并没有明确规定是1.8V、1.5V还是1.2V;但是用不到加密功能时,XILINX建议接入VCCAUX(1V8)或GND。结合来看,电池电压也应和VCCAUX保持一致,即1V8。

Spartan-7的7S6/7S15不支持加密功能,该引脚需要接VCCAUX或GND。

XADC

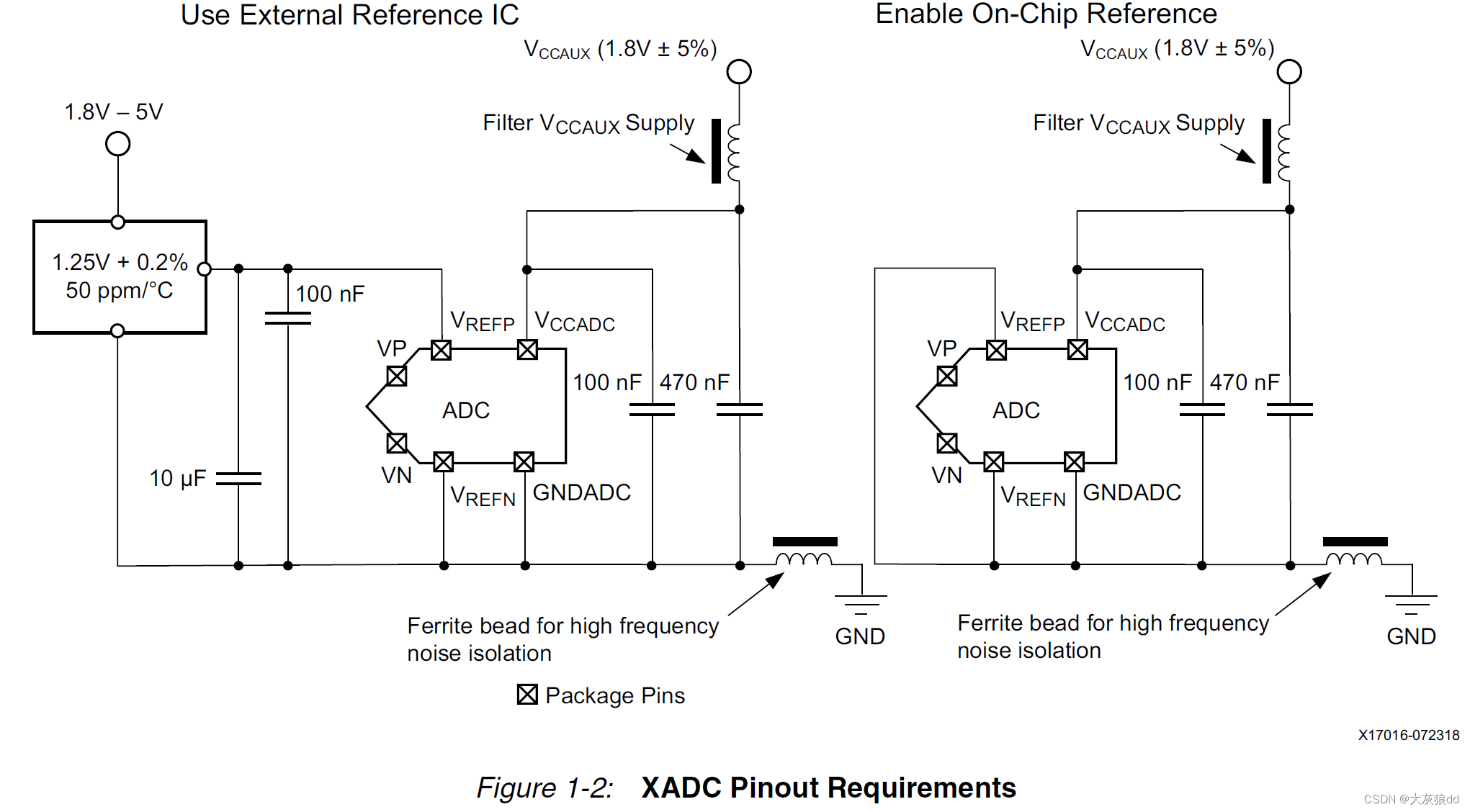

- VCCADC_0:XADC的模拟电源引脚,电压和VCCAUX保持一致,建议单独供电或通过滤波电路(电感等)连到VCCAUX上,不使用时也需要接VCCAUX;

- GNDADC_0:XADC的模拟接地引脚,可以通过磁珠连接到系统GND,也可以连接到系统的模拟地上(此时不再需要额外的磁珠,系统模拟地应已处理),不使用时也需要接GND;

- VP_0/VN_0:XADC专用差分输入引脚(专用是对比其他XADC模拟输入来说,该引脚不能用作普通IO,其他的都可以),不使用时接GND;

- VREFP_0:电压基准,可接入外部1.25V高精度基准,也可采用内部基准电压(此时接GNDADC_0),不用XADC时也接GNDADC_0;

- VREFN_0:电压基准GND,采用外部基准时接入外部基准电压GND,采用内部基准时接入系统GNDADC_0,不用XADC时也接GNDADC_0;

- DXP_0/DXN_0:内部温度二极管,结合外部温度监控电路可实现对FPGA芯片结温的监控,不用时接系统GND。

JTAG

- TCK_0:测试时钟输入,连外部仿真器,建议加防静电措施(TVS管),含驱动电路时,注意输入弱上拉(例如10kΩ),保持未接仿真器时为高电平;

- TMS_0:测试模式输入,其他同TCK_0;

- TDO_0:测试数据输出,连外部仿真器,级联时连接后级TDI_0引脚,建议加防静电措施(TVS管);

- TDI_0:测试数据输入,连外部仿真器,级联时链接前级TDO_0引脚,建议加防静电措施(TVS管);

大多数应用中,不会涉及到多个FPGA,即使涉及到了,也不会级联,而是每个器件都会预留一个JTAG调试口。若涉及到多个FPGA级联的情况,常规的做法是多个FPGA共用TCK/TMS,前级TDO接后级TDI,需要考虑驱动能力、走线等因素。

配置

配置引脚的接法和器件采用的配置模式相关,当前常用的配置模式是主SPI和主BPI模式,主串、主并、从串、从并模式基本上不用,仅介绍两种常用模式下的连接方法。

- CCLK_0:主SPI模式下,该引脚为时钟输出引脚,连接SPI FLASH的时钟输入引脚,需要考虑信号完整性(源端匹配+上下拉);主BPI模式下不使用,可以悬空;

- INIT_B_0:该引脚刚上电时为低电平,直到初始化完成,变为高阻态,需要外接上拉电阻到VCCO_0(≤4.7kΩ),变为高电平后开始采样M[2:0]引脚,执行后续操作;该引脚可以由外部控制拉低,以推迟FPGA配置过程;在主BPI场合下,可以将该引脚接到BPI FLASH的/RESET引脚上,当检测到配置数据错误时,触发BPI FLASH复位;

- PROGRAM_B_0:该引脚上的低电平表示需要重新配置FPGA,需要外接上拉电阻到VCCO_0(≤4.7kΩ),通常可以外接按键来提供手动复位功能;

- CFGBVS_0:高电平(VCCO_0)代表2V5/3V3电平(Bank 0以及配置期间的Bank 14/15),低电平(GND)代表1V8/1V5电平标准;

- DONE_0:该引脚上的高电平代表配置完成,内部含10kΩ上拉电阻(仅7系列),外部可以不接330Ω上拉电阻(仅7系列),考虑到兼容之前系列FPGA,也可以保留该外部上拉电阻;

- M0_0/M1_0/M2_0:决定了FPGA的启动模式,直连VCCO_0/GND或通过上下拉电阻连接(≤1kΩ),主SPI对应001,主BPI对应010,JTAG对应101,建议预留JTAG模式(101),FPGA起不来又连不上仿真器的情况下可以用来恢复。

Bank 14(HR BANK)

电源

VCCO_14:可接1V2/1V5/1V8/2V5/3V3等多种电压,但是主SPI/主BPI模式下配置过程涉及到该Bank上的某些引脚,需要和VCCO_0保持一致。

普通IO

普通IO指的是该引脚只做IO用,没有其他功能复用情况,Bank 14共有两个普通IO,IO_0_14和IO_25_14,即第一个和最后一个。

配置IO

仅针对主SPI/主BPI情况说明,其他情况基本上用不到。

- D[15:00]:主SPI x1/x2模式用到D[01:00](MOSI/DIN),主SPI x4模式用到D[03:00],主BPI模式下用到D[15:00];

- A[15:00]:主SPI模式下不使用,主BPI模式下用作低16位地址线;

- PUDC_B:配置期间IO内部上拉使能引脚,低电平使能上拉,高电平禁止上拉,可以直连或通过上下拉电阻(≤1kΩ)连接,一般选择上拉,以保证配置期间IO为三态,不输出任意波形;

- EMCCLK:外部时钟输入引脚,主SPI模式下,可以切换替代CCLK_0功能,达到提速的目的,使用时需要外接晶振;

- FCS_B:主SPI/主BPI模式下,作为片选功能连接到FLASH的/CS引脚,需要外接上拉电阻(≤4.7kΩ)到VCCO_14;

- RDWR_B:仅并行模式下使用,主SPI/BPI模式下不使用;

- DOUT_B/CSO_B:级联功能引脚,主SPI x1级联模式下(x2/x4模式不支持级联),连接后级的DIN引脚,组成菊花链;主BPI级联模式下,连接后级的CSI_B引脚,需要外接330Ω上拉到VCCO_14上(主SPI x1级联模式不需要外接上拉电阻);

- CSI_B:仅并行级联模式下使用,主SPI/主BPI模式下不使用;

特别说明下,主BPI级联模式中,第一个器件为主BPI模式,后级所有器件都为从并模式,首器件通过FCS_B连接外部FLASH(不用CSI_B),将CSO_B连到后级CSI_B中,后级其他器件通过CSI_B和CSO_B组成菊花链。

时钟IO

- SRCC:共2组4根时钟输入,可驱动BUFIO/BUFR/BUFG;

- MRCC:共2组4根时钟输入,可驱动BUFIO/BUFR/BUFMR/BUFG。

其他IO

- DQS:DDR专用DQS引脚;

- VREF:DDR专用电压参考引脚。

Bank 15(HR BANK)

电源

VCCO_15:主SPI模式不涉及该Bank,可接1V2/1V5/1V8/2V5/3V3等多种电压;主BPI模式配置过程涉及该Bank,需要和VCCO_0保持一致。

普通IO

共有三个普通IO,IO_0_15/IO_L6P_T0_15/IO_25_15。

配置IO

- ADV_B:主SPI模式下不使用;主BPI模式下,针对支持地址有效功能的FLASH,连接到该FLASH的ADV引脚,外接上拉电阻(≤4.7kΩ)到VCCO_15,针对不支持地址有效功能的FLASH,不要使用该引脚(?);

- A[28:16]:主SPI模式下不使用;主BPI模式下,用作高13-bit地址线;

- FOE_B:主SPI模式下不使用;主BPI模式下,连接BPI FLASH的/OE引脚,外接上拉电阻到VCCO_15(≤4.7kΩ);

- FWE_B:主SPI模式下不使用;主BPI模式下,连接BPI FLASH的WE引脚,外接上拉电阻到VCCO_15(≤4.7kΩ);

- RS1/RS0:仅在使能回读模式或远程重配置的情况下才会用到,还没见到哪个应用中用到过。

时钟IO

同Bank 14。

其他IO

- AD[n]P/N:XADC的模拟输入引脚;

- DQS:DDR专用DQS引脚;

- VREF:DDR专用电压参考引脚。

Bank 12/13/16/17/18(HR BANK)

电源

VCCO_12/13/16/17/18:可接1V2/1V5/1V8/2V5/3V3等多种电压,根据需要选择。

普通IO

共32个普通IO。

时钟IO

同Bank 14。

其他IO

同Bank 14。

Bank 32/33/34(HP BANK)

电源

VCCO_32/33/34:可接1V2/1V5/1V8等多种电压,根据需要选择。

普通IO

共30个普通IO(少了两个VRP/VRN引脚)。

时钟IO

同Bank 12,4个SRCC+4个MRCC。

其他IO

包含DQS/VREF/VRP/VRN等DDR/DCI专用引脚。

Bank 115(GTX BANK)

校准

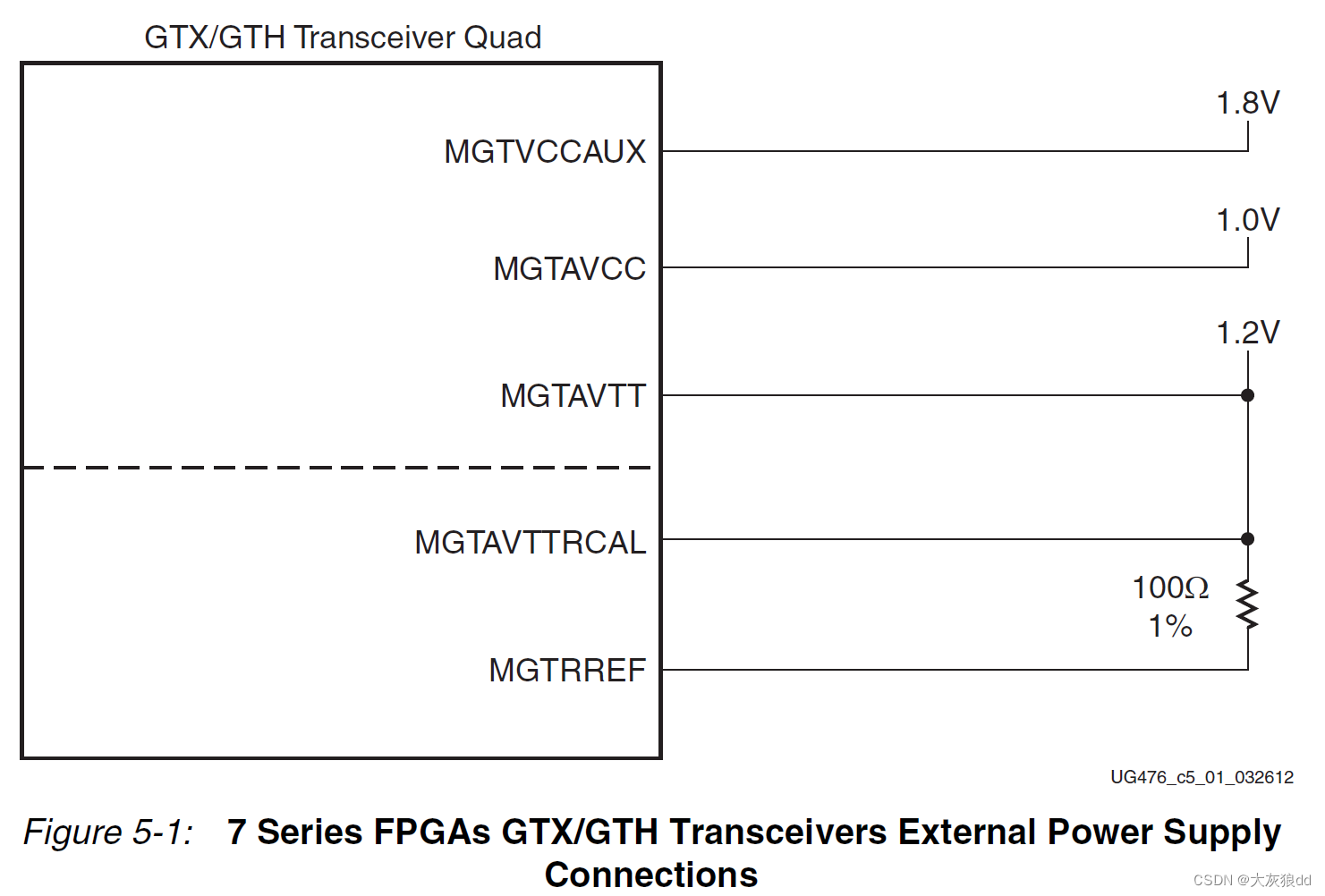

MGTAVTTRCAL和MGTRREF,用于GTX内部校准,MGTAVTTRCAL直连1.2V(同MGTAVTT),MGTRREF通过100Ω电阻连接MGTAVTTRCAL。若不用GTX功能,应连接GND。

时钟

含两组差分时钟引脚,MGTREFCLK[n]P/N,接入外部差分时钟(需要电容耦合)。若不用GTX功能,应悬空。

数据

含4组差分收发引脚,MGTXTXP/N[n]、MGTXRXP/N[n],使用时需要电容耦合。若不使用GTX功能,接收端可以选择悬空(偏置)或连GND(未偏置),发送端应悬空。

Bank 116/117/118(GTX BANK)

无校准引脚,其他同Bank115。

GTX电源

- MGTAVCC:1.0V(≤10.3125GHz),1.05V(>10.3125GHz);

- MGTAVTT:1.2V;

- MGTVCCAUX:1.8V;

- 上下电时序要求:先上VCCINT和MGTAVCC(两者之间无特殊要求,可以同时上),然后上MGTAVTT,MGTVCCAUX无特殊要求,下电时序和上电时序相反;

- 不使用GTX功能时,供电引脚可以悬空或连GND。

非GTX电源

- VCCINT:1.0V/0.95V(-2LI)/0.9V(-2LE);

- VCCBRAM:1.0V/0.95V(-2LI)/0.9V(-2LE);

- VCCAUX:1.8V;

- VCCAUX_IO:1.8V/2.0V;

- 上下电时序要求:VCCINT和VCCBRAM先上电(建议同时上电),然后上电VCCAUX/VCCAUX_IO,最后上电VCCIO(含在Bank各章节中),下电时序和上电相反。