引言

随着高性能计算机的发展,在许多领域对系统的带宽有着越来越高的要求。因此,为了实现高速数据传输,采用新的总线技术已经成为必然的发展趋势。2005年PICMG 提出了CPCI-E 协议,开辟了新型高速总线。CPCI-E 实质上是高速PCI-E 总线基于欧卡规格的实现,在解决高带宽问题的同时,兼具了高可靠性和坚固性,并且支持模块化和热插拔。CPCI-E系统很适合各种需要高性能、高可靠性的领域。

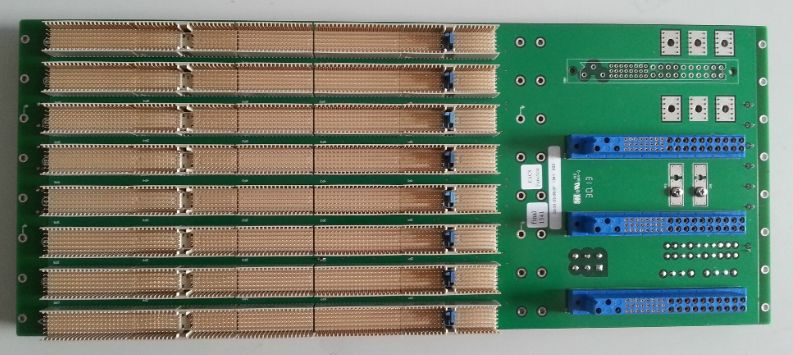

在CPCI-E 系统中往往采用背板实现各功能板的互连,因此背板设计的好坏直接影响系统的适用性、兼容性和可靠性。本文旨在设计一种CPCI-E背板,使其为高速CPCI-E 系统提供丰富的互连接口,并且对传统CPCI 系统具备一定兼容性。然而,高速率传输带来了以前低速率传输中可以忽略的信号完整性问题,例如信号在传输线上的反射、串扰、延迟、衰减,以及电源完整性问题等。这些问题成为影响信号质量,从而影响系统的稳定性和可靠性的因素。

1 背板原理图与布局设计

为了使此背