1.1 处理器中指令的交付、取消、冲刷

1.1.1 指令交付、取消和冲刷

影响指令交付的因素:

- 中断、异常以及分支预测指令造成流水线冲刷

- ARM中存在条件码,只会取消自己不会造成流水线冲刷

交付的位置

- 执行阶段()完成分支预测之后

- 写回阶段(有的指令需要多个周期才可以写回)

- 重排序交付队列。对于高性能的超标量处理器指令往往乱序执行乱序写回,写回往往会使用ROB或者纯物理存储器。相应处理器往往会配备一个较深的重排序交付队列用来花村乱序执行的指令。

RISC-V没有条件码,也没有异常指令不用担心硬件实现上的异常。

只需要处理以下两种情形。

- 分支预测指令错误预测造成的后续指令流消失

- 中断和异常造成的后续指令流取消。

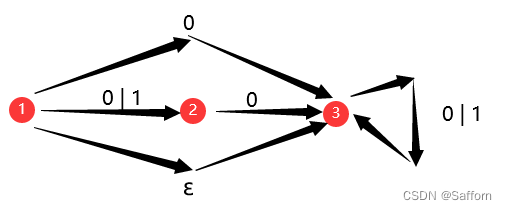

1.1.2 分支预测指令的处理

IFU中主要是处理以下几种带条件的跳转指令。

- beq:若两个整数操作数相等则跳转。

- bne:若两个整数不相等则跳转。

- blt:若第一个有符号数小于第二个有符号数,则跳转

- bltu:若第一个无符号数小于第二个无符号数,则跳转

- bge

- bgeu

E203都使用了**静态预测,即向后跳转预测为跳转,向前跳转预测为不跳转。**是否真的跳转需要ALU计算得到。如果预测的结果和真实的结果相同则交付,否则会进行流水线冲刷。

1.1.3 多周期执行的指令的交付

交付在执行阶段可以完成,写回需要在后续的周期内写回