【流程】

2022.8.18 一面

2022.8.25 二面

面经分享

一面

1.讲项目

2.笔试的除法器怎么实现的?

讲了流水线乘法器,用移位的方法,面试官说还有查表,逼近的办法

3.PAPR算法被抑制的点在接收机怎么处理?

我一直觉得是不用处理的,具体原理面试官也不懂通信,感觉解释的不好

4.怎么做信噪比估计?

估计处用h做和同步处用相关做两种方法,然后说一下具体原理

5.FFT ip核内部是怎么实现的?基2基4有什么区别?

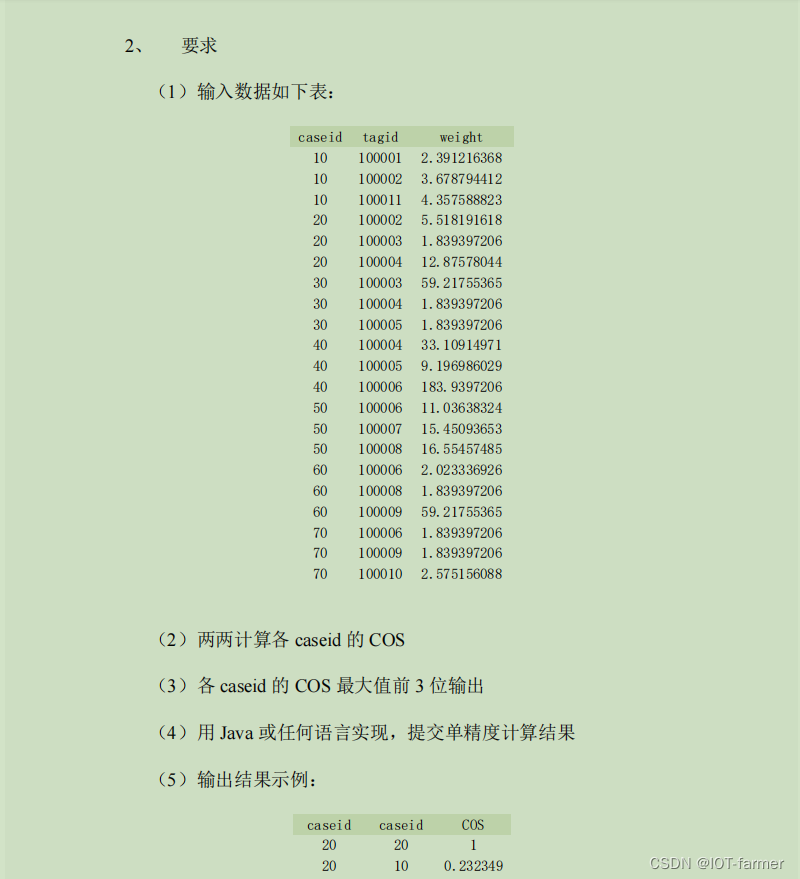

6.a&b&c&d要用多少LUT,怎么实现

可以用二输入LUT搭

7.六个单比特相加要用多少六输入LUT

听错题目了!!!但是面试官不给我机会说了

二面

1.完整的讲了一遍某一个项目(我做的部分)

2.怎么验收性能?怎么验收抗干扰性能?

3.怎么解决时序违例?

4.为什么扇出高会引起时序违例?

我说是单元的负载/驱动能力不够,在面试官提示下说扇出高有些路径就会跨很多单元,可能布线时延会比较长。

5.怎么计算setup/hold slack?

6.multicycle怎么看两个沿?然后大概手撕了一下multicycle的tcl代码

一般来说setup向后延N个clk,hold得回推N-1个clk,然后具体分析一下就行

7.用MUX搭一个与门

8.怎么实现一个延迟模块(输入20bit数据及动态可配置的延时)?如果延迟500突然变200怎么做?

异步fifo和移位寄存器两种方法。将输入的延时打一拍并相减,然后如果不等于0代表变化,然后给状态机和fifo复位。(听面试官意思还有其他方法,忘记问了)

9.项目中怎么用的AXI,说一下AXI写数据过程

10.介绍一下FPGA底层资源

11.介绍一下锁相环

12.ZYNQ启动流程

一种是通过SDK等工具启动,一种是通过ROM自启动,具体流程网上都有

反问:

因为大家都挺忙的,所以进来后主要还是靠资料自学,每周会开周会分享知识

总结

个人还是更想做IC,不过禾赛毕竟国内激光雷达两大巨头之一(知乎上有看过一些文章说激光雷达可能过几年还得洗牌一次),听说挺累的但是总包挺高的,两面难度都不小,感觉挺注重底层和原理的,如果做FPGA的话还是很好的选择。