作者:小道萧兮 未经授权 不得二次转载

链接:https://www.jianshu.com/p/0aa5c09b2a6b

一、如何存储数据

由于保存数据的重要性,科学家一直在思考,在电路中使用何种方式可以保存数据。

如果使某个器件一直输出高电平,那不就是 1 了吗?一直输出低电平,那不就是 0 了吗?而且还要可以自由切换 0 和 1。

接下来,内存条闪亮登场。

二、RAM

内存条还有一个更专业的名字:RAM (Random Access Memory) 随机存储器,因为可以随意读写任意位置的数据。

现在计算机基本上都是二进制的,不管什么样的数据或者代码指令,在我们这里都是一串串的 0 和 1 的比特位。

为了存储这一个比特位,曾经有两种电路方案摆在先辈们的面前,第一种是静态方案:

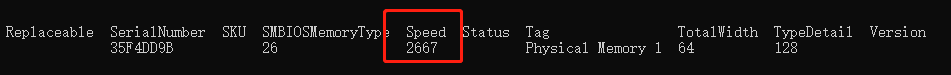

是不是有点复杂?我也觉得。这种电路方案的好处是可以稳定的维持在 0 和 1 之间的某个状态,所以叫静态 SRAM (Static Random Access Memory)。

但是需要用到的晶体管太多了,一个比特位就要用好几个晶体管,16GB 那得用多少才够啊,成本太高了,造出来我们的个头肯定会特别大,主板上空间这么局促,哪里装得下啊。

还有第二种方案:

这样是不是简单了许多?只通过一个电容器的电荷就能决定这是一个 1 还是一个 0,这样就存储了 1bit。

在每一个存储芯片里,这样的比特位存储单元都有很多,例如一个 16G 的内存条有 137438953472 bit,也就是有 137438953472 个这样的电容。

但这种电路方案有个毛病,就是里面的那个电容会“漏电”,电容中的电荷会慢慢消失,电压也就变小了,这样就没办法区分这是表示的 1 还是 0 了。

为了解决这个问题,必须得周期性的去给它们充电,才能维持数据的稳定,这叫动态数据刷新,所以这种方案叫 DRAM (Dynamic Random Access Memory)。

三、内存控制器

当我们需要读取数据时,要访问哪个 bit 位,通过芯片号、bank 号、行地址、列地址,就可以了。

是不是有点麻烦,这些内部细节应该封装一下,提供给一个简单接口就是了,于是 内存控制器 登场了。

内存控制器就像一个中介,位于 CPU 与 内存条之间。

内存存储数据的电路单元中,电容经常漏电,需要定时刷新,按照规定,最多 64ms 就得要刷新一次,这数据刷新的工作就由内存控制器管理。

内存条的数据存储在每一个存储芯片之上,每一个芯片里面又分了很多个分片,每个分片里面又有很多的比特位存储格子。想要访问哪个比特位,就得指定对应的芯片、对应的分片、对应格子的行地址和列地址。

CPU这边想要访问数据,肯定不想这么麻烦,所以内存控制器就派上用场了。

用 bit 作为读写单元太麻烦了,咱们按 8 bit 为一组,叫做一个字节 byte,CPU 统一给内存的存储空间编址,以后要读取数据的时候呢,就把地址交给内存控制器,再告诉内存具体是读写哪个芯片哪个分片的哪些位置。

以后只需要一个地址,内存控制器就转换成具体的数据存储位置,去读取内存,再由内存完成读写操作就可以了。

由于内存控制器的重要性,现在,内存控制器已经集成到了 CPU 内部,成为了 CPU 的一份子了。

随着 CPU 的发展,CPU 的速度越来越快,开始嫌内存慢了,要说慢,硬盘那可比内存慢多了!于是在 CPU 内部又搞了个缓存出来,不用每次都问内存要数据,而是把一些常用的数据存储在 CPU 内部的缓存中。

只不过 CPU 内部的缓存不会太大,仅存放一些常用的数据,大部分数据还是需要通过内存进行读取。

猜您喜欢:

戳我,查看GAN的系列专辑~!

戳我,查看GAN的系列专辑~!

一顿午饭外卖,成为CV视觉的前沿弄潮儿!

最新最全100篇汇总!生成扩散模型Diffusion Models

ECCV2022 | 生成对抗网络GAN部分论文汇总

CVPR 2022 | 25+方向、最新50篇GAN论文

ICCV 2021 | 35个主题GAN论文汇总

超110篇!CVPR 2021最全GAN论文梳理

超100篇!CVPR 2020最全GAN论文梳理

拆解组新的GAN:解耦表征MixNMatch

StarGAN第2版:多域多样性图像生成

附下载 | 《可解释的机器学习》中文版

附下载 |《TensorFlow 2.0 深度学习算法实战》

附下载 |《计算机视觉中的数学方法》分享

《基于深度学习的表面缺陷检测方法综述》

《零样本图像分类综述: 十年进展》

《基于深度神经网络的少样本学习综述》