用原版vivi一直很不爽,于是便有个想法,想整个功能比较完备的出来.

于是开始搜索资料,baidu+google一番竟然发现早已有高手做出来了.自己正苦于拿不定主意到底用不用中断,正好拿高手的成果参考下,站在巨人的肩膀上,让我们走得更远.

于是便看代码...看代码...

在看tftp实现的时候,突然发现莫名其妙出来一个CS8900_BASE(0x19000300)这个地址.百思不得其解.

查询2410手册,cs8900手册...未遂,baidu下才知道,原来这个地址是有来头的.

转一篇别人的心得,以作自勉.

文章说明:calmarrow(lqm)原创

文章引自:http://piaoxiang.cublog.cn

开始研究tftp的实现方法,框架基本上是(从底层向上):媒介->IP->UDP->TFTP。其中,CS8900A就可以完成 PHY层和MAC层的所有工作,在媒介的上部应该还有一个LLC(logical link control),IP层也不仅仅包含IP协议,另外还需要有arp协议来确定host的mac地址。这个整体的框架后面详细介绍,下面先简略介绍 cs8900a的base address的确定方法和探测程序。 cs8900a实际上已经比较老了,性能和价格上都比不过dm9000,Linux 2.6的内核默认的是支持dm9000的以太网控制器。但是EDUKIT-III上仍然使用的是cs8900a,所以还是专心看cs8900a。要注意, 一是以学习的态度去研究,二是总结阅读datasheet的方法。 首先看看cs8900a到底是什么。

·Single-Chip IEEE 802.3 Ethernet Controller with Direct ISA-Bus Interface

·Maximum Current Consumption = 55 mA (5V Supply)

·3 V or 5 V Operation

·Industrial Temperature Range

· Comprehensive Suite of Software Drivers Available

·Efficient PacketPage Architecture Operates in I/O and Memory Space, and as DMA Slave

·Full Duplex Operation

·On-Chip RAM Buffers Transmit and ReceiveFrames

·10BASE-T Port with Analog Filters, Provides:

- Automatic Polarity Detection and Correction

·AUI Port for 10BASE2, 10BASE5 and 10BASE-F

·Programmable Transmit Features:

- Automatic Re-transmission on Collision

- Automatic Padding and CRC Generation

·Programmable Receive Features:

- Stream Transfer; for Reduced CPU Overhead

- Auto-Switch Between DMA and On-Chip Memory

- Early Interrupts for Frame Pre-Processing

- Automatic Rejection of Erroneous Packets

·EEPROM Support for Jumperless Configuration

·Boot PROM Support for Diskless Systems

·Boundary Scan and Loopback Test

·LED Drivers for Link Status and LAN Activity

·Standby and Suspend Sleep Modes

可以看出,cs8900a最重要的部分就是: ·ISA总线接口。这部分可以使外部的glue logic最小,简化编程,方便设计。 ·集成10BASE-T transmit and receive filters。这个加上专用变压器和RJ45对应的网线,就可以完成PHY层的功能。所以,硬件设计时不需要考虑PHY芯片了。at91rm9200集 成了以太网控制器,但是只是实现了MAC层的功能,所以需要扩展一个PHY层芯片完成网络接口的设计。 ·特殊的PacketPage架构。这实际上是cs8900a的特色,本来IO访问模式和memory访问模式是不同的,但是cs8900a屏蔽了这种差异,提供了一个统一的接口。这样在程序设计上,就可以使用统一的内存空间,来完成对cs8900a的操作。 ·EEPROM的支持。 现在就PacketPage架构和两种访问模式展开分析。

The CS8900A architecture is based on a unique, highly-efficient method of accessing internal registers and buffer memory known as PacketPage. PacketPage provides a unified way of controlling the CS8900A in Memory or

I/O space that minimizes CPU overhead and simplifies software. It provides a flexible set of performance features and configuration options, allowing designers to develop Ethernet circuits that meet their particular system requirements.

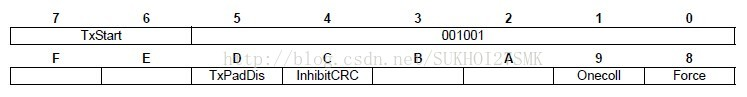

cs8900a有两种访问模式:IO模式和MEM模式。在IO模式下,cs8900a占用host最小的空间,仅仅16个字节(8个16bit的IO ports)。对地址空间紧张的系统来说,是一个合适的选择。在MEM模式下,cs8900a占用4K的空间,这是软件可以直接访问cs8900a的内部 寄存器,而且这4K的空间还分成了6个组成部分,具体可以参考datasheet的4.1.1部分。 cs8900a默认的是IO模式。在系统设计时,最好两种模式都要预留出来。原因有很多,首先,大多数情况下,MEM模式性能更高。因为ISA内存操作比 IO操作需要更少的时钟周期。所以最好有mem模式。其次呢,如果内存空间不可用,或者特殊操作时,IO模式是唯一的选择,而且如果使用了EEPROM, 板子发生故障时,EEPROM通常是空白的,为了对EEPROM编程,cs8900a也必须工作在IO模式。综上两种分析,系统设计还是要设计两种访问方 式为好。在ISA总线接口中,I/O空间和内存空间是独立寻址的,因此它们有各自不同的读写信号。但ARM体系中,I/O空间和内存空间是统一寻址。问题 就出来了,如果两种访问模式同时存在,那么如何区分是那种访问模式呢? 这个在硬件设计中是很普遍的问题。电路设计的时候用高位地址线(ADDR24)经过组合逻辑的译码来区分I/O空间和内存空间的读写。cs8900a只需 要20根地址现,而s3c2410的地址线是32条。那么可以让a[19:0]对应cs8900a的sa[19:0],拿出一条地址线A24来区分两种模 式。我画了原理图(注意,这仅仅是组合逻辑译码的一种,可以有其他的方式,这个就有硬件设计来决定了),如下:

通过上述的原理图,很容易明白,A24地址线为低时,为MEM模式。A24为高时,为IO模式。另外,cs8900a可以接在不同的bank。比如, EDUKIT接在nGCS3,基址是0x18000000,那么很明显,MEM模式的基地址是0x18000000,而IO模式的基地址是 0x18000000+(1<<24),也就是0x19000000。但是IO模式的基地址还没有最终结果呢。看datasheet,发现 packetpage偏移0x0020的地方为IO base address。在复位以后,如果没有EEPROM,那么该寄存器的值就是默认的0x0300。如果采用IO方式,那么初始时对应的该寄存器始终为 0x0300,前面得到的0x19000000再加上这个0x300才能找到最终8个16bitsIO ports的首地址。以后所有的操作都是通过这8个IO ports来进行的,包括访问MEM模式的那些寄存器。也就是MEM要访问那些内部寄存器,只是需要直接寻址就可以了,而IO模式则要先找到IO ports,然后通过这些IO ports来寻找到内部寄存器。显然,在效率上又差了一层。 下面看看EDUKIT-III的不同。EDUKIT-III采用了核心板+底板的设计方法。核心板SoC的A24最终经过电平转换芯片 74LVCH62245成为AB24,然后经过CPLD处理逻辑关系得到相应的IO和MEM控制信号。在CPLD中的逻辑处理跟上面原理图的处理是相同 的,不过实验箱需要处理的逻辑太多,用CPLD要好。这个也是看了好长时间的电路图才推断出来的。 由此可见base address的计算方法如下(假定选择nGCSn,对应bank的首地址为nGCS_ADDR) MEM模式: base address = nGCS_ADDR IO模式: base address = nGCS_ADDR + (1 << 24) + 0x0300. 当然,还有的默认前提就是使用了A24这条地址线来进行区分。当然,如果你不使用A24,只采用IO模式,不支持MEM模式,那么你的基地址完全可以是 nGCS_ADDR+0x0300。需要注意的是,在弄清楚原理的情况下,一定要看硬件设计如何,这样才能确定基地址。

备注:关于IO mode和memory mode的比较 I/O mode is 99.6% as fast as Memory mode. Also, since the CS8900A defaults to I/O and you don't need glue logic in most systems in I/O mode, Cirrus recommends I/O mode.