001

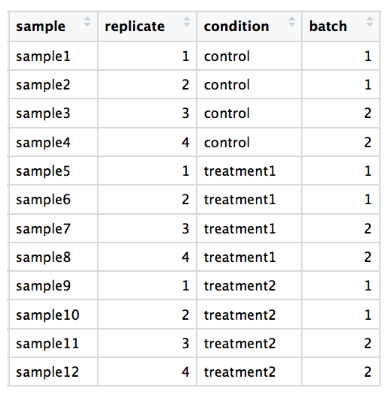

问题描述:

QuestaSim-64 vlog 10.6c Compiler 2017.07 Jul 26 2017

** Error: (vlog-13069) D:\1_projects\Questasim_prj\AHP2APB\apb_slv_trans.sv(6): near “uvm_sequence_item”: syntax error, unexpected IDENTIFIER.

** Error: D:\1_projects\Questasim_prj\AHP2APB\apb_slv_trans.sv(6): Error in class extension specification.

解决方案:

在代码开头加入

import uvm_pkg:😗;

`include “uvm_macros.svh”

结果:

compile显示no errors

002

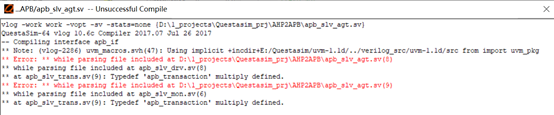

问题描述:

QuestaSim-64 vlog 10.6c Compiler 2017.07 Jul 26 2017

** Note: (vlog-2286) uvm_macros.svh(47): Using implicit +incdir+E:/Questasim/uvm-1.1d/…/verilog_src/uvm-1.1d/src from import uvm_pkg

** Error: D:\1_projects\Questasim_prj\AHP2APB\apb_slv_drv.sv(11): (vlog-2730) Undefined variable: ‘apb_transaction’.

** Error: (vlog-13069) D:\1_projects\Questasim_prj\AHP2APB\apb_slv_drv.sv(15): near “#”: syntax error, unexpected ‘#’, expecting IDENTIFIER or ‘=’.

解决方案:

把接口sv文件放在第一句

添加if,mem,trans,drv之后的代码调试正确

003按位与 逻辑与

[3:0] a,b;

& 按位;

&& 逻辑;

如果是一位的话,不影响;

2.头文件的问题

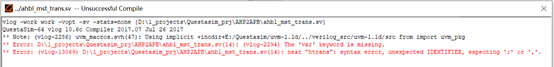

004

问题描述:

import和include一直错误的交叠在一起

解决方案:把所有的.sv放在一个pkg里面,在每一个class里面import即可,不需要多余的include,编译的时候只需要跑pkg.sv就可以了。

NOTE:import可以重复,include不能重复

005

问题描述:

在随机化和定义枚举类型的时候遇到问题

解决方案:

方法一:在pkg里面枚举声明需要的信号

方法二:在class里面枚举声明需要的信号