一、设置8086最小模式系统总线

8086系统中 BHE# 和 A0 引脚

AD15 ~ AD0 为地址/数据总线,T1 时用作地址总线的低 16 位,其他时间用作数据总线。

A19 ~ A16 / S6 ~ S3为地址状态总线,T1 时用作地址总线高 4 位,其他时间指示 CPU 状态信息。

34 号引脚 #BHE/S7 总线高允许 / 状态信号,T1 时作为高允许信号,#BHE 低电平时把读写的 8 位数据与 AD15 ~ AD8 联通,与 A0 结合以决定是高字节工作还是低字节工作。AD0 除了传输数据或地址信息还作为低 8 位数据的选通信号多字节的存取

奇地址:最低存储单元地址为奇数——即地址最低位 A0 = 1

偶地址:最低存储单元地址为偶数——即地址最低位 A0 = 0

8086 每个周期可以访问 16 位信息,变量地址为偶地址时,只需一个总线周期。如果变量为奇地址时,则要两个连续总线周期。8086 的存储空间时分成两个 512K 的存储体,偶存储体和奇存储体。低 8 位 D7 ~ D0 数据总线联接偶存储体,高 8 位 D15 ~ D8 数据总线联接奇存储体。偶地址存储时:一个 16 位字数据,高 8 位存储在奇存储体,低 8 位存储在偶存储体。奇地址存储时:相反。这样在读或写字数据时,偶地址存储方式:可以在一个总线周期完成读写。奇地址存储方式:读写时则有一个字节交换过程,也就是要用总线的高 8 位去读写字数据的低 8 位,再用总线的低 8 位读写字数据的高 8 位,需要两个总线周期才能完成一个字数据的读写。

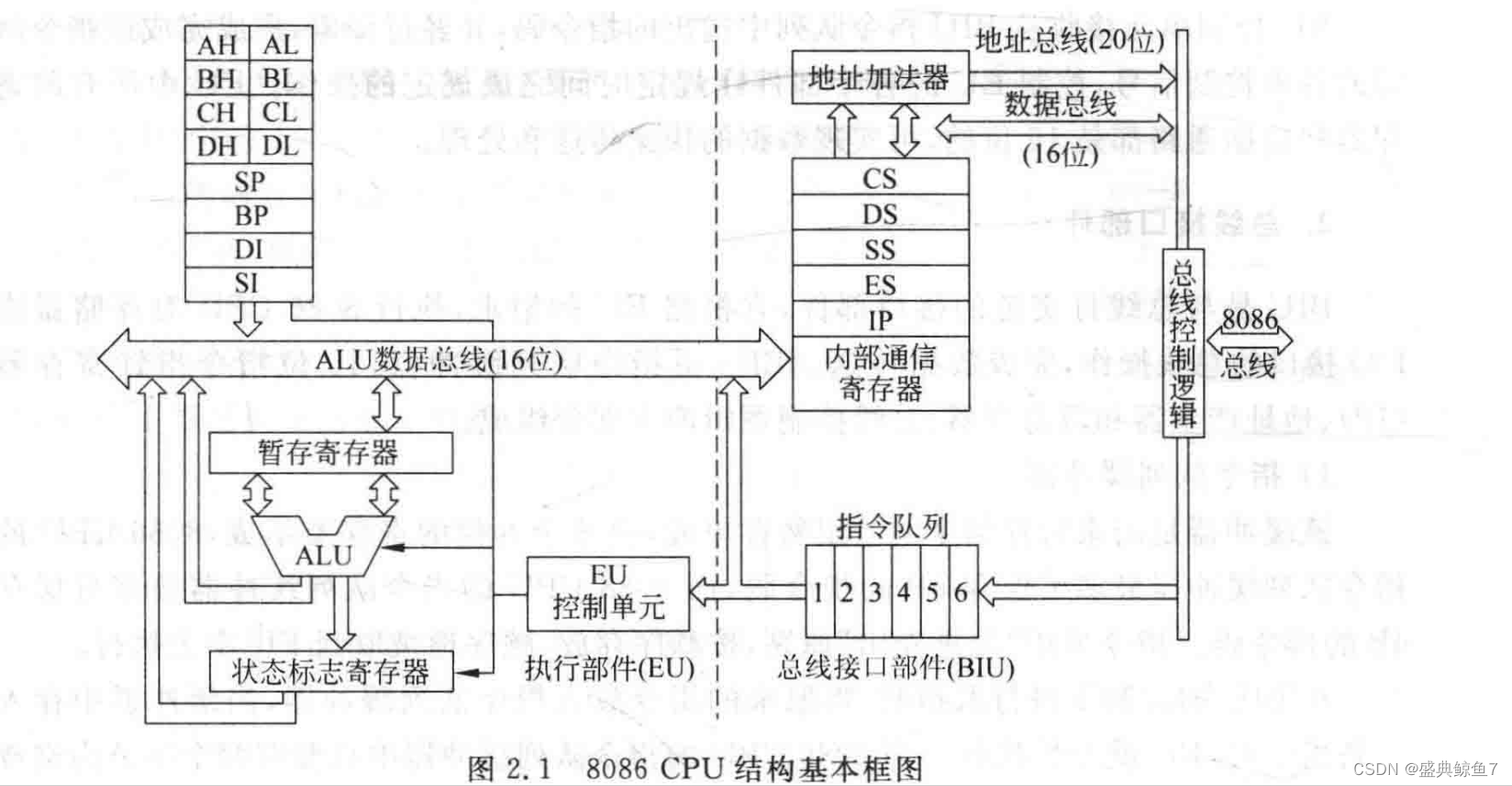

根据最小模式选择8086CPU,8086CPU有20根地址线,16根数据线,寻址空间1MB。根据传输信号的不同,8086CPU的引脚分为三种,即控制引脚(CB),地址引脚(AB),数据引脚(DB)。各个控制引脚的功能:

- RESET:复位信号,高电平有效。当该引脚有效,CPU停止当前工作。

- ALE:地址所存信号,解决数据和地址传送问题。

- M/ I O IO IO:存储器或外设选择信号,为0时选择外设,为1时选择存储器。

- B H E BHE BHE:高八位数据有效。

- D E N DEN DEN:数据选通有效信号。

- DT/ R R R:数据收发控制信号,为0时接受信号,为1时发送信号。

- READY:准备就绪信号,输入,高电平有效。(所有引脚信号均采用标签法)

设置系统地址总线,由于8086有20根地址线,74ls373是一种8位锁存器,一次可以保存8位有效数据。AD0AD16,A16AD19作为输入,第一片接AD0AD7,第二片接AD8AD15,第三片接A16~A19, B H E BHE BHE共21位地址相关信息需要所存。

所以选择3片地址锁存器74ls373。此芯片引脚信号 O E OE OE需要为低电平时允许输出。

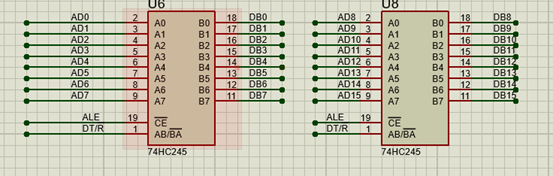

设置系统数据总线,由于8086有16根数据线,74HC245是一种8位数据缓冲寄存器,所以选择2片数据缓冲器74hc245。AD0AD7为输入端,第一片接AD0AD7,第二片接AD8~AD15。此芯片引脚信号 C E CE CE接 D E N DEN DEN控制数据传送信号,,AB/ B A BA BA接DT/ R R R控制数据的接受与发送。

设置三总线结构

二、输入输出系统总线设计

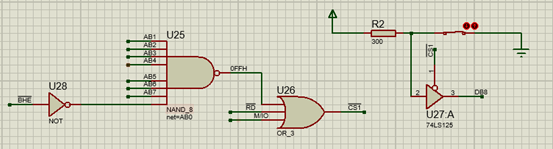

一位输出系统

- 为外设安排地址,定义偶地址(80H)为输出地址。

- 安排一个二极管当写入时,二极管发光。

- 为保存写入的二进制有效,选择74LS74芯片(D触发器)。

- 当 W R WR WR为低电平,地址有效且M/ I O IO IO为低电平时,二极管发光。

一位输入系统 - 为外设安排地址,定义奇地址(81H)为输入地址。

- 设置一个开关电路作为输入。

- 安排一个三态门(将模拟信号传换为数字信号),当 C S CS CS无效时,信号阻断,无法与CPU进行数据传输。

- 当 R D RD RD为低电平,地址有效且M/ I O IO IO为低电平时,才能进行输入。