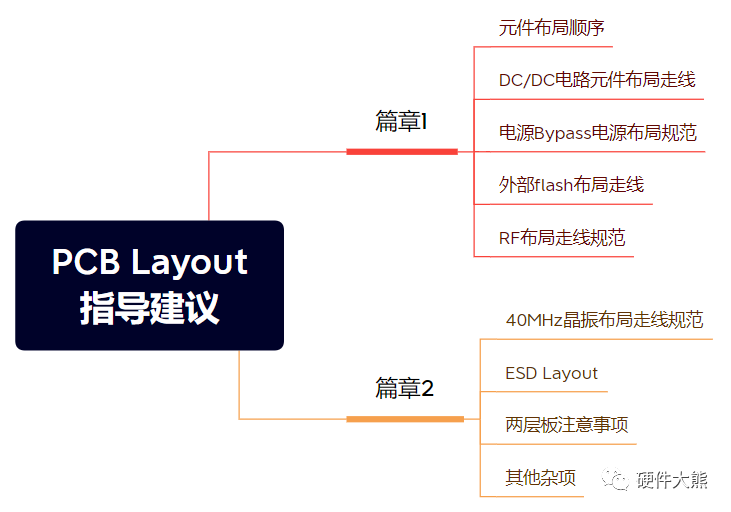

《一款射频芯片的layout设计指导案例-篇章1》中,我们阐述了RTL8762元件布局顺序、DC/DC电路元件布局走线、电源Bypass布局规范、外部flash布局走线、RF布局走线,

本篇阐述晶振、ESD、板层等相关指导建议——

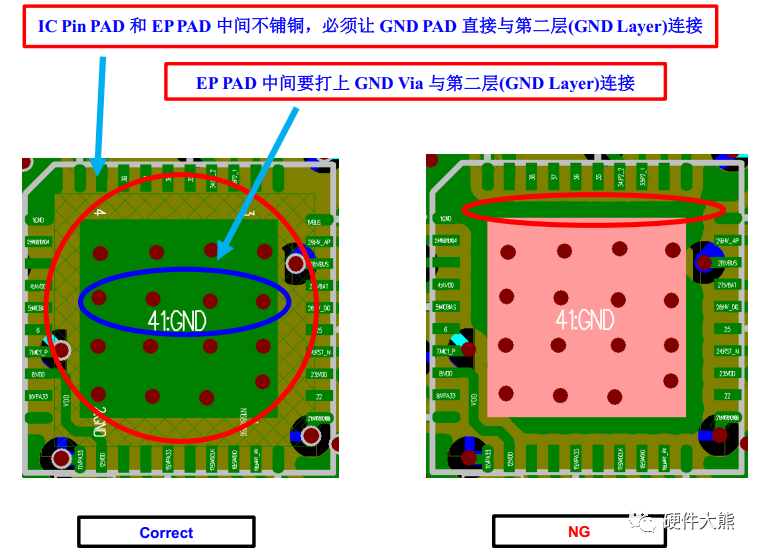

40MHz晶振布局走线规范

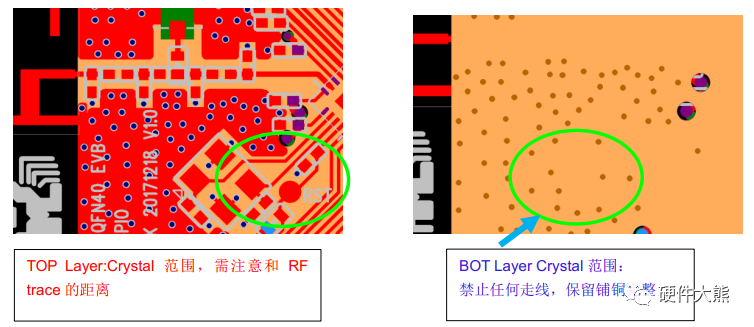

在没有结构限制情况下, Crystal 和 BT CHIP 要放在同一层面。

为了避免干扰 RF 信号, Crystal 尽量远离 RF Trace。

Crystal 的放置应尽可能靠近 BT CHIP,路径要短, Trace 宽度建议超过 6mil。

如果是 2 层板,禁止在 Crystal 的背层走线,让背层(BOT)的铺铜保留完整性。

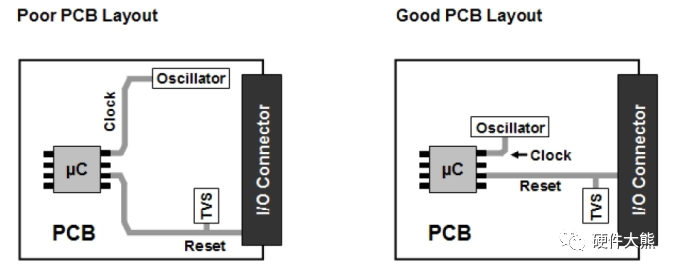

ESD Layout

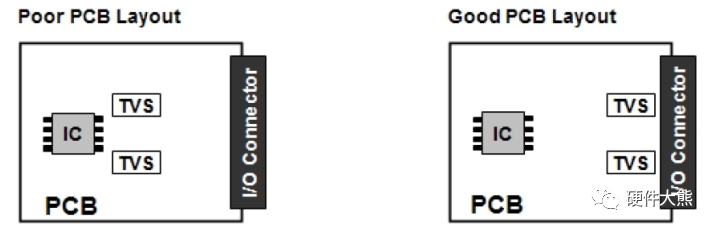

TVS 摆放位置应尽可能靠近 ESD 源头(接头等处),与被保护 IC 的距离要远于 ESD 源。布线时需将 ESD 源直接接到 TVS,减少 TVS 管和回流地之间的寄生电感

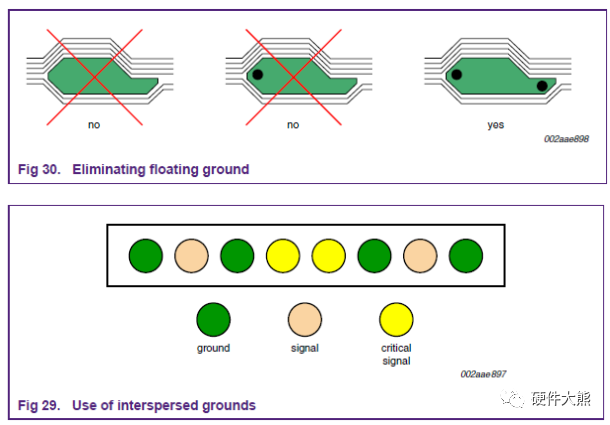

分割地平面时要注意缩短信号线的回流路径, 采用星状线的方式实现并联接地。

删除孤岛铜皮,用地将敏感信号包裹起来,防止其他信号的辐射干扰

尽量缩短线长以减少寄生电感。因直角走线会产生更大的电磁辐射,避免直角走线连接到器件或走线上。高速电路设计时,更需注意这点。

尽量增大过孔的钻孔直径和焊盘直径,减少过孔的寄生电感。

布线时,让敏感信号线远离 PCB 板边。为避免走线与天线间的串扰,走线需远离天线,天线需放在离

接头较远的位置。布局时,将所有的接头和板边接线放在 PCB 板边一侧, ESD 敏感器件放到 PCB 中心。

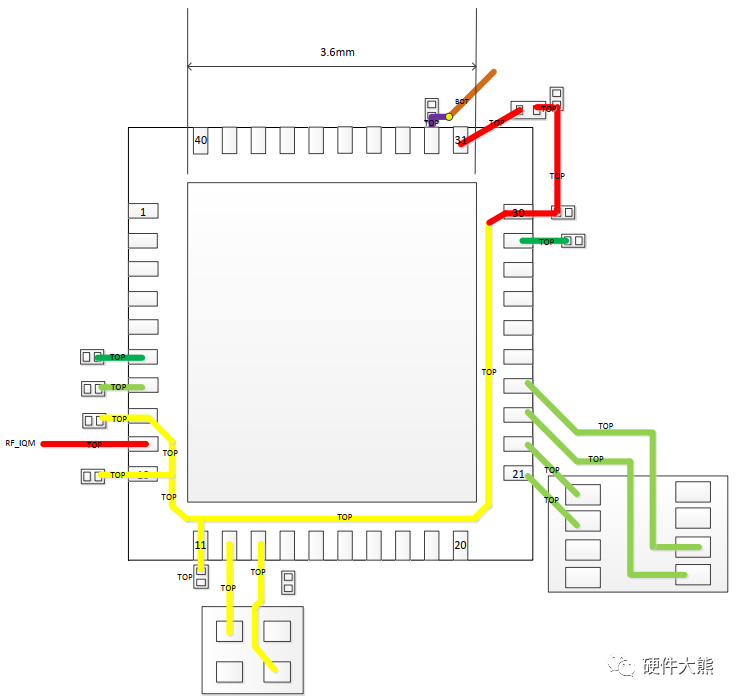

两层板注意事项

BT CHIP、 RF、 Crystal、 Buck 区域,尽量避免于这些区域走线。

两层板走线尽可能走在同一层面。

若走线要贯穿到背层,背面的走线尽可能短或者集中在一起,维持背面敷铜的完整。

电源VDD12 走线可将 EPAD 尺寸改小到 3.6mm, trace 从 IC package 缝隙中穿过。

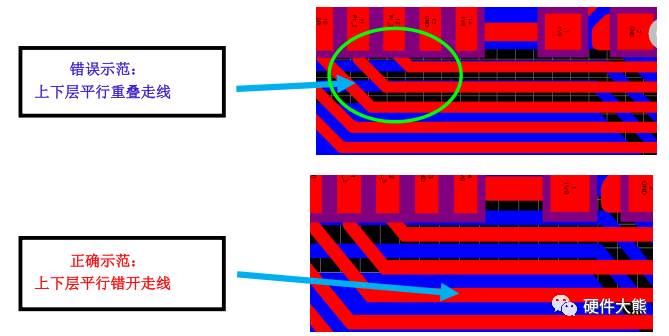

其他注意事项

上下层走线时尽可能不要平行重叠的走线

External flash 必须尽量的靠近 IC 摆放

原创不易,若有转载需求,务必告知!

如果我的文字对你有所启发或帮助,

“点赞\转发”是对我最大的支持

推荐阅读:

一款射频芯片的layout设计指导案例-篇章1

面试题:高速PCB一般布局、布线原则

面试题:高速电路是什么,什么信号算高速?

硬件大熊原创合集(2023/04-05更新)