TMS320C54x(以下简称C54x)系列DSP是一种低功耗、高性能的16位定点芯片它的突出特点是:采用改进型哈佛总线结构,具有性能强大的CPU内核、内部多总线结构、硬件重复机制及两套独立的地址产生器,为组成6级流水线和并行操作提供了硬件平台。

2.1 芯片内部结构及特点

C54xDSP的内部结构主要由C54xCPU内核、片内存储器及片内外围设备(简称片内外设)三大部分组成,如图2-1所示。它的主要组成部分和结构特点如下:

1.多总线的哈佛结构

C54x片内配置了8套16位的地址总线和数据总线,用以实现CPU与片内存储器的数据交换:片内还有一套外设总线,通过6通道的直接存储器访间(DMA)可以实现与片内外设的数据传送。

2.CPU内核

C54xCPU内含一个40位的算术逻辑运算单元(ALU)和两个40位的累加器(ACCA、ACCB),可以进行40位宽数捌范围的算术运算:一个40位的桶形移位器,为进行定点定标操作提供了基础;一个17×17位的硬件乘法器和40位的加法器组成了乘法-累加单元(MAC);一个用于Viterbi算法的比较、选择、存储单元(CSSU):一个支持单周期指令EXP的专用硬件指数编码器,可用来计算40位累加器中数值的冗余指数位,以便进行定点与浮点数据格式的转换等。CPU中还配置了两个地址生成器,包括2个辅助算术运算单元(ARAU0、ARAU1)及8个辅助寄存器(AR0~AR7),为在单周期内进行两次存储器访问提供了硬件支持。

3.片内存储空间

C54x片内集成了ROM和RAM。片内RAM又分为两种类型:双口 DARAM和单口SARAM。其中,双口DARAM在单周期内可进行一次读取和一次写入操作,而单SARAM在单周期内只能进行一次读/写访问。片内ROM和RAM的特点是:既可配置为程序存储器,又可配置为数据存储器;具有与CPU相同的执行速度,可零等待高速运行;造价低,便于使用等)不同的C54x芯片其片内ROM和RAM的容量有所不同。

4.片外可扩展的最大存储空间

5.片内外设

6.灵活的寻址方式及适合于信号处理的指令系统

7.低功耗工作

2.2 C54x的内部多总线结构

总线结构决定了计算机的数据访问能力和并行操作能力。C54×的片内采用了多总线结构,它由8套16位的内部总线组成。

(1)2套程序存储器操作总线:程序地址总线PAB,程序总线PB。

(2)6套数据存储器操作总线:数据地址总线CAB、DAB、EAB,数据数据总线CB、DB、EB。

2.2.1程序存储器操作总线

序总线P优取程序存储器的指令代码和立即数,或者通过数据总线B进行程序的程序地址总线PAB为CPU提供取指令和写指令时所需要的地址,CPU可通过程操作。CPU还可以将存储在程序空间的立即数通过PB传送至乘法-累加单元MAC进行乘且累加操作。在执行数据移动指令MVPD和READA等时,程序存储器的数据会经过PB总线传送至数据存储器。

2.2.2数据存储器操作总线

总线CAB、DAB、EAB及CB、DB、EB与CPU、数据地址产生逻辑、程序地址产生逻辑、片内外设及数据存储器等功能单元相连,负责对数据进行寻址及读/写访问。其中,数据地址总线CAB、DAB、EAB负责传送指令执行时所需要的数据存储器地址,数据数据总线CB、DB、EB负责进行读/写数据的传送。

2.3 C54×的中央处理单元(CPU)

CPU是DSP的核心部件。它负责进行程序流的控制和指令的处理,完成数据的传送,执行算术运算、布尔逻辑及移位操作等。

C54×CPU的结构如图2-2的下半部分所示,它主要包括下列器件:

(1)1个40位的算术逻辑单元,

(2)2个40位的累加器(ACCA、ACCB)。

(3)1个桶形移位器。

(4)1个17位×17位的硬件乘法器与加法器组成的乘法累加单元(MAC)。

(5)1个比较、选择和存储单元(CSSU)(在图2-2中由COMP、TRN和TC等部分组成)。

(6)1个指数编码器(EXP)。

(7)2个16位的状态控制寄存器ST0、ST1和一个16位的处理器模式状态寄存器

PMST(图2-2中没有列出)。

(8)程序地址发生逻辑(PAGEN)和数据地址发生逻辑(DAGEN)。

累加器

C54xCPU内有两个40位的累加器A和B,每个累加器都由三部分组成:低位15~0(AL或BL)、高位31~16(AH或BH)和保护位39~32(AG或BG),如图2-3(a)、(b)所示。AG、BG、AH、BH、AL和BL都是16位的存储器映像寄存器,CPU可以对它们分别进行访问和保存。保护位AG和BG的作用在数值计算中,当出现32位有符号运算溢出时,可以用来保存溢出的结果,由此增大了计算结果的动态范围,提高了定点运算的精度。

CPU的状态和控制寄存器

C54xCPU有3个状态和控制寄存器,分别是状态寄存器ST0、ST1和处理器模式状态寄存器PMST。在ST0和ST1中包含着各种状态和控制标志位,其中,状态位反映了CPU当前的某些处理结果,如进位、溢出等;控制位则是提供给用户用来控制芯片及CPU工作的,如进行符号扩展、允许中断处理等。在PMST中包含有存储器组织和系统工作的控制信息,对它们进行正确的配置,才能保证系统的正常工作。

(1)状态寄存器ST0、ST1

ST0、ST1都是16位的存储器映像寄存器(MMR),其地址分别为0006h和0007h。ST0、ST1各位的定义分别如表2-5及表2-6所示。可通过下列方法对它们进行访问或修改:

(1)用指令SSBX或RSBX对ST0、ST1的某些位置位或清零。

(2)用装载指令LD给ST0、ST1的某些位加载数据。

(3)用存储指令STM等给ST0、ST1加载设定值。

2.4C54x的存储器结构

C54x的存储器空间分为三个独立空间:程序空间、数据空间和I/O空间。存储容量分别为:

(1)程序存储器基本空间64K字,最大可扩展至8M字。

(2)数据存储器空间 64K字。

(2)I/0空间64K字。

2.5复位操作及省电方式

2.5.1复位操作

DSP与其他微处理器一样,需要进行上电复位和人工按键复位。

在C54x处于复位时,DSP将进行以下操作:

(1)处理器模式状态寄存器PMST的位IPTR=1FFb,将中断矢量表的128个字置于程序存储器的FF80h~FFFFh区域。

(2)使程序计数器PC=FF80h,即复位后程序从FF80h开始执行。

(3)将MP/MC引脚上的状态送给PMST的位MP/MC.以决定程序存储空间的配置。

(4)使状态寄存器ST0=1800b,ST1=2900h。

(4)使ST1的位INTM=1,关断所有可屏蔽中断。

(6)使中断标志寄存器IFR=0,清除所有可屏蔽中断的标志。

(7)使控制程序计数器XPC=0,指向程序存储空间的第0页。

(8)使数据总线处于高阻状态。

(9)使控制线处于无效状态。

(10)产生应答信号ACK.(CPV的中断响龙信号输出)

(11)产生同步复位信号,用于初始化片内外设。

2.5.2省电方式

C54x系列DSP提供了多种省电工作方式,主要有下列4种:空闲方式1、空闲方式2、空闲方式3和保持方式,可以通过执行IDLE1、1DLE2、IDL.E3这三条指令使DSP进入相应的空闲方式;或通过控制信号的配置实现保持方式。

2.6中断系统

2.6.1C54x的中断申请源

1.中断的分类

根据C54x中断申请源的不同,可将中断划分为软件中断和硬件中断。

从屏蔽的角度来看,可将中断划分为可屏蔽中断和非屏蔽中断。

2.中断优先级

当有多个硬件中断请求同时出现的时候,CPU将按照其优先级的高低来确定响应次序,先响应优先级高的,然后响应低优先级中断,中断的优先级是由芯片本身确定的,用户不能通过软件来进行修改。在优先级中1级表示最高级。

3.中断矢量表

C54x芯片共有30个中断申请源,中断矢量表的总长度为128个字,每个中断矢量都存放在固定的相对位置,每个中断的中断矢量仅有四个字长。

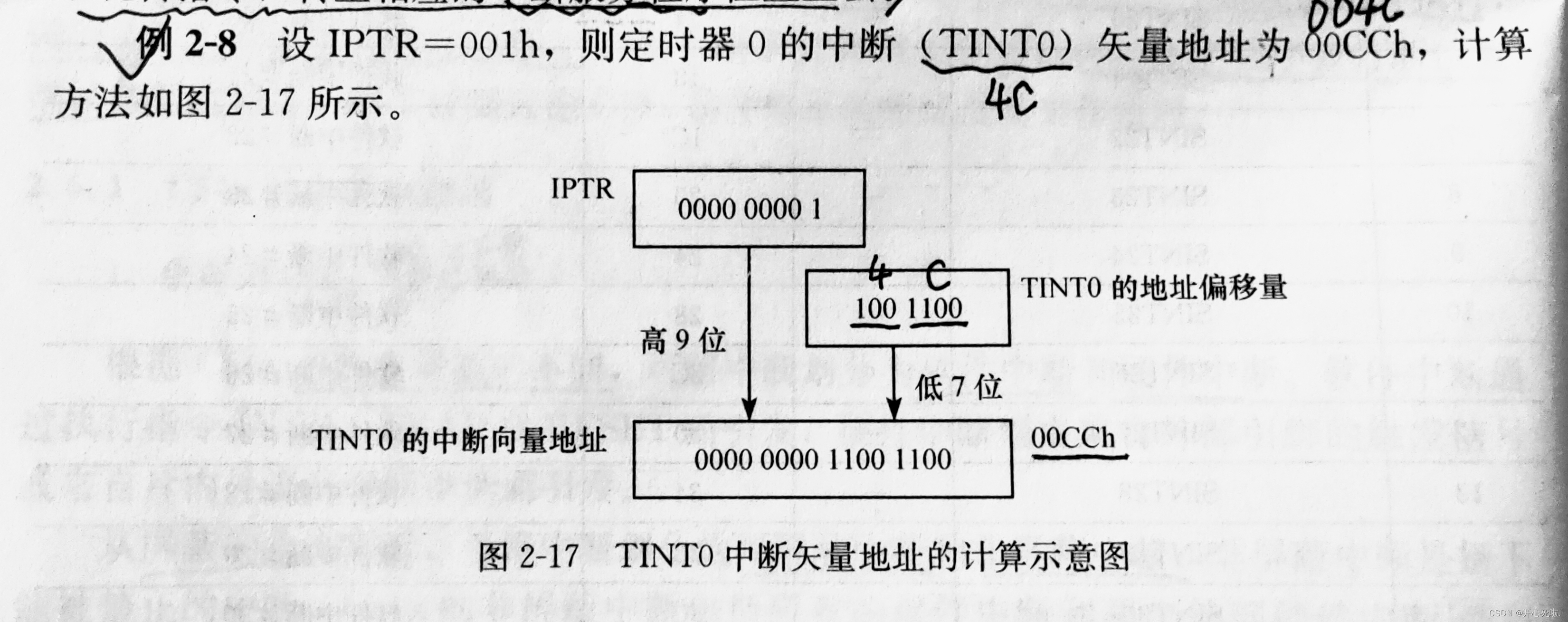

4.中断矢量地址的计算

5.软件中断指令

C54x提供了3条软件中断指令INTR、TRAP和RESET。

(1)指令RESET:可在程序的任何位置使用。执行该指令会引起芯片的软件复位,使DSP返回到一个预定状态开始工作。

(2)指令INTRK:0<K<31:此处的K值即为表2-13中的中断序号。不管ST1中的中断屏蔽位INTM及中断屏蔽寄存器(IER)的状态如何,执行该指令都会强行使CPU跳转至K所指出的中断矢量地址。当INTRK中断被确认时,位INTM被置1,禁止其他可屏蔽中断,但中断标志寄存器IⅡR的相应标志位不会置位,也不能清零该位。

(3)指令TRAPK;0≤K≤31:与INTR指令的操作类似,但是两者有一个重要的区别:INTR会将INTM置1以禁止所有可屏蔽中断,而TRAP指令不影响位INTM。因此,在CPU响应TRAP指令所引发的中断时,可以被其他高优先级的可屏蔽中断打断,使用时应该注意这一点。

2.6.2中断寄存器(R)

C54x有2个寄存器对中断进行管理,分别为中断标志瓷在器正R和中断蔽寄在器IMR。

1.中断标志寄存器(IFR)

当一个中断请求出现时,将把中断标志寄存器IFR中的相应位置1,表示该中断发出了中断申请,并已被挂起,等待CPU的响应。CPU识别该中断并执行相应的中断服务程序会将该标志位清零,通过下列方法可以清除FR中的中断标志:

(1)硬件或软件复位。

(2)响应指令INTRK或TRAPK引发的中断,执行相应的中断服务程序。

(3)响应硬件引发的中断,执行响应的中断服务程序。

(3)向IFR中的位做写入操作。注意:无论向IFR中的某位写入I或0都会清除该位。

2.中断屏蔽寄存器(LMR)

IMR的各位可以看作是可屏蔽中断的分开关,CPU通过对它的设置来选择允许产生中断的中断源。给相应的标志位写入1,允许该中断源产生中断,写入0禁止该中断。而ST1中的INTM位是总开关。在使用时,令INTM=0,使总开关闭合:令相应IMR的某位=1,使分开关闭合,该可屏蔽中断才能得到CPU的响应。注意:INTM位及IMR对于复位中断RS和非屏蔽中断NMI是不起作用的。

2.6.3中断响应及中断处理过程

1.非屏蔽中断或软件中断的处理过程

非屏蔽中断或软件中断的处理过程如图2-19所示。当执行软件中断指令INTR K或TRAP K,或是有非屏蔽中断发生时,CPU将立即响应该中断,进行下列的处理:

(1)产生一个IACK中断应答信号。

(2)将NTM位置1,屏蔽其他可屏蔽中断(TRAPK指令除外)。

(3)保存当前PC值,以便中断结束后返回主程序。

(4)CPU进入相应中断服务程序ISR,执行ISR。

(5)在ISR结束位置有一条返回指令,执行返回指令把返回地址从堆栈中弹给

PC.

(6)CPU继续执行主程序。

2.可屏蔽中断的处理过程

可屏蔽中断的处理过程如图2-20所示。当可屏蔽中断发出请求时,首先设置IFR寄存器的相应标志位,然后由CPU测试下列三个条件是否为真:

(1)INTM=0.

(2)IMR的相应位为1。

(3)当前的中断优先级最高。

如果上述条件都为真,则CPU响应这个中断,进行下列的处理:

(1)INTM位被置1,屏蔽其他可屏蔽中断。

(2)CPU开始对中断矢量表的相应位置寻址。

(3)当取出中断矢量的第一个指令字后,DSP产生一个中断应答信号IACK,并将FR相应位清0。

(4)保存当前PC值。

(5)CPU进人相应中断服务程序1SR,执行1SR,

(6)在ISR结束位置有返回指令,执行返回指令将返回地址从栈中弹给卫C,

(7)CPU继续执行主程序。

2.7流水线

1、C54x的流水线操作

C54x的流水线操作由6个阶段组成,它们是:预取指(P)、取指(F)、译码(D)、寻址(A)、读数(R)执行(X)。

预取指P:CPU将PC的值(指令地址)加载到程序地址总线PAB

取指F:CPU从选中的程序存储单元中取出指令代码并加载到程序数据总线PB

译码D:CPU将PB上的代码送至指令译码器IR进行译码,并产生执行指令所需的控信号

寻址A:如果有对数据存储器的读操作,则在此周期寻址操作数,并修正辅助寄存器或堆栈指针。根据指令的不同,寻址操作数有下列几种操作:①将读单操作数Smem的地址加载到数据地址总线DAB;②将读双操作数Xmem、Ymem的地址加载到数据地址总线DAB、CAB

读数R:根据指令的不同,此阶段有下列儿种操作:①将读出的单操作数Smem加载到数据数据总线DB;②将读出的双操作数Xmem、Ymem加载到数据数据总线DB、CB:③格并行写操作数的地址加载到数据地址总线EAB;④将写单操作数Smem的地址加载到数据地址总线EAB

执行X:CPU完成指令的操作要求。同时将并行写操作数或单操作数Smem加载到数据数据总线EB,写入数据存储器中W

2、流水线冲突

所谓流水线冲突是指:当多个流水线上的指令同时访问DSP的同一资源时所造成的时序上的冲突,或是一条指令需要使用前一条或前几条指令的运行结果,而这个结果还没有产生,此时就会产生逻辑性的错误。

C54x有两类流水线冲突,一类流水线冲突由CPU自行解决,如在双寻址存储器和单寻址存储器的流水线操作中存在的流水线冲突就可以由CPU自动插入空周期来解决,对这类流水线冲突本书不做讨论。还有一类流水线冲突是未加保护的,是C54xCPU不能自动解决的,必须由编程者去设法解决。