CPU :S3C2416 --友善之臂开发板

tRCD --- Active 命令到发出 Read/Write 命令时间间隔

tRP ---Precharge(预充电) 命令到发送 Active 命令时间间隔

tCAS ---Read/Write 命令发出后经过 5tCK=12.5ns 数据才有效

tRAS ---Active 命令到 Precharge 命令时间间隔

tRC两个Active之间的间隔

tREFI ---平均刷新周期间隔

tRFC ----指令刷新时间

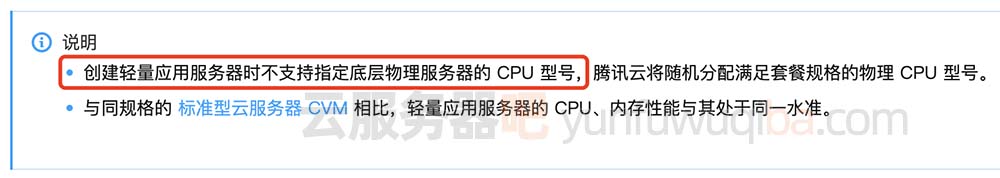

芯片时序图:

;设置DDR0 13位行地址, 10位列地址, DDR2接口, 16位总线

Active命令,打开行及bank地址

; Read命令,在Active后,打开列地址读

; Write命令,在Active后,打开列地址写

LDR R0, =DRAM_BASE

LDR R1, =(2<<17)+(2<<14)+(2<<11)+(2<<8)+(1<<6)+(1<<4)+(1<<1)+(1<<0)

STR R1, [R0, #BANKCFG_OFS]

;// DQS delay 3,Write buffer,Auto pre-charge,bank address 在高位

LDR R1, =(3<<28)+(1<<26)+(1<<8)+(0<<7)+ \

(1<<6)+(0<<5)+(1<<4)

STR R1, [R0, #BANKCON1_OFS]

; s3c2416 ddr2寄存器的clk设置值是相对HCLK的

; RAS [23:20] Row active time 45ns HCLK=133M DDR2=266M 6clock

; Active命令到Precharge命令的最小时间45ns

; ARFC [19:16] Row cycle time tRFC=105ns 14clock

; 指令刷新时间105ns

; CAS Latency [5:4] CAS latency control 12.5ns 2clock

; Read/Write命令发出后经过5tCK=12.5ns数据才有效

; tRCD [3:2] RAS to CAS delay 12.5ns 2clock

; Active命令需经5tCK=12.5ns后才发出Read/Write命令

; tRP [1:0] Row pre-charge time 12.5ns 2clock

; Precharge命令到发送Active命令5tCK=12.5ns

; 故两个Active命令所需的最小时间 tRC=tRAS+tRP=57.5ns

LDR R1, =(5<<20)+(13<<16)+(3<<4)+(1<<2)+(1<<0)

STR R1, [R0, #BANKCON2_OFS]

;// issue an EMRS(extern mode register) command to EMR(2)

LDR R1, [R0, #BANKCON3_OFS]

LDR R2, =0xFFFF0000

BIC R1, R1, R2

ORR R1, R1, #(2<<30)

STR R1, [R0, #BANKCON3_OFS]

LDR R1, [R0, #BANKCON1_OFS]

ORR R1, R1, #0x03

STR R1, [R0, #BANKCON1_OFS]

;// issue an EMRS(extern mode register) command to EMR(3)

LDR R1, [R0, #BANKCON3_OFS]

LDR R2, =0xFFFF0000

BIC R1, R1, R2

ORR R1, R1, #(3<<30)

STR R1, [R0, #BANKCON3_OFS]

LDR R1, [R0, #BANKCON1_OFS]

ORR R1, R1, #0x03

STR R1, [R0, #BANKCON1_OFS]

;// issue an EMRS to enable DLL and RDQS, nDQS, ODT disable

LDR R1, =0xFFFF0000

LDR R2, [R0, #BANKCON3_OFS]

BIC R2, R2, R1

LDR R1, =(0x1<<30)+(0<<27)+(1<<26)+ \

(0<<23)+(0<<16)

ORR R1, R1, R2

STR R1, [R0, #BANKCON3_OFS]

LDR R1, [R0, #BANKCON1_OFS]

ORR R1, R1, #0x03

STR R1, [R0, #BANKCON1_OFS]

;// issue a mode register set command for DLL reset

LDR R1, =0x0000FFFF

LDR R2, [R0, #BANKCON3_OFS]

BIC R2, R2, R1

LDR R1, =(1<<8)+(0<<7)+(3<<4)

ORR R1, R1, R2

STR R1, [R0, #BANKCON3_OFS]

LDR R1, [R0, #BANKCON1_OFS]

BIC R1, R1, #0x03

ORR R1, R1, #0x02

STR R1, [R0, #BANKCON1_OFS]

;// Issue a PALL(pre-charge all) command

LDR R1, [R0, #BANKCON1_OFS]

BIC R1, R1, #0x03

ORR R1, R1, #0x01

STR R1, [R0, #BANKCON1_OFS]

;// Issue 2 or more auto-refresh commands

LDR R1, =0x20

STR R1, [R0, #REFRESH_OFS]

;// Issue a MRS command with LOW to A8 to initialize device operation

LDR R1, =0x0000FFFF

LDR R2, [R0, #BANKCON3_OFS]

BIC R2, R2, R1

LDR R1, =(0<<8)+(0<<7)+(3<<4)

ORR R1, R1, R2

STR R1, [R0, #BANKCON3_OFS]

LDR R1, [R0, #BANKCON1_OFS]

BIC R1, R1, #0x03

ORR R1, R1, #0x02

STR R1, [R0, #BANKCON1_OFS]

;// Wait 200 clock, execute OCD Calibration

LDR R1, =200

0 SUBS R1, R1, #1

BNE %B0

;// Issue a EMRS1 command to over OCD Mode Calibration

LDR R1, =0xFFFF0000

LDR R2, [R0, #BANKCON3_OFS]

BIC R2, R2, R1

LDR R1, =(0x1<<30)+(0<<27)+(1<<26)+ \

(0<<23)+(0<<19)+(0<<22)+(0<<18)+ \

(0x0<<17)+(0<<16)

ORR R1, R1, R2

STR R1, [R0, #BANKCON3_OFS]

LDR R1, [R0, #BANKCON1_OFS]

ORR R1, R1, #0x03

STR R1, [R0, #BANKCON1_OFS]

;// Refresh period is 7.8us, HCLK=133M, REFCYC=1037

LDR R1, =1037

STR R1, [R0, #REFRESH_OFS]

;// issue a Normal mode

LDR R1, [R0, #BANKCON1_OFS]

BIC R1, R1, #0x03

STR R1, [R0, #BANKCON1_OFS]

----------------------------------------------------------------------------------------------------------------------------------------------

对于不同的 DDR2,主要是配置第一步 BANKCFG & BANKCON1, 2,其它初始化流程

可以通用。 BANKCFG 主要是用来配置外扩 DDR2 的行地址线,列地址线以及接口位宽等。

BANKCON1 用来配置 DDR2 控制器一些控制属性,如自动预充,功耗控制,写缓存等。

BANKCON2 用来配置 DDR2 的时序参数,如果时序参数设置得过快,将无法初始化相应

的 DDR2,参数设置得过慢,将造成 DDR2 读写性能低。因此,需要对照相应的 DDR2 芯

片数据手册时序参数来作设置,