目录

- 位扩展

- 定义

- 字扩展

- 定义

- 1、线选法

- 定义

- 优点

- 缺点

- 2、部分译码法

- 定义

- 3、全译码法

- 定义

- 优点

- 缺点

- ⭐⭐⭐字位扩展

- 定义

- 问题

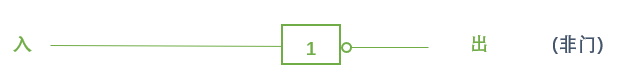

位扩展

定义

当存储芯片的存储字的数量 满足需要,而存储字长(存储单元的位数)不满足需要时,就需要增加存储字长,即进行位扩展。

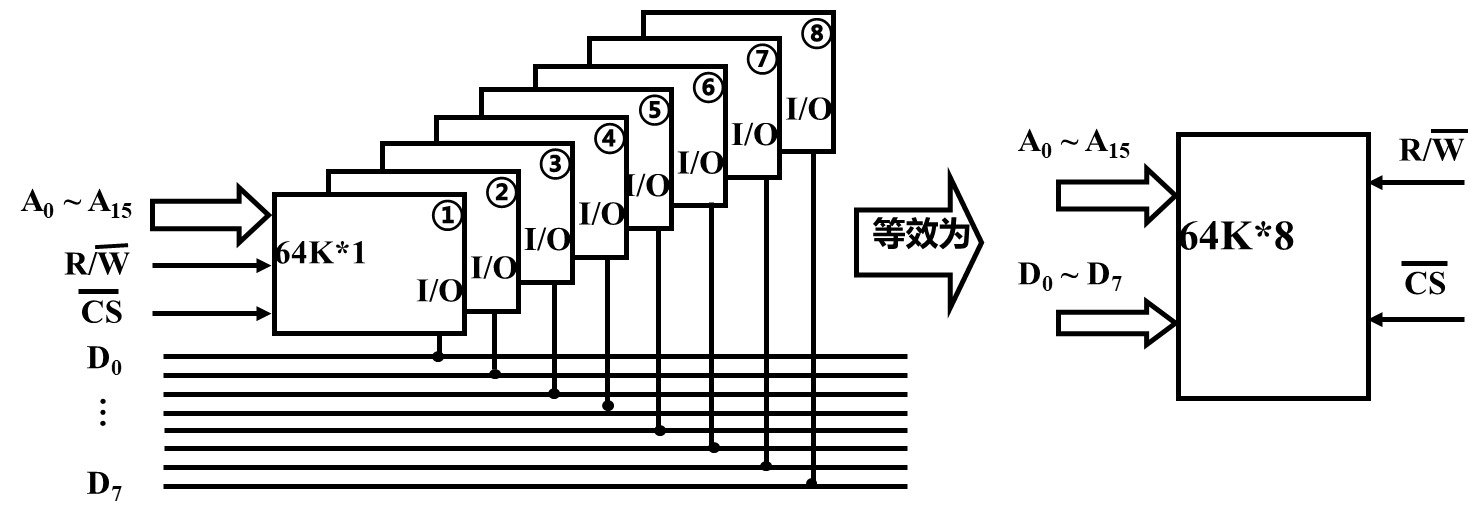

如果采用Inter 2164 芯片,因该芯片为64K×1b芯片,必须由8片才能构成64KB的内存。

字扩展

定义

当存储芯片的存储字长(存储单元的位数)满足需要,而存储字的数量不满足需要时,就需要增加存储字的数量,即进行字扩展。

在存储器系统中,实现片选控制的方法有三种,即①线选法②部分译码法③全译码法

1、线选法

定义

线选法是指利用地址总线的高位地址线直接作为存储器芯片的片选信号,低位地址线和存储器地址相连。采用线选法需保证每次寻址时只能有一个片选信号有效。

优点

结构简单

缺点

地址空间浪费大。由于部分地址线未参与译码,会出现大量地址重叠。(一般高位有剩余)

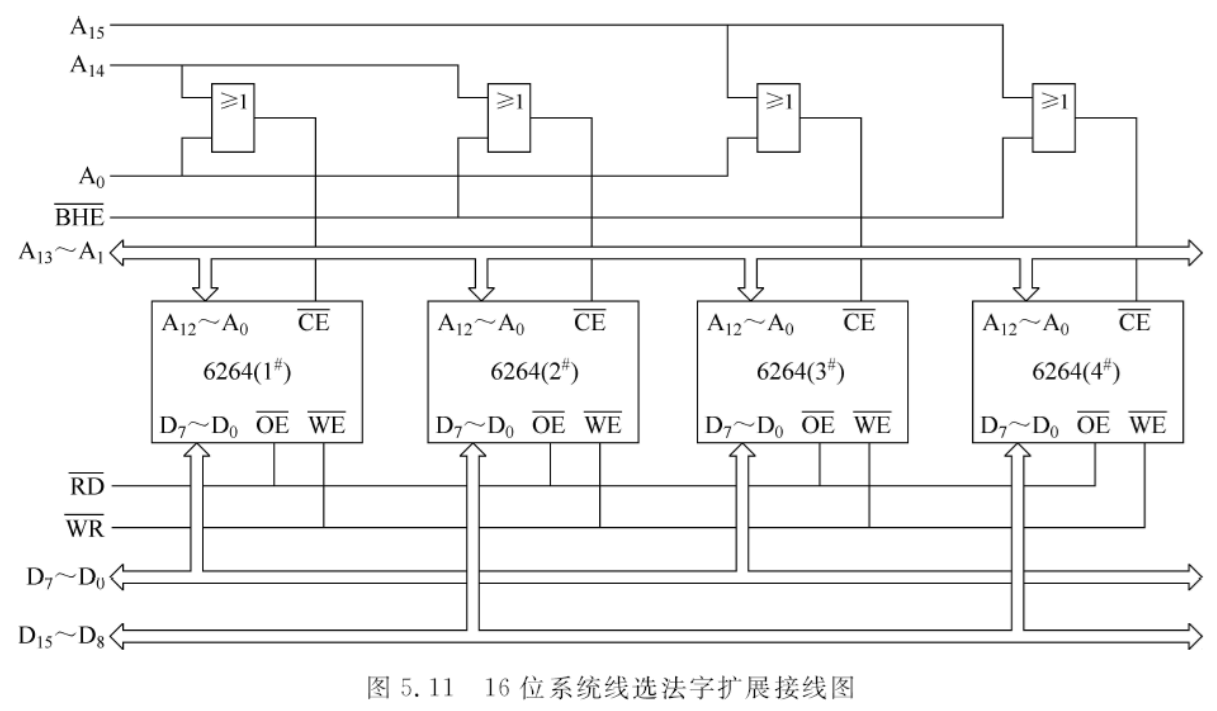

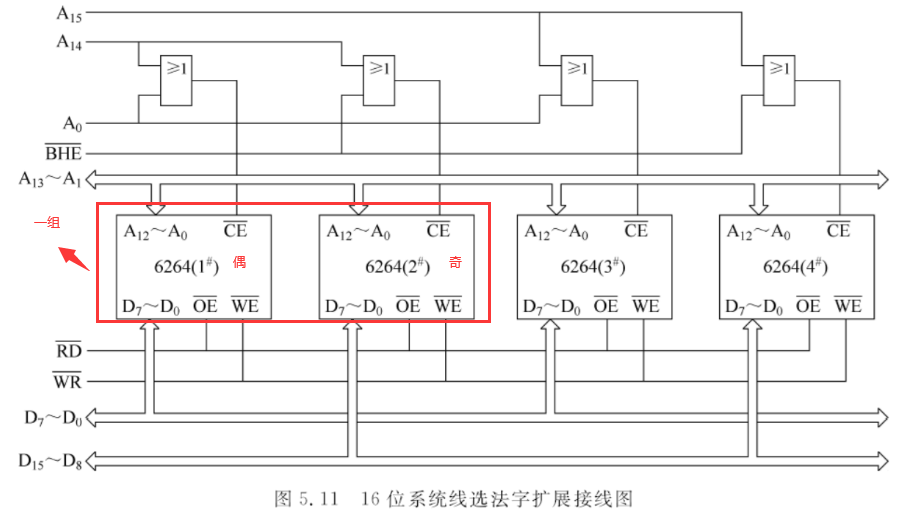

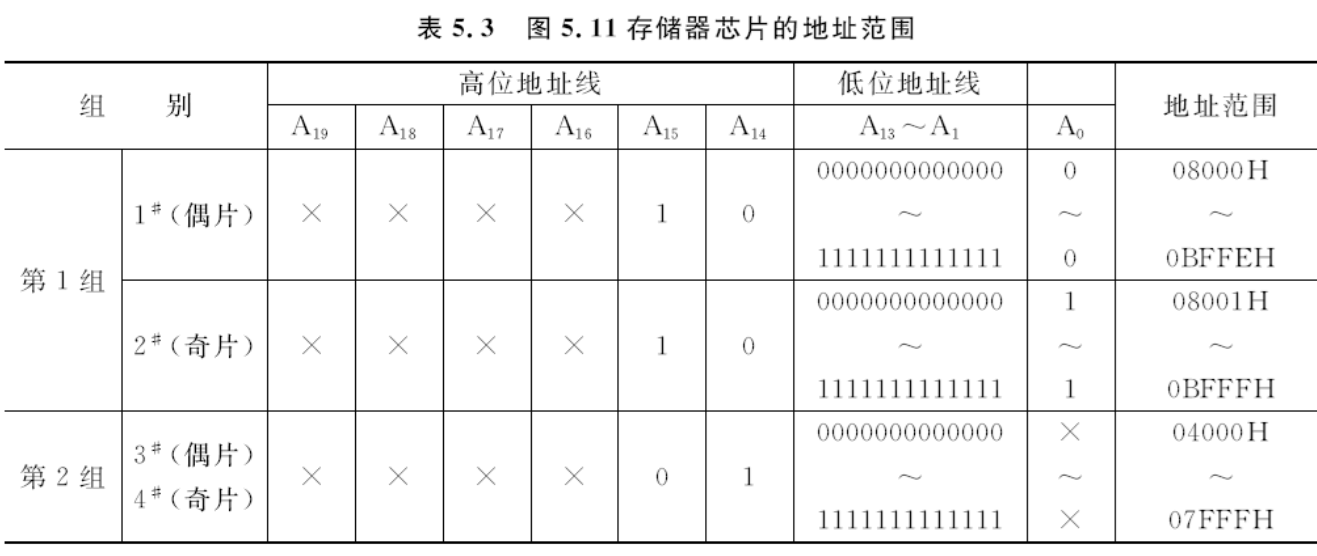

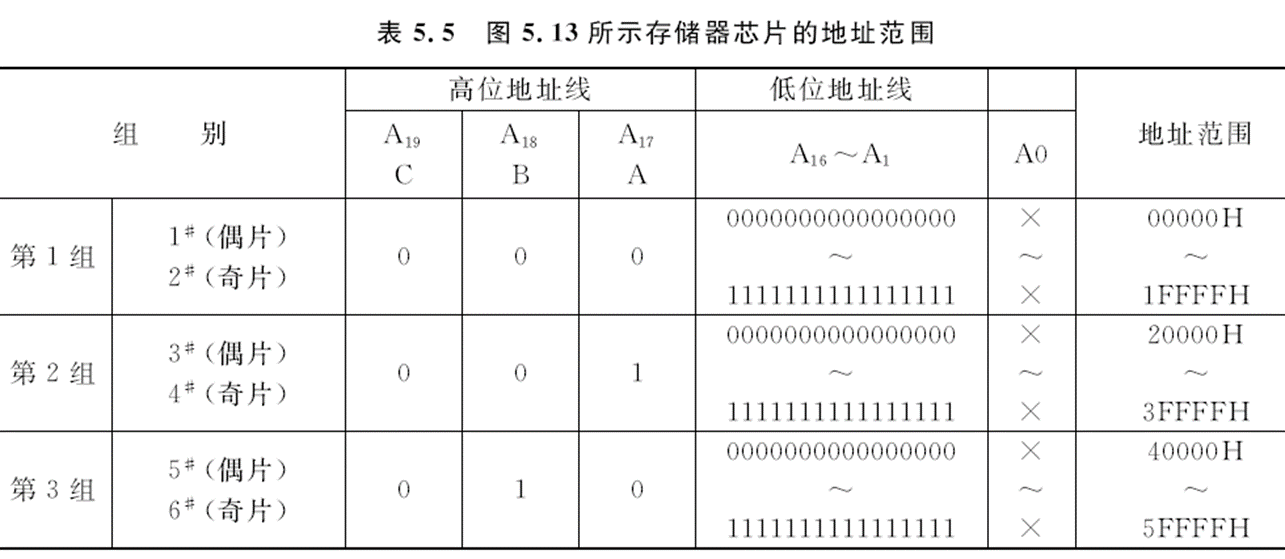

例如:4片6264芯片(8K×8位,SRAM),分为两组,奇片和偶片。

由图可知:D7 ~ D0和D15 ~ D8数据线16条⟶16位CPU,所以分奇偶存储体。

奇片:用 B H E ‾ \overline{BHE} BHE作为片选,8位数据线D7 ~ D0连接到8086数据总线D15 ~ D8上。

偶片:用A0作为片选,8位数据线D7 ~ D0连接到8086数据总线D7 ~ D0上。

6264芯片地址线13条A12 ~ A0连接到8086数据总线A13 ~ A1上。

根据线选法产生片选原则选择高位地址中的A14和A15作为2组存储器芯片的片选。

解答:

第1组中1#芯片(偶片)的片选是A14=0和A0=0同时成立

第1组中2#芯片(奇片)的片选是A14=0和 B H E ‾ \overline{BHE} BHE=0同时成立

A19 ~ A16因未参与对2组芯片的片选控制,故其值可以是0或1(用X表示任取)

考虑到2组芯片不能被同时选中,所以地址不允许出现A15A14=00的情况。

A19 ~ A0为:

XXXX 1000 0000 0000~XXXX 1011 1111 1111

2、部分译码法

定义

部分译码是将高位地址线中的部分地址进行译码,产生存储器的片选信号。

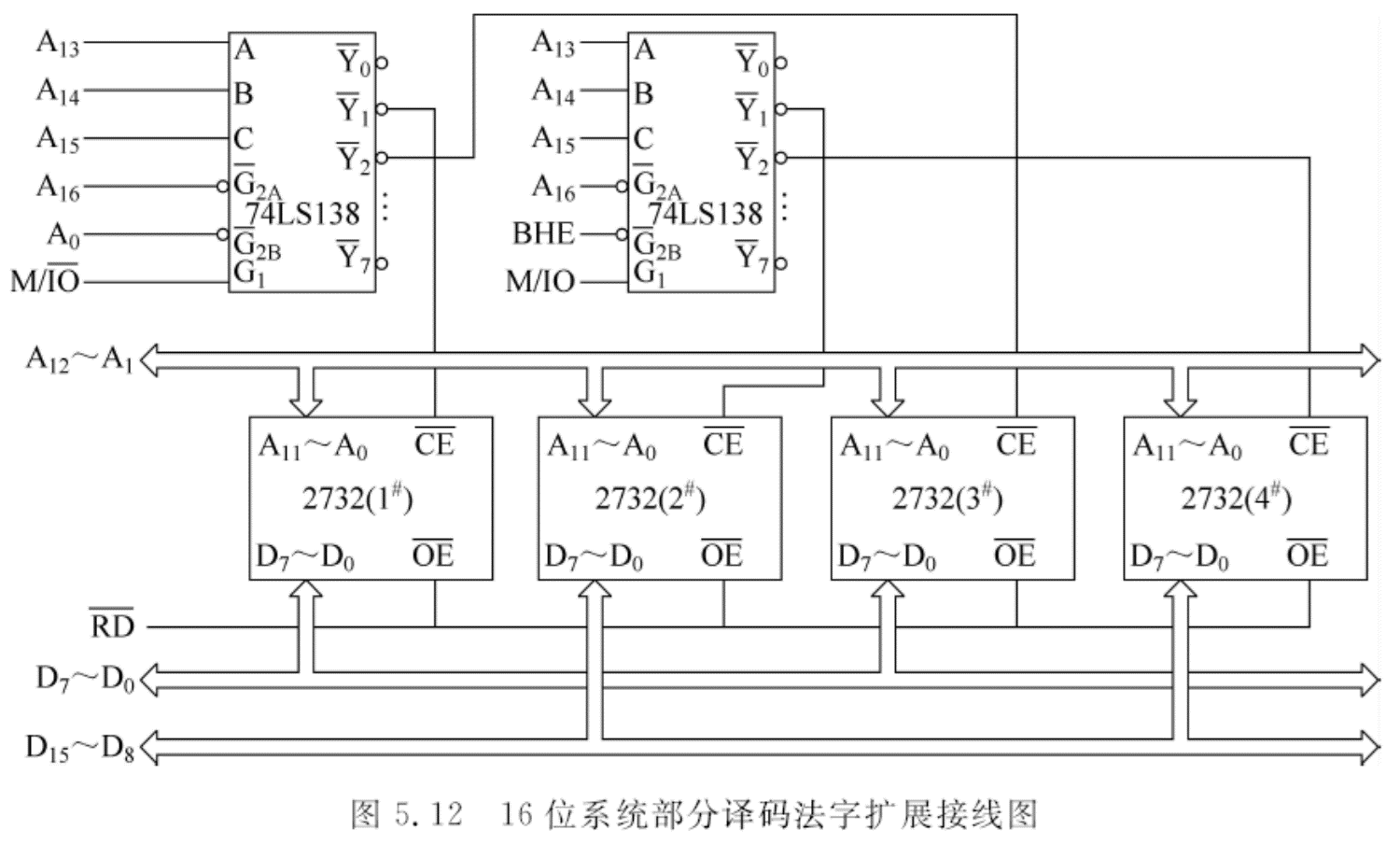

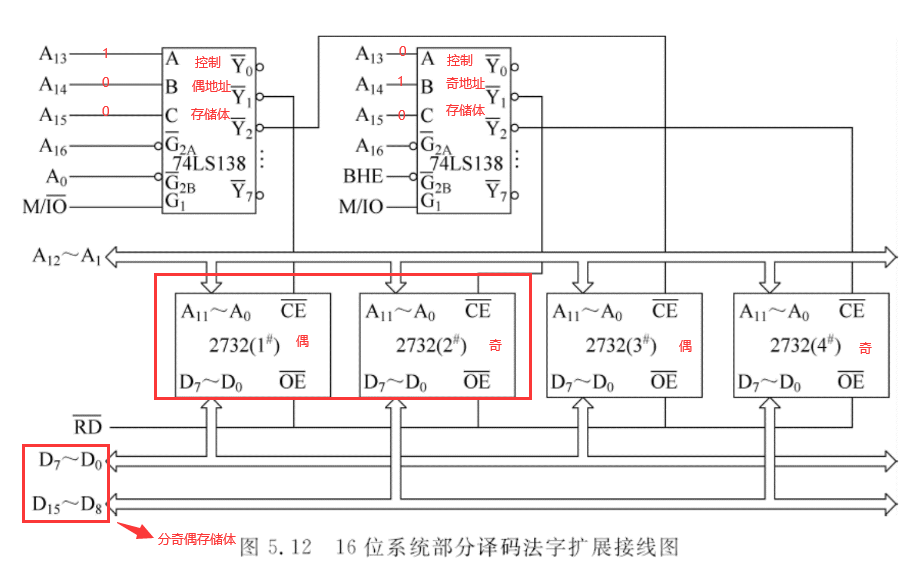

例题:采用部分译码法用4片2732芯片(4K×8位,EPROM)组成的16位存储器系统。

4片2732芯片分为两组,每组2片(奇片和偶片)。

2732芯片地址线12条A11 ~ A0连接到8086地址总线A12 ~ A1上。

部分译码法采用高位地址的部分A16、A15、A14、A13 经两片74LS138进行译码。

74LS138的 G ‾ \overline{G} G2B使能端一个接A0、一个接 B H E ‾ \overline{BHE} BHE。

部分译码时,未使用高位地址线A19、A18、A17也就是说,这3位无论是什么,对芯片寻址都没有影响。所以,每个芯片将同时具有23=8个可用且不同的地址范围(即重叠区)。

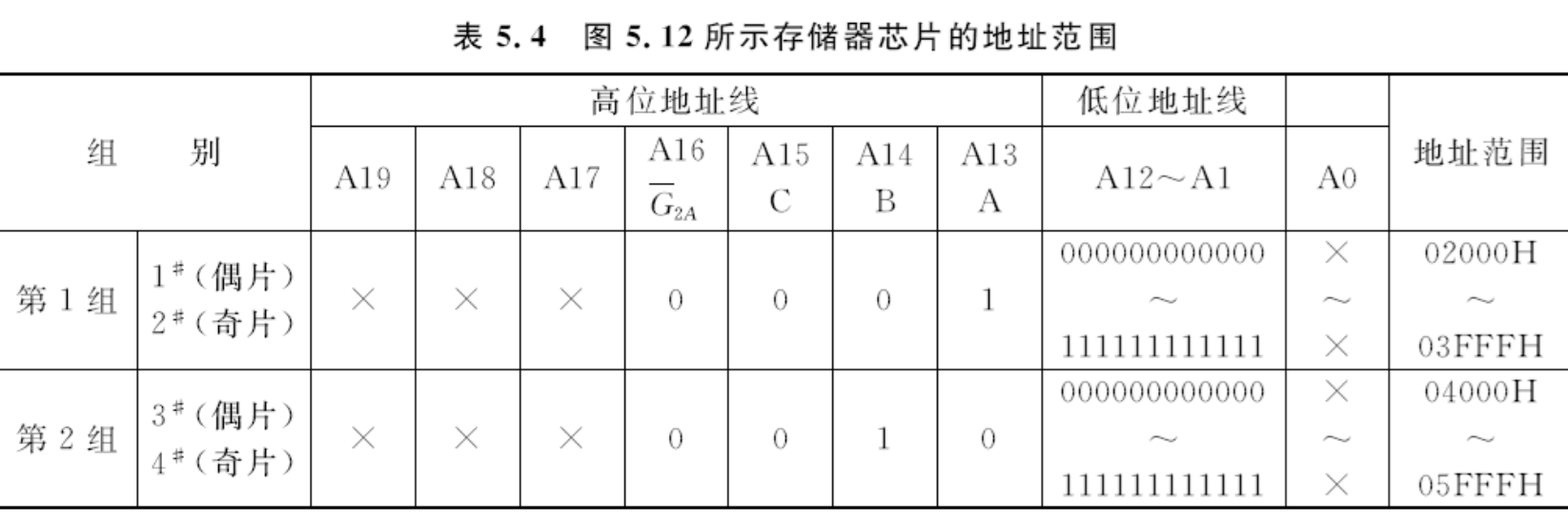

3、全译码法

定义

全译码法:是指将地址总线中除片地址以外的全部剩余高位地址参加译码,产生各存储芯片的片选信号。

优点

每个存储单元的地址都是唯一的,不存在地址重叠

缺点

译码电路较复杂,连线也较多

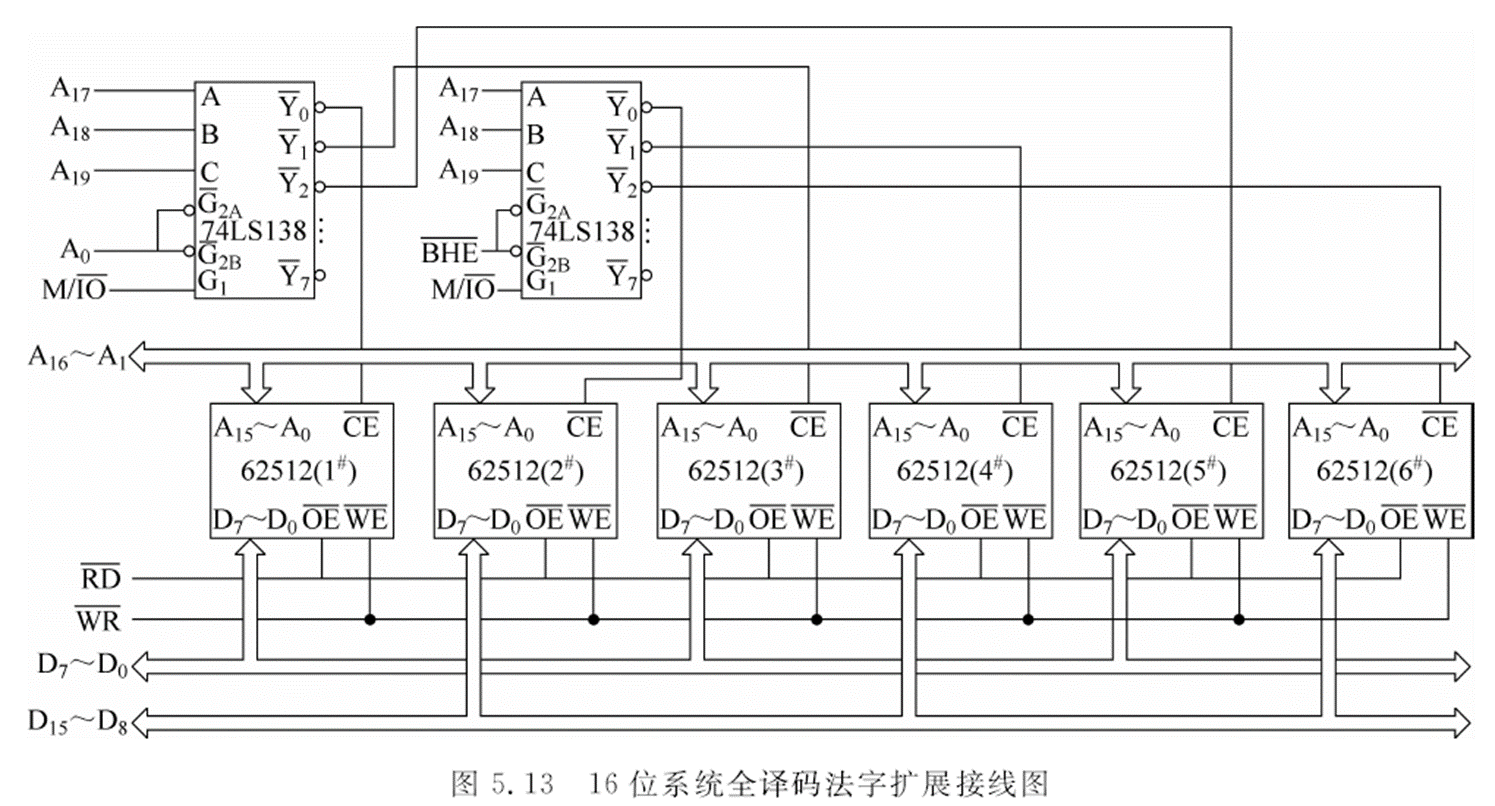

例题:采用全译码法用6片62512芯片(64K×8位,SRAM)组成的16位存储器系统。

6片62512芯片分为3组,每组2片(奇片和偶片)。

62512芯片地址线16条A15 ~ A0连接到8086地址总线A16 ~ A1上。

8086的高位地址是A19~A17,全部经两片74LS138进行译码。A0、 B H E ‾ \overline{BHE} BHE分别接两片74LS138的使能端。

⭐⭐⭐字位扩展

定义

当存储芯片的 存储字长 (存储单元的位数)和 存储字的数量 都不满足需要时,则字和位 都需要进行扩展,即进行字位扩展。

字位扩展是字扩展和位扩展的组合。

字位全扩展时,先把存储器芯片分组,然后可以采取:

①组内位扩展、组间字扩展。(最优)

②组内字扩展、组间位扩展。

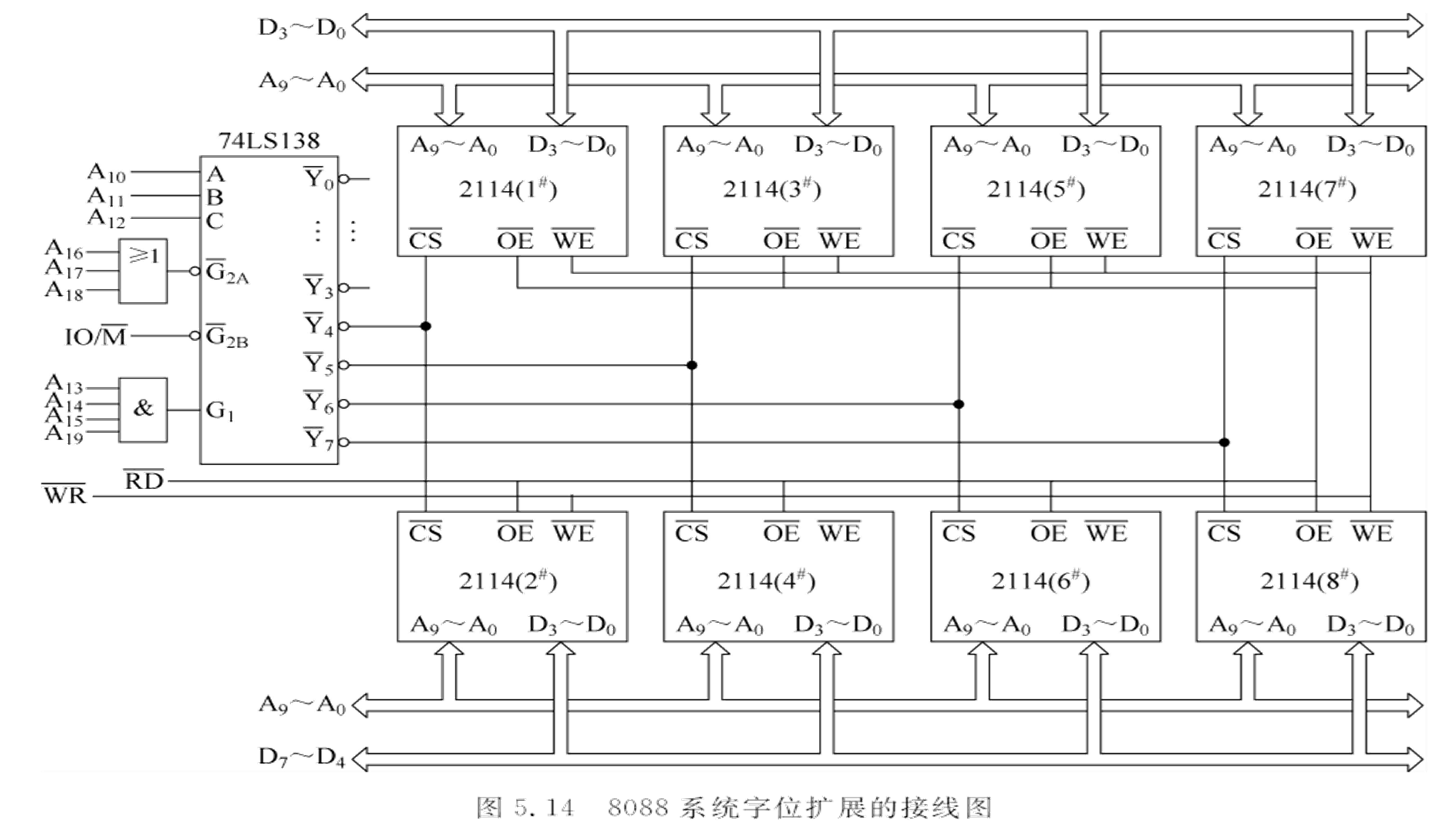

例题:某8088微机系统,要求使用2114芯片(1K×4b)若干,扩展(4K×8b)存储器模块。

解答:

2114所需芯片数=(4K×8b)/(1K×4b)=8片。

组内位扩展:8b/4b=2,(故2114芯片每2片一组)

组间字扩展:4K/1K=4,(故2114芯片分为4组)

组成4组按字节存取的1KB容量的存储器。

由图可知:D7 ~ D4和D3 ~ D0数据线8条⟶8位CPU,所以不分奇偶存储体。

芯片的D7 ~ D4和D3 ~ D0的数据线分别与CPU数据总线的D7 ~ D4和D3 ~ D0相连,地址线、控制线并联。

组件字扩展:4组存储器的地址线A9 ~ A0和D7 ~ D0并联后分别连接到8088总线的低位地址A9 ~ A0和数据线D7 ~ D0上。

因为8088的地址线为20位,且剩余A19 ~ A10。

高位地址线A19 ~ A10全译码后为4组存储器组提供片选信号,全译码用一片74LS138和逻辑门实现。

Y ‾ \overline{Y} Y4、 Y ‾ \overline{Y} Y5、 Y ‾ \overline{Y} Y6、 Y ‾ \overline{Y} Y7、 分别作为4组存储器的片选 C S ‾ \overline{CS} CS。

看A10、A11、A12:(第一组)连接的是 Y ‾ \overline{Y} Y4

∴A10、A11、A12为001

看A10、A11、A12:(第二组)连接的是 Y ‾ \overline{Y} Y5

∴A10、A11、A12为101

看A10、A11、A12:(第三组)连接的是 Y ‾ \overline{Y} Y6

∴A10、A11、A12为011

看A10、A11、A12:(第四组)连接的是 Y ‾ \overline{Y} Y7

∴A10、A11、A12为111

看A13、A14、A15、A19:(经过与门连接G1,要想有效则经过与门后为高电平) ∴A13、A14、A15、A19为1111

看A16、A17、A18:(经过或门连接 G ‾ \overline{G} G2A,要想有效则经过或门后为低电平)

∴A16、A17、A18为000

综上所述:

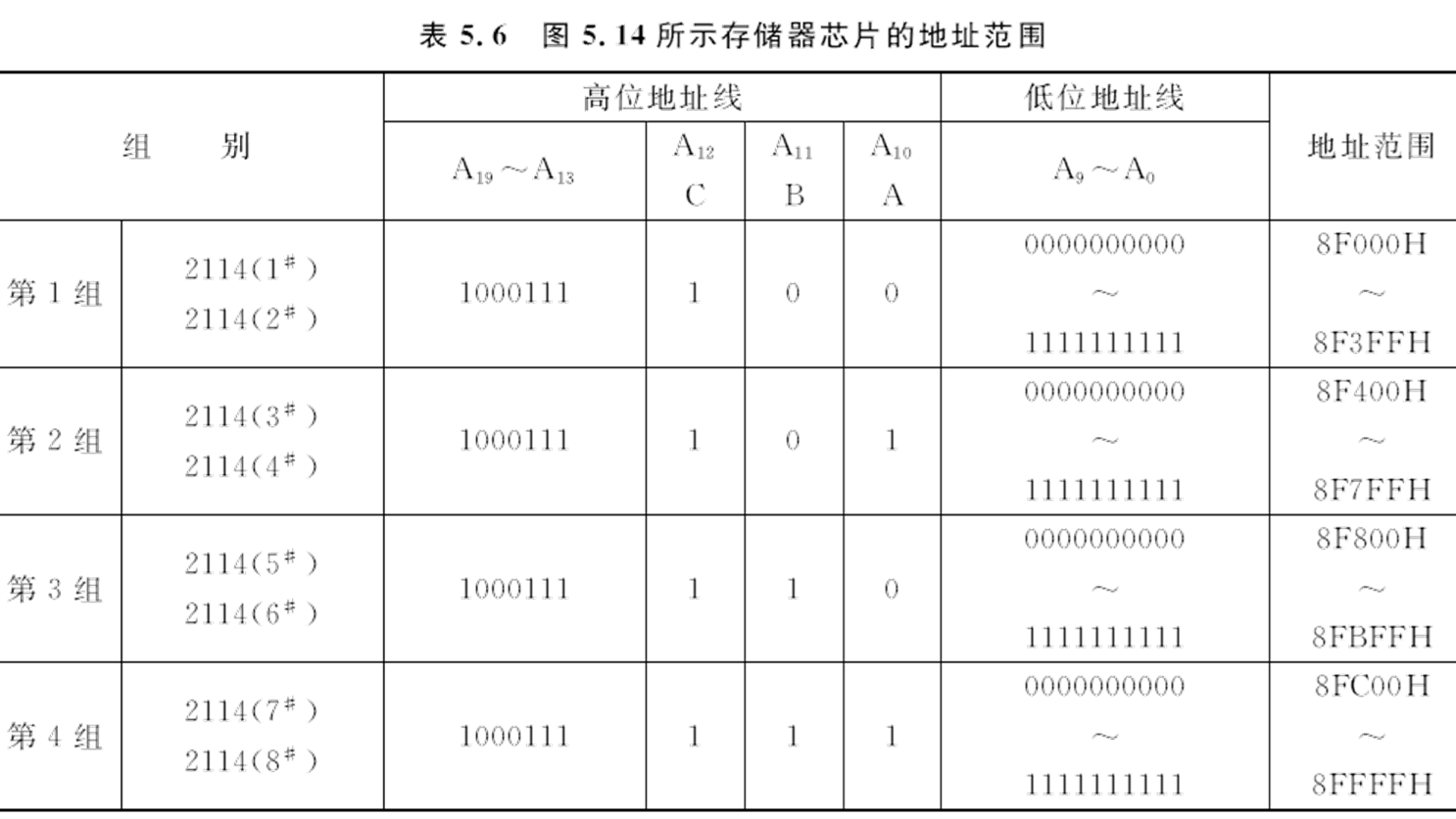

(第一组)A19 ~ A0为

1000 1111 0000 0000 0000 ~1000 1111 0011 1111 1111

∴8F000H~8F3FFH

(第二组)A19 ~ A0为

1000 11110100 0000 0000 ~1000 11110111 1111 1111

∴8F400H~8F7FFH

(第三组)A19 ~ A0为

1000 11111000 0000 0000 ~1000 1111 1011 1111 1111

∴8F800H~8FFBFH

(第四组)A19 ~ A0为

1000 1111 1100 0000 0000 ~1000 1111 1111 1111 1111

∴8FC00H~8FFFFH

问题

①该系统的存储容量为多少?

4KB(4K×8b)

②采用了什么译码方式?

全译码法

③系统扩展方法为?

字位扩展

④每组存储器的地址为?

第一组:8F000H~8F3FFH

第二组:8F400H~8F7FFH

第三组:8F800H~8FFBFH

第四组:8FC00H~8FFFFH